IIC - 【转载】对I2C总线的时钟同步和总线仲裁的深入理解

对I2C总线的时钟同步和总线仲裁的深入理解

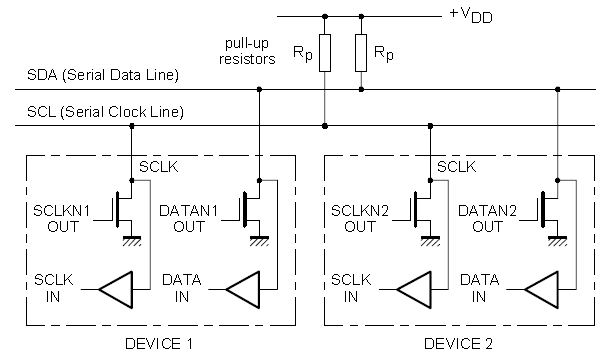

每一个IIC总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管、输入缓冲为一只高输入阻抗的同相器[1]。这种电路具有两个特点:

①由于SDA、SCL为漏极开路结构,借助于外部的上拉电阻实现了信号的“线与”逻辑;

②引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致。为 “时钟同步”和“总线仲裁”提供硬件基础。

I2C总线接口内部结构

IIC设备对总线的操作仅有“把线路接地”——输出逻辑0。基于IIC总线的设计,线路上不可能出现电平冲突现象。如果一设备发送逻辑0,其他发送逻辑1,那么线路看到的只有逻辑0。也就是说,如果出现电平冲突,发送逻辑0的始终是“赢家”。总线的物理接法允许主设备往总线写数据的同事读取数据。这样两主设备争总线的时候“赢家”并不知道竞争的发生,只有“输家”发现了冲突——当写一个逻辑1,却读到了0——而退出竞争。

时钟同步

如果被控器希望主控器降低传送速度可以通过将SCL主动拉低延长其低电平时间的方法来通知主控器,当主控器在准备下一次传送发现SCL的电平被拉低时就进行等待,直至被控器完成操作并释放SCL线的控制控制权。这样以来,主控器实际上受到被控器的时钟同步控制。可见SCL线上的低电平是由时钟低电平最长的器件决定;高电平的时间由高电平时间最短的器件决定。这就是时钟同步,它解决了I2C总线的速度同步。

总线仲裁

假设主控器1要发送的数据DATA1为“101 ……”;主控器2要发送的数据DATA2为“1001 ……”总线被启动后两个主控器在每发送一个数据位时都要对自己的输出电平进行检测,只要检测的电平与自己发出的电平一致,他们就会继续占用总线。在这种情况下总线还是得不到仲裁。当主控器1发送第3位数据“1”时(主控器2发送“0” ),由于“线与”的结果SDA上的电平为“0”,这样当主控器1检测自己的输出电平时,就会测到一个与自身不相符的“0”电平。这时主控器1只好放弃对总线的控制权;因此主控器2就成为总线的唯一主宰者。 不难看出:

- ① 对于整个仲裁过程主控器1和主控器2都不会丢失数据;

- ② 各个主控器没有对总线实施控制的优先级别;

- ③总线控制随即而定,他们遵循“低电平优先”的原则,即谁先发送低电平谁就会掌握对总线的控制权。

根据上面的描述,“时钟同步”与“总线仲裁”可以总结如下规律:

- ①主控器通过检测SCL上的电平来调节与从器件的速度同步问题——时钟同步;

- ②主控器通过检测SDA上自身发送的电平来判断是否发生总线“冲突”——总线仲裁。因此,I2C总线的“时钟同步”与“总线仲裁”是靠器件自身接口的特殊结构得以实现的。

[1]同相器:当输入高电平时输出也是高电平,输入低电平时输出也是低电平。主要要于需要缓冲的场合,就是只要输入很小的电流,可输出较大的电流,增加带载能力。

【转载】http://blog.csdn.net/ce123_zhouwei/article/details/6877494

IIC - 【转载】对I2C总线的时钟同步和总线仲裁的深入理解的更多相关文章

- I2C总线的仲裁机制

在多主的通信系统中.总线上有多个节点,它们都有自己的寻址地址,可以作为从节点被别的节点访问,同时它们都可以作为主节点向其他的节点发送控制字节和传 送数据.但是如果有两个或两个以上的节点都向总线上发送启 ...

- I2C总线完全版——I2C总线的结构、工作时序与模拟编程

I2C总线的结构.工作时序与模拟编程 I2C总线的结构.工作时序与模拟编程I2C总线(Inter Integrated Circuit)是飞利浦公司于上个世纪80年代开发的一种"电路板级&q ...

- [I2C].I2C总线详解

转自:https://www.cnblogs.com/BitArt/archive/2013/05/27/3101037.html 一. 基本信息 1. 概述 I²C 是Inter-Integrate ...

- I2C总线之(一)---概述

概述: I²C 是Inter-Integrated Circuit的缩写,发音为"eye-squared cee" or "eye-two-cee" , 它是一 ...

- 【转】I2C总线协议

I2C总线(Inter Integrated-Circuit)是由PHILIPS公司在上世纪80年代发明的一种电路板级串行总线标准,通过两根信号线——时钟线SCL和数据线SDA——即可完成主从机的单工 ...

- (3)I2C总线的字节格式,时钟同步和仲裁

字节格式 发送到SDA线上的每个字节必须是8位.每次传输的字节数量是不受限制的.每个字节后必须跟着一个ACK应答位.数据从最高有效位(MSB)开始传输.如果从机要执行一些功能后才能接收或者发送新的完整 ...

- 【转载】SPI总线和I2C总线的异同点

来源:https://blog.csdn.net/lishun1422840684/article/details/77776763 总结的简单.明了.适用! 一:SPI接口的全称是"Ser ...

- I2C总线之(三)---以C语言理解IIC

为了加深对I2C总线的理解,用C语言模拟IIC总线,边看源代码边读波形: 如下图所示的写操作的时序图: 读时序的理解同理.对于时序不理解的朋友请参考“I2C总线之(二)---时序” 完整的程序如下: ...

- I2C总线协议学习笔记 (转载)

1.I2C协议 2条双向串行线,一条数据线SDA,一条时钟线SCL. SDA传输数据是大端传输,每次传输8bit,即一字节. 支持多主控(multimastering),任何时间点只能有一 ...

随机推荐

- 一次python 内存泄漏解决过程

最近工作中慢慢开始用python协程相关的东西,所以用到了一些相关模块,如aiohttp, aiomysql, aioredis等,用的过程中也碰到的很多问题,这里整理了一次内存泄漏的问题 通常我们写 ...

- 2018年中国C++大会详细日程+报名

http://purecpp.org/detail?id=2050

- golang中值类型/指针类型的变量区别总结

转自:https://segmentfault.com/a/1190000012329213 值类型的变量和指针类型的变量 先声明一个结构体: type T struct { Name string ...

- 微信公众号 chinaxdt 的 解压密码 mima

关于密码:解压密码获取方式第一步关注微信号“chinaxdt”第二步发送信息“mima”即可获取自动回复解压密码 这个 chinaxdt 的微信公众号已经失效,所以大家也不用去加了,密码我这告诉大家. ...

- [转]decorator(HTML装饰器)

原文地址:https://blog.csdn.net/jzh440/article/details/7770013 1>:每当遇到一个新的技术,首先我会问自己,这个技术是做神马的?用这个技术有神 ...

- mysql数据字段整理

<?php header('content-type:text/html;charset=utf-8'); define('DB_HOST','127.0.01'); define('DB_US ...

- Scala学习笔记(七):Rational、隐式转换、偏函数、闭包、重复参数及柯里化

class Rational(n: Int, d: Int) { require(d != 0) private val g: Int = gcd(n, d) val number: Int = n ...

- 【Python】博客信息爬取-微信消息自动发送

1.环境安装 python -m pip install --upgrade pip pip install bs4 pip install wxpy pip install lxml 2.博客爬取及 ...

- php四个常用类封装

这4个类分别是Mysql类. 分页类.缩略图类.上传类. Mysql类 <?php /** * Mysql类 */ class Mysql{ private static $link = nul ...

- (二)区块链的共识算法:PoS 及其 例子 代码 实现

作者:林冠宏 / 指尖下的幽灵 掘金:https://juejin.im/user/587f0dfe128fe100570ce2d8 博客:http://www.cnblogs.com/linguan ...