采用FPGA实现音频模数转换器

http://www.21ic.com/app/eda/200905/42832.htm

http://www.eefocus.com/article/09-10/84673s.html

摘 要 简要分析sigma—deIta(∑一△)架构模数转换器(ADC)原理,提出一种基于FPGA内部LVDS(Low Voltage Differential Signaling)接收器的音频ADC架构,并给出在FPGA上的实现结果。在FPGA内部实现音频ADC,具有扩展方便灵活,实现简单,集成度高等优点。

关键词 sigma—delta FPGA LVDS 音频ADC

引 言

数字系统已经越来越广泛地应用到现实世界的各个领域中,绝大多数数字系统无法直接处理现实世界中的信号,必须采用ADC器件把模拟信号转换成数字信号后才能处理。FPGA和DSP处理器是数字信号处理的两大主流技术。随着技术的发展和进步,一些FPGA器件集成了一些模拟电路以及混合信号处理模块,比如集成温度监控二极管。Actel公司的混合FPGA系列已经集成ADC、DAC、PGA(Programmable Gain Amplifier)、电压参考基准源和RCC(Resistance Capacitance)振荡器。Xilinx公司的V5系列FPGA集成电压和温度监控ADC,用户可以直接通过JTAG下载调试接口读取电压和温度值。但这些单元物理位置固定,灵活性受限,仅限于特定的应用。而采用FPGA的LVDS接收器来实现ADC,逻辑电路完全在FPGA内部实现,可重新配置,扩展性好,需要的外围器件少,使FPGA能直接进行混合信号处理。

1 ∑一△ADC原理

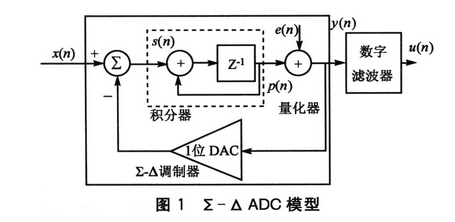

∑一△ADC的核心是∑一△调制器和数字滤波器。∑一△调制原理在半个多世纪前已经提出,但在20世纪90年代才广泛应用到ADC设计中。∑一△ADC的模型如图1所示。

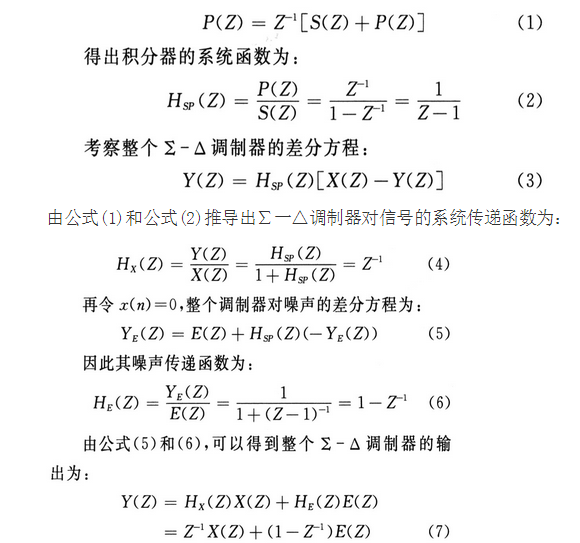

从图中可以看到,乏一△架构的ADC主要由左边方框内模拟∑一△调制器和右边的数字滤波器组成。∑-△调制器包含1个积分器、1个ADC和1个构成反馈环路的DAC。其中积分器用离散时间表示,以方便采用Z变换分析。e(n)是AD量化器的量化噪声。假设量化噪声是加性噪声,反馈环路中DAC是理想的,其传输函数是固定增益。采用线性系统分析方法,先令e(n)=O,考察积分器的差分方程:

由公式(7)可以看出,在Z变换域,调制器对信号只是延迟,而对噪声进行差分处理。因为差分器具有高通滤波器特性,因此噪声被高通滤波,调制器对应的时域输出为:

剩余的噪声则由后续的数字滤波器滤除。

2 LVDS收发器标准及其原理

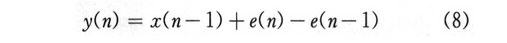

LVDS是一种低压低功耗的高速串行差分数据传输标准,在高速数据互联和数据通信领域得到广泛的应用,主流的FPGA器件都集成了高速的LVDS收发器。LVDS收发传输框图如图2所示。

在图2中,LVDS发送端的4个开关管交叉控制3.5mA电流源在接收端的流向。电流在100Ω电阻上建立约350 mV的电压差,接收器通过比较电压的极性来判决是逻辑“1”还是逻辑“0”。LVDS驱动器是电流型,对电源波动不敏感,功耗很低,1路LVDS传输功耗为35 mA×350 mV=1.2 mW。由于采用差分传输方式,LVDS收发器可以很好地消除共模干扰,提高系统电磁兼容性能。利用FPGA集成的LVDS接收器,配合少量外围器件,即可在FPGA内部实现ADC。

3 用FPGA集成的LVDS接收器实现ADC

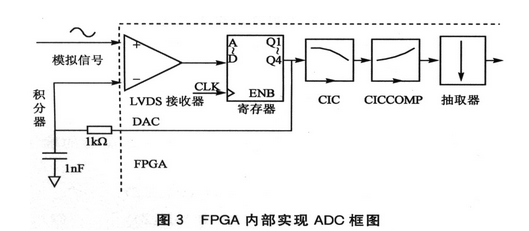

参考第2部分的∑一△架构的ADC原理,在FPGA内部实现ADC的框图如图3所示。

在图3中,虚线框内表示在FPGA内部实现。外部仅需要1个1 kΩ的电阻和1个1 nF的电容作为模拟积分器,输入信号和积分器输出值在LVDS接收器进行比较,比较结果被量化成数据比特流,经过寄存器后输出到CIC(Cascaded Integrated Comb)滤波器及其后续的数字滤波模块,同时通过1个FPGA引脚作为1位的DAC,输出到外部的积分器。在数字滤波模块里面,CIC滤波器累加量化的比特流并恢复成18位数的量化值,同时通过大倍数的抽取,把数据率降低;CICCOMP是15阶FIR滤波器,用于补偿CIC滤波器幅频响应。抽取器是31阶FIR低通滤波器,降低数据率并进一步滤除带外的噪声。整个系统运行于49.152 MHz时钟下,采样数据经过CIC进行512倍抽取后,数据率降为96 kHz,最后经过低通滤波器进行2倍抽取,数据率降为48 kHz。用FPGA实现ADC,包括LVDS接收器部分,全部采用VerilogHDL语言编写,实现简单,可移植性较好。

4 FPGA内部实现的ADC实验分析

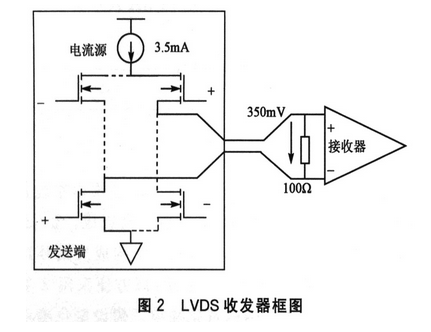

整个ADC设计工程在Xilinx公司的FPGA集成开发环境ISE下编译,下载到XC2VP70系列FPGA上进行测试,用Tektronix公司的信号源AFG3101产生音频信号,经ADC采用后通过板载的8位DAC输出,用Agilent公司的示波器54622D进行分析,频率为3 kHz的正弦信号输入/输出波形和频谱如图4所示。

图4上半部分波形是输入的信号和频谱,下半部分波形是经过ADC采样后通过DAC输出的波形和频谱。从图中可以看到,尽管受限于板载DAC的位数,DAC后面也没有抗混叠滤波器,仅将ADC的18位量化值高8位输出,但波形和频谱完全没有失真。输出波形上叠加的高频噪声是DAC转换引入的,可以通过滤波器滤除。信号源产生20 Hz~20 kHz的音频信号,ADC输出的波形和频谱均没有失真,FPGA在3.3 V的I/O电压下,ADC最大输入信号的峰值电压约O.8 V,输出信号SNR约为50 dB。

结语

FPGA实现ADC的模型,仅需要极少数外围元器件,核心模块均采用FPGA资源实现,明显降低板上面积,同时逻辑可重配置,具备强大的扩展性。通过适当改进和优化,该方法可以应用到语音通信,温度、电压监控,水压检测,压力传感等诸多领域。

采用FPGA实现音频模数转换器的更多相关文章

- 采用FPGA实现UART转SPI

应用笔记 V1.1 2015/2/10 采用FPGA实现UART转SPI 概述 本文提供了实现UART转SPI的Verilog代码的功能描述.这份笔记将介绍UART和SPI的基本知识,代码设计 ...

- 基于FPGA的线阵CCD实时图像采集系统

基于FPGA的线阵CCD实时图像采集系统 2015年微型机与应用第13期 作者:章金敏,张 菁,陈梦苇2016/2/8 20:52:00 关键词: 实时采集 电荷耦合器件 现场可编程逻辑器件 信号处理 ...

- 【资讯】天啦鲁,这十余款创客设计居然由FPGA搞定 [转]

按理说‘高大上’的FPGA,多出现在航天航空(如火星探测器).通信(如基站.数据中心).测试测量等高端应用场景.但麦迪却也发现,近期,在很多创客的作品内部都有FPGA的影子.这或许也从侧面看出,打从总 ...

- 【FPGA】相关介绍

什么是 FPGA ? FPGA是Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL.GAL.EPLD等可编程器件的基础上进一步发展的产物.它是作为专用集 ...

- 音频DAC剖析---解开HI-FI音质的秘密

选自:http://mp3.zol.com.cn/54/547689.html 无论我们是买MP3.MP4也好,实际上我们的数码播放器最经常使用的就是音乐播放功能,所以数码播放器的音质,一直是消费者的 ...

- FPGA的典型应用领域

本文关键字:fpga应用,fpga应用领域, fpga培训,FPGA应用开发入门与典型实例 一.数据采集和接口逻辑领域 1.FPGA在数据采集领域的应用 由于自然界的信号大部分是模拟信号,因此一般的信 ...

- FPGA入门1

FPGA入门知识介绍 近几年来,由于现场可编程门阵列(FPGA)的使用非常灵活,又可以无限次的编程,已受到越来越多的电子编程者的喜爱,很多朋友都想学习一些FPGA入门知识准备进行这个行业,现在关 ...

- CPLD VS FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL.GAL.CPLD等可编程器件的基础上进一步发展的产物.它是作为专用集成电路(ASIC)领域中的 ...

- 基于FPGA的线阵CCD图像测量系统研究——笔记

本文是对基于FPGA的线阵CCD图像测量系统研究(作者:高尚)的阅读笔记 第一章绪论 1. 读读看 读了前面的摘要依然没有看懂作者要做什么.接着往下读....终于看到了一个字眼“基于机器视觉的图像测量 ...

随机推荐

- 42.Trapping Rain Water---dp,stack,两指针

题目链接:https://leetcode.com/problems/trapping-rain-water/description/ 题目大意:与84题做比较,在直方图中计算其蓄水能力.例子如下: ...

- 中国区的Azure添加到 VSTS 的 Service Endpoint

把中国区的Azure添加到 VSTS (Visual Studio Team System) 的 Service Endpoint. 这个是使用 VSTS 自动部署到中国区Azure的前置条件. Se ...

- gtk+学习笔记(二)

如何创建一个按钮呢,直接贴代码把,有详细的注释. #include<gtk/gtk.h> gint data_count=; void on_button_clicked (GtkWidg ...

- MINIBASE源代码阅读笔记之HFPage

HFPage heap file的page的类 成员 slot_t:用来表示页里的slot,包括offset和length slot[]:倒着生长的slot array slotCnt:有多少已用sl ...

- 飘窗原生js效果

css: .close { width: 30px; height: 20px; background: white; position: absolute; right: 0; top: 0; z- ...

- ASN.1笔记——语法规则与类型概述

转载:https://blog.csdn.net/sever2012/article/details/7672699 一.简介 ASN.1(Abstract Syntax Notation doton ...

- Ubuntu 如何更换阿里源

#进入源地址 cd /etc/apt #备份源文件 sudo cp sources.list sources.list.bak #编辑 sudo vim /etc/apt/sources.list d ...

- CodeForces 785D Anton and School - 2

枚举,容斥原理,范德蒙恒等式. 先预处理每个位置之前有多少个左括号,记为$L[i]$. 每个位置之后有多少个右括号,记为$R[i]$. 然后枚举子序列中第一个右括号的位置,计算这个括号的第一个右括号的 ...

- Oracle意外赢官司,程序员或过苦日子

关于“Google在Android平台使用Java侵犯知识产权”一案,2014年5月,联邦法院判定Oracle获胜,这个结果完全出人意料,因为这样一来无异于打开了软件开发领域中API使用方式的潘多拉之 ...

- 最小生成树---->prim算法的应用 hdu1863

畅通工程 Time Limit: 1000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others) Total Submi ...