A/X家FPGA架构及资源评估

评估对比xilinx以及altera两家FPGA芯片逻辑资源。

首先要说明,

- 现今FPGA除了常规逻辑资源,还具有很多其他片内资源比如块RAM、DSP单元、高速串行收发器、PLL、ADC等等,用以应对不同的场合,逻辑量只能作为选型的重要依据之一。

- 不同厂家FPGA架构各异,具有很多独有的专利设计,量级相当的FPGA在应对不同应用场景下(比如视频处理、通讯总线、加密算法)时表现可能会差异很大,逻辑资源评估只是作为通常意义上的选型参考。

本文以占有率最大的X家和A家为例来进行比较。

首先对比下两家的芯片架构,

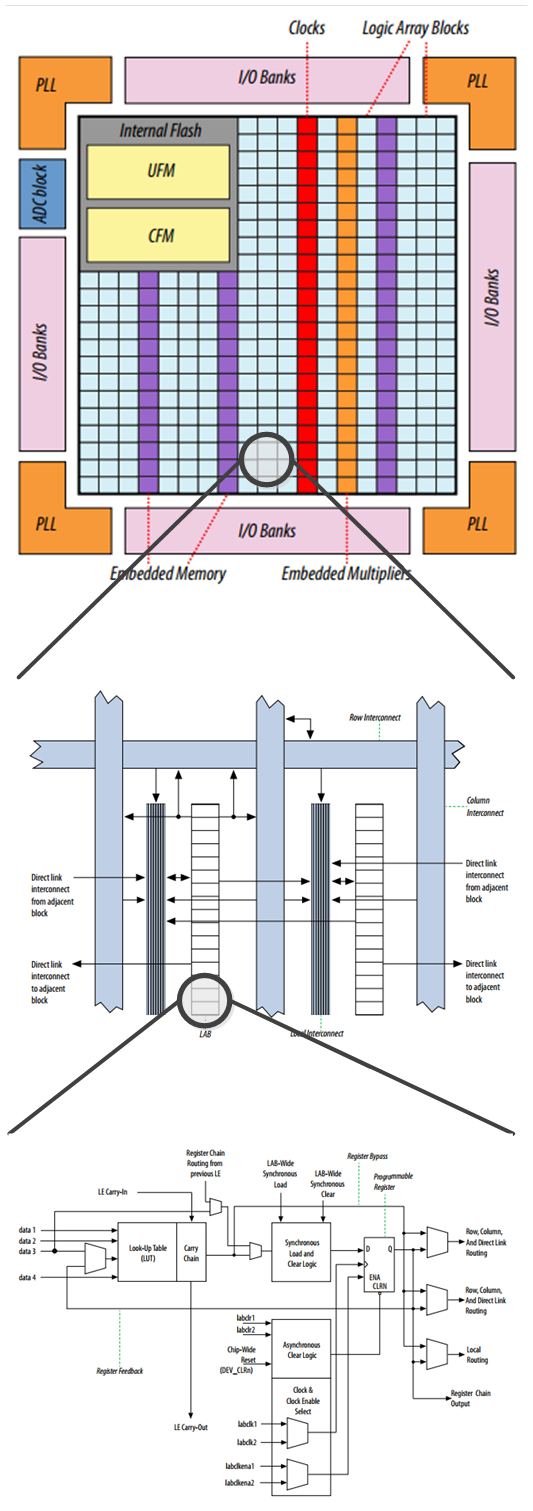

Altera LUT4架构(以入门级MAX10为例,以下材料来源于m10_handbook)

基本的逻辑单元由LAB组成,每个LAB包含16个LE,LE主要由一个LUT-4以及一个触发器。

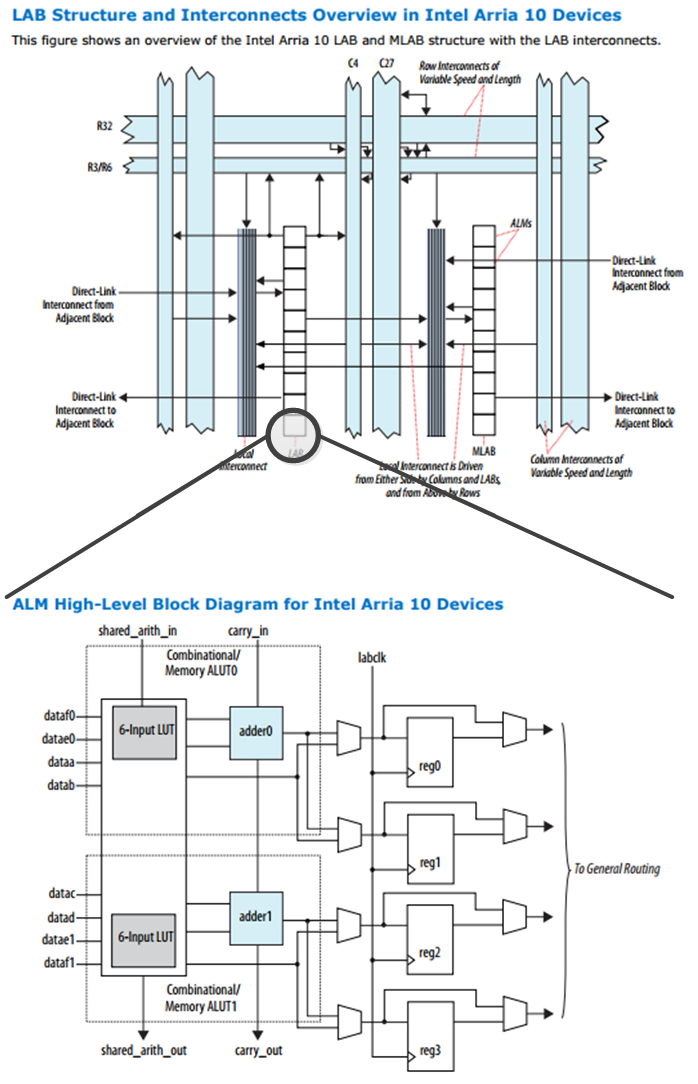

Altera ALM架构(以Arria10系列为参考)

基本逻辑单元LAB包含10xALM,ALM全程为Adaptive Logic Module,具有8输入和2输出,一个ALM可以配置成不同的LUT组合,比如2个单独LUT4、单独LUT5+LUT3、共享一个输入的LUT5+LUT4等等。ALM相比单独的LUT4架构显然具有更大的灵活性。

(a10_handbook.pdf)

Xilinx(以7系列为例)

赛灵思基本逻辑单元叫做CLB,CLB内有具有两片Slice,每个Slice由4片LUT6及8个触发器组成。可见每个CLB约等于8 x LUT6。

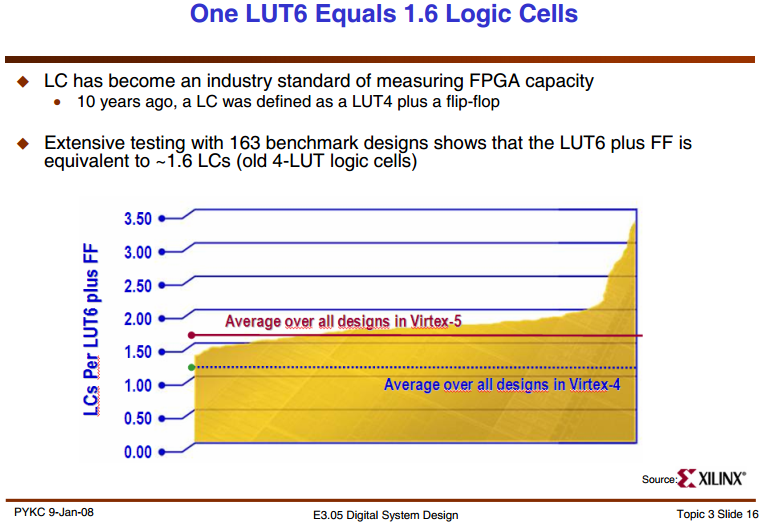

由于最早的FPGA多为基于LUT4组成,惯用的做法是用LUT4的数量近似表示逻辑量。现在FPGA不一定是基于LUT4,但可以转换成等效LUT4数量。XIlinx的叫做LC,ALTERA叫做LE,都可以理解成一个LUT4加触发器的单元的数量。

对MAX10来说,LE的数量就等于LUT4的数量,而xilinx 7系列基于LUT6,LUT与LC有如下换算关系:

A/X家FPGA架构及资源评估的更多相关文章

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- Serverless 的资源评估与成本探索

Serverless 布道师在讲解 Serverless 架构和云主机等区别的时候,总会有类似的描述: 传统业务开发完成想要上线,需要评估资源使用.根据评估结果,购买云主机,并且需要根据业务的发展不断 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- 浅谈FPGA资源评估

在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源. FF和LUT的数目: 这个在写出具体代码之前,初学者通常没法估算,但资深FPGA工程师会估算出一个数量级.通常的做法 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- Kubernetes(二)架构及资源关系简单总结

Kubernetes架构 先引用一下官方的架构图: 对于本文来说,我觉得这张图有点复杂了,但是我又懒得自己画了,就用这张吧.Kubernetes是一个集群,和传统的集群相似,它也是有一个主节点和若干个 ...

- 3、flink架构,资源和资源组

一.flink架构 1.1.集群模型和角色 如上图所示:当 Flink 集群启动后,首先会启动一个 JobManger 和一个或多个的 TaskManager.由 Client 提交任务给 JobMa ...

- 对FPGA的时钟资源理解(更新中)

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟.内部时钟进行处理,生成需要的低抖动时钟.PLL是MMCM的功能子集, ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

随机推荐

- VFS四大对象之三 struct dentry

继上一篇文章介绍了inode结构体:继续介绍目录项dentry: http://www.cnblogs.com/linhaostudy/p/7427794.html 三.dentry结构体 目录项:目 ...

- MCMC,GIBBS SAMPLING简单摘要

本文后面很多内容都是参考博客:http://www.cnblogs.com/xbinworld/p/4266146.html.本文主要用作学习交流备忘用. 1)简述: 随机模拟也可以叫做蒙特卡洛模拟, ...

- $(document).ready()和window.onload之间的差异

最近使用$(document).ready(function(){})遇到一个问题:加载页面后发送数据请求后台,得到的数据不对,后发现请求后台时,发送的数据为空,没有获取到值导致的.------改成w ...

- Java与算法之(1) - 冒泡排序

冒泡排序法的原理是,每次比较相邻的两个元素,如果它们的顺序错误就把它们交换过来. 例如对4 3 6 2 7 1 5这7个数字进行从小到大的排序,从最左侧开始,首先比较4和3 因为是从小到大排序,4和3 ...

- python写unix口令破解器

看了python绝技做出来的unix口令破解器 首先需要crypt. python并不自带!! windows下pip安装失败= = 后来直接去kali敲了 附件:jiami.txt #假设是unix ...

- JVM GC知识回顾

这两天刚好有朋友问到我面试中GC相关问题应该怎么答,作为java面试中热门问题,其实没有什么标准回答.这篇文章结合自己之前的总结,对GC做一个回顾. 1.分代收集 当前主流VM垃圾收集都采用" ...

- 51 NOD 1238 最小公倍数之和 V3

原题链接 最近被51NOD的数论题各种刷……(NOI快到了我在干什么啊! 然后发现这题在网上找不到题解……那么既然A了就来骗一波访问量吧…… (然而并不怎么会用什么公式编辑器,写得丑也凑合着看吧…… ...

- HDU-5340 Three Palindromes(字符串哈希)

http://acm.hdu.edu.cn/showproblem.php?pid=5340 orz到了新的字符串hash姿势 #include<cstdio>#include<cs ...

- Max Sum(dp)

题目链接:http://acm.hdu.edu.cn/showproblem.php?pid=1003 Max Sum Time Limit: 2000/1000 MS (Java/Others) ...

- [国嵌笔记][029][ARM处理器启动流程分析v2]

2440启动流程 启动方式:nor flash启动.nand flash启动 地址布局: 选择nor flash启动时,SROM(nor flash)地址为0x00000000 选择nand flas ...