AMBA APB总线

前面分析了AHB总线协议。接下来分析APB总线协议。

(一) APB总线接口:

PCLK APB总线时钟。

PRESETn APB总线复位。低有效。

PADDR 地址总线。

PSELx 从设备选择。

PENABLE APB传输选通。

PWRITE 高为写传输,低为读。

PRDATA 读数据总线。

PWDATA 写数据总线。

接口信号定义如下:

interface apb_slv_intf #(

parameter AW = ,

DW =

) (

input logic PCLK,

input logic PRESETn

);

logic PSEL;

logic PENABLE;

logic [AW-:] PADDR;

logic PWRITE;

logic [DW-:] PWDATA; logic [DW-:] PRDATA; modport m (

input PRDATA,

output PSEL, PENABLE, PADDR, PWRITE, PWDATA

); modport s (

input PSEL, PENABLE, PADDR, PWRITE, PWDATA,

output PRDATA

); endinterface: apb_slv_intf

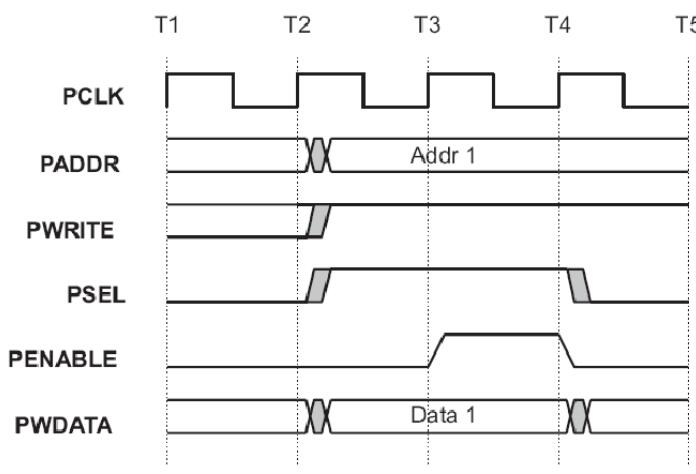

(二) APB总线时序图:

写传输

读传输

注意在PENABLE信号有效后从设备需要给出有效数据/读取有效数据。

(三) AHB总线到APB总线转换桥

module ahb2apb_bridge #(

parameter AHB_AW = ,

AHB_DW = ,

APB_AW = ,

APB_DW = ,

NSLV =

) (

input logic HCLK,

input logic HRESETn,

input logic PCLK,

input logic PRESETn,

ahb_slv_intf.s ahb,

apb_slv_intf.m apbv[NSLV]

); logic ahb_work;

logic apb_work; genvar i; typedef enum logic [:] {

AHB_IDLE = 'b00,

AHB_WRITE = 'b01,

AHB_READ = 'b10,

AHB_WAIT = 'b11

} ahb_state_e; // Signal of AHB Domain

struct {

logic work;

logic [AHB_AW-:] addr;

logic [AHB_DW-:] data;

logic write;

ahb_state_e cstate, nstate;

} ahbd; typedef enum logic [:] {

APB_IDLE = 'b00,

APB_WRITE = 'b01,

APB_READ = 'b10

} apb_state_e; // Signal of APB Domain

struct {

logic work;

logic [APB_DW-:] data[NSLV];

logic PSEL[NSLV];

logic PENABLE[NSLV];

apb_state_e cstate, nstate;

} apbd; // AHB Control Logic

always_comb begin

case (ahbd.cstate)

AHB_IDLE: begin

if (ahb.HSEL && ahb.HTRANS == HTRANS_NONSEQ) begin

if (ahb.HWRITE)

ahbd.nstate = AHB_WRITE;

else

ahbd.nstate = AHB_READ;

end

else

ahbd.nstate = AHB_IDLE;

end

AHB_WRITE: begin

if (apbd.work)

ahbd.nstate = AHB_WAIT;

else

ahbd.nstate = AHB_WRITE;

end

AHB_READ: begin

if (apbd.work)

ahbd.nstate = AHB_WAIT;

else

ahbd.nstate = AHB_READ;

end

AHB_WAIT: begin

if (!apbd.work)

ahbd.nstate = AHB_IDLE;

else

ahbd.nstate = AHB_WAIT;

end

default: ahbd.nstate = AHB_IDLE;

endcase

end always_ff @(posedge HCLK or negedge HRESETn) begin

if (!HRESETn)

ahbd.cstate <= AHB_IDLE;

else

ahbd.cstate <= ahbd.nstate;

end always_ff @(posedge HCLK or negedge HRESETn) begin

if (!HRESETn) begin

ahbd.work <= 'b0;

ahbd.addr <= '0;

ahbd.data <= '0;

ahbd.write <= 'b0;

ahb.HREADY <= 'b1;

ahb.HRDATA[APB_DW-:] <= '0;

end

else begin

case (ahbd.cstate)

AHB_IDLE: begin

if (ahb.HSEL && ahb.HTRANS == HTRANS_NONSEQ) begin

ahbd.addr <= ahb.HADDR;

ahbd.write <= ahb.HWRITE;

ahb.HREADY <= 'b0;

end

else begin

ahbd.addr <= '0;

ahbd.write <= 'b0;

ahb.HREADY <= 'b1;

end

ahbd.work <= 'b0;

ahbd.data <= '0;

ahb.HRDATA[APB_DW-:] <= apbd.data[ahbd.addr[AHB_AW-:AHB_AW-]];

end

AHB_WRITE: begin

ahb.HREADY <= 'b0;

ahbd.work <= 'b1;

ahbd.data <= ahb.HWDATA;

ahb.HRDATA[APB_DW-:] <= '0;

end

AHB_READ: begin

ahbd.work <= 'b1;

ahbd.data <= '0;

ahb.HREADY <= 'b0;

ahb.HRDATA[APB_DW-:] <= '0;

end

AHB_WAIT: begin

ahbd.work <= 'b0;

ahb.HREADY <= 'b0;

ahb.HRDATA[APB_DW-:] <= '0;

end

endcase

end

end assign ahb.HRESP = HRESP_OKAY;

// assign ahb.HRDATA[AHB_DW-1:APB_DW] = '0; // APB Control Logic

always_comb begin

case (apbd.cstate)

APB_IDLE: begin

if (ahbd.work) begin

if (ahbd.write)

apbd.nstate = APB_WRITE;

else

apbd.nstate = APB_READ;

end

else

apbd.nstate = APB_IDLE;

end

APB_WRITE: apbd.nstate = APB_IDLE;

APB_READ: apbd.nstate = APB_IDLE;

default: apbd.nstate = APB_IDLE;

endcase

end always_ff @(posedge PCLK or negedge PRESETn) begin

if (!PRESETn)

apbd.cstate <= APB_IDLE;

else

apbd.cstate <= apbd.nstate;

end always_ff @(posedge PCLK or negedge PRESETn) begin

if (!PRESETn) begin

apbd.work <= 'b0;

for (int j = ; j < NSLV; j++) begin

apbd.PSEL[j] <= 'b0;

apbd.PENABLE[j] <= 'b0;

end

end

else begin

case (apbd.cstate)

APB_IDLE: begin

if (ahbd.work) begin

apbd.work <= 'b1;

for (int j = ; j < NSLV; j++)

apbd.PSEL[j] <= (ahbd.addr[AHB_AW-:AHB_AW-] == j) ? 'b1 : 1'b0;

end

else begin

apbd.work <= 'b0;

for (int j = ; j < NSLV; j++)

apbd.PSEL[j] <= 'b0;

end

for (int j = ; j < NSLV; j++)

apbd.PENABLE[j] <= 'b0;

end

APB_WRITE: begin

apbd.work <= 'b1;

for (int j = ; j < NSLV; j++)

apbd.PENABLE[j] <= (ahbd.addr[AHB_AW-:AHB_AW-] == j) ? 'b1 : 1'b0;

end

APB_READ: begin

apbd.work <= 'b1;

for (int j = ; j < NSLV; j++)

apbd.PENABLE[j] <= (ahbd.addr[AHB_AW-:AHB_AW-] == j) ? 'b1 : 1'b0;

end

endcase

end

end generate

for (i = ; i < NSLV; i++) begin: apbv_loop

assign apbv[i].PADDR = {'h0, ahbd.addr[APB_AW-4-1:0]};

assign apbv[i].PWRITE = ahbd.write;

assign apbv[i].PWDATA = ahbd.data[APB_DW-:];

assign apbd.data[i] = apbv[i].PRDATA;

assign apbv[i].PSEL = apbd.PSEL[i];

assign apbv[i].PENABLE = apbd.PENABLE[i];

end

endgenerate endmodule: ahb2apb_bridge

AMBA APB总线的更多相关文章

- AHB总线和APB总线

AHB主要用于高性能模块(如CPU.DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作:非三态的实现方式:支持突发传输:支持分段传输:支持多个主控制器:可配置 ...

- APB总线

APB(Advance Peripheral Bus)是AMBA总线的一部分,从1998年第一版至今共有3个版本. AMBA 2 APB Specfication:定义最基本的信号interface, ...

- AMBA AHB总线

Advanced Microcontroller Bus Architecture, 即AMBA,是ARM公司提出的总线规范,被很多SoC设计所采用,常用的实现有AHB(Advanced High-P ...

- STM32WB AHB总线、APB总线与外设

方框图: 如图所示: 1)APB1外设 2)APB2外设 3)AHB1外设 4)AHB2外设 5)AHB3外设 6)AHB4外设(ABH共享总线外设) 内存映射关系图:

- AMBA总线介绍

The Advanced Microcontroller Bus Architecture (AMBA) specification defines an on- chip communication ...

- APB协议

https://wenku.baidu.com/view/2663f629ef06eff9aef8941ea76e58fafab04592.html https://www.cnblogs.com/l ...

- AMBA总线协议AHB、APB

一.什么是AMBA总线 AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus).ASB (Advanced ...

- AMBA总线协议AHB、APB、AXI对比分析【转】

转自:https://blog.csdn.net/ivy_reny/article/details/56274412 一.AMBA概述 AMBA (Advanced Microcontrolle ...

- [转]AMBA、AHB、APB、ASB总线简介

[转]http://www.cnblogs.com/zhaozhong1989/articles/3092140.html 1.前言 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大.数字IC ...

随机推荐

- python 全栈开发,Day17(初识面向对象)

一.引子 第一次参加工作,进入了一家游戏公司,公司需要开发一款游戏<人狗大战>一款游戏,首先得把角色和属性定下来. 角色有2个,分别是人和狗属性如下:人 :昵称.性别.血.攻击力狗 :名字 ...

- bind函数详解(转)

var name = "The Window"; var object = { name: "My Object", getNameFunc: function ...

- Codeigniter使用HMVC(一)

涉及三方代码: https://tutorials.kode-blog.com/codeigniter-admin-panel https://bitbucket.org/wiredesignz/co ...

- hdu 2112 map+Dijkstra

无向图 用map 起点和终点可能一样 数组不能开太大 WA了好多发 Sample Input6xiasha westlake //起点 终点xiasha station 60xiasha Shoppi ...

- jsp+servlet实现最基本的注册登陆功能

源码和数据库下载地址:http://download.csdn.net/detail/biexiansheng/9759722 1:首先需要设计好数据库和数据表,这里简单截图说明我创建的字段和类型. ...

- centos6.5上安装配置telnet服务

https://blog.csdn.net/wx5040257/article/details/78327915

- asp.net core 微信公众号支付(扫码支付,H5支付,公众号支付,app支付)之3

在微信公众号中访问手机网站,当需要调用支付时候无法使用H5支付,只有使用微信公众号支付,使用公众号支付用户必须关注该公众号同时该公众号必须开通公众号支付功能. 1.获取用户的OpenId ,参考之前写 ...

- hzy 和zsl 的生存挑战

Problem Description zsl 和hzy 来到了臭臭城堡,打算挑战臭臭城堡的大魔王hyz,大魔王hyz设置了这样的一个挑战:1. zsl 和hzy两个人各自来到一间密室,期间两人无法以 ...

- java过滤防止sql注入过滤

/** * 过滤特殊字符 * @author: Simon * @date: 2017年8月31日 下午1:47:56 * @param str * @return */ public static ...

- VSCode tasks.json中的各种替换变量的意思 ${workspaceFolder} ${file} ${fileBasename} ${fileDirname}等

When authoring tasks configurations, it is often useful to have a set of predefined common variables ...