modelsim仿真正确FPGA运行不正确的可能原因 - cm4写寄存器错

困住整整一周了,工作进行不下去,中午偶遇导师,指导意见是有两种可能:

1. FPGA编译器优化代码,可以考虑把综合过程中所有的warning排查一下

2. verilog里有不可综合的语句。

又及,原有的功能模块完全正确,自己改写的不行,导师说那是自己写的时序不对,仿正确的模块看modesim里自己写的和正确的模块时序差在哪里,修改自己的。

添加各种(*keep="true"*),未果

排查所有warning,没看到会和这个问题相关

相信大神导师写的代码不会有问题

一下午加晚上各种折腾,甚至画卡诺图与非门硬写了一个bit_mask,嗯,AHB总线的HSIZE+ADDR选择屏蔽哪个字节的代码有了:

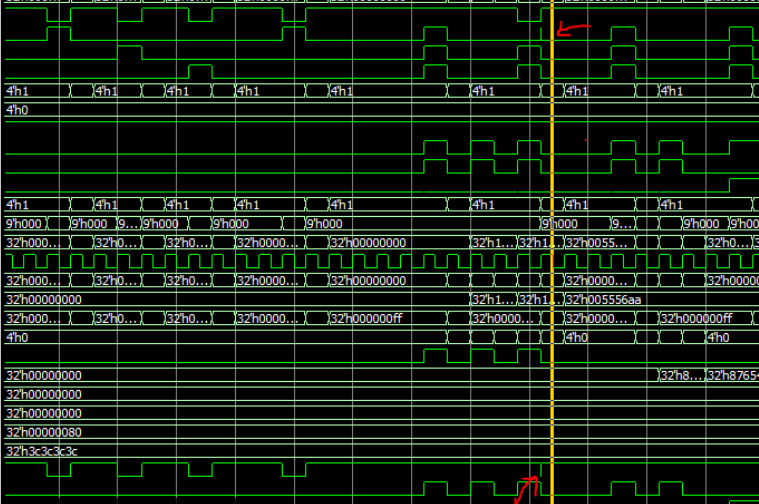

等综合的时候胡乱看modelsim,突然发现了个小毛刺:

开始怀疑写的时候没有对齐,引出hready信号加在写使能寄存器控制端,最后一遍综合,没有报希望,开始收拾桌子,打算明天再搞了,然后,生活永远比电视剧精彩,峰回路转,柳暗花明。

其实最开始分析代码的时候考虑过这个问题,还试了,只是加在了byte_mask寄存器的控制端,无效。当时也隐约考虑过这个写使能信号好可疑的样子,然后...不知道为什么没有追究下去,中间modelsim仿真看波形各种折腾两天。

想起回家时候爷爷经常叨叨我的话,现在觉得好有道理。

问题找到了,第二天用了大半个下午分析原因:

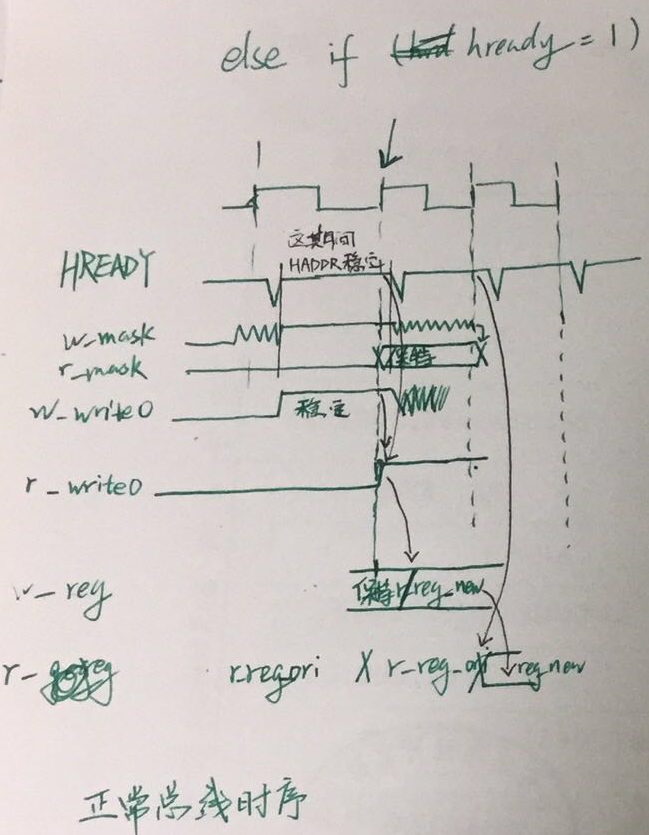

正常的总线读写时序应该是这样:

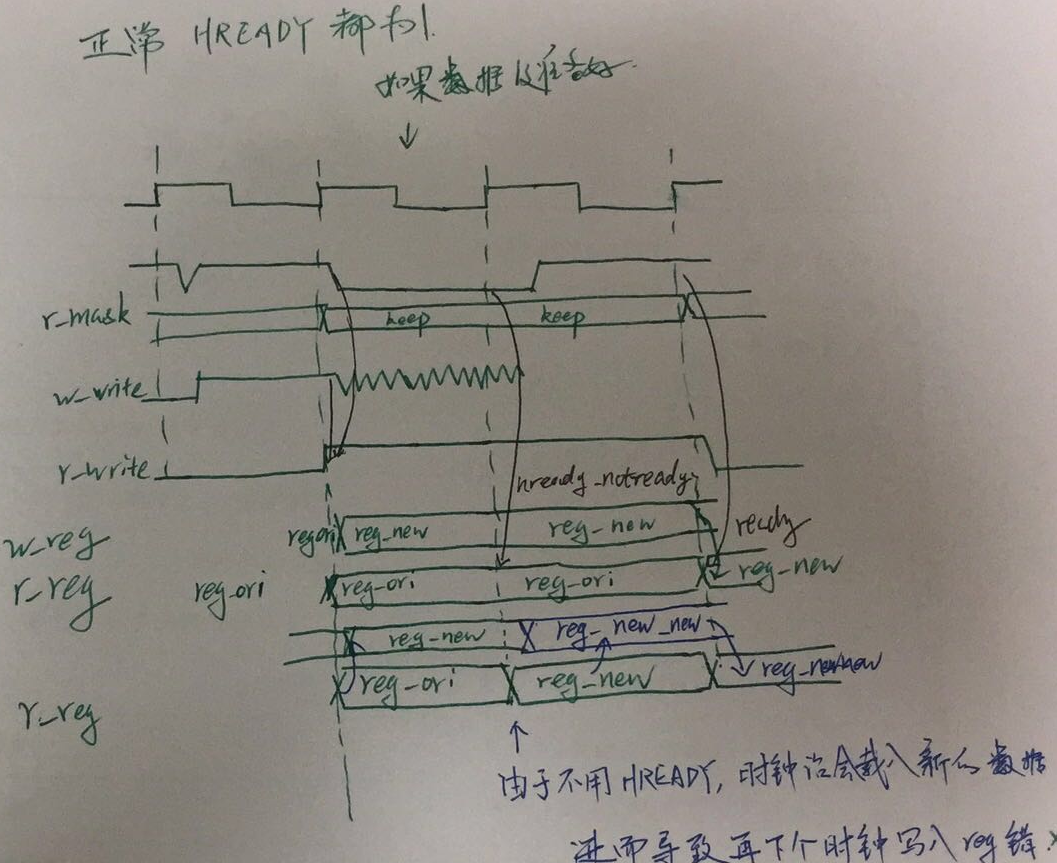

因为加了HREADY控制就好了,本来是怀疑第二拍写数据的时候数据没有准备好,那HREADY定然是低电平,像这样:

怎么分析都觉得好有道理的样子,嗯,定然是这样,由于没有用HREADY来控制写使能信号,导致寄存器在不该更新的时候更新了。可是仔细推敲,又傻了,因为mask信号是用HREADY控制的,如果数据没有准备好,mask不会变,进而写入的还是会正确。

仔细再想,觉得问题不是出在总线数据没准备好,是HREADY有效总会比其他控制信号有效到的晚,是这样:

根据verilog,写使能信号

ce_re = HSEL&HWRITE&HTRANS[]&HADDR[相应的地址]

如果在时钟上升沿,这些信号已经都有效了,就会导致不用HREADY控制的写使能寄存器比期待的提前一拍置位(写使能应该在写数据周期有效,而不应该在写地址周期有效),而此刻mask信号还在等HREADY,不会有效,从而导致写寄存器错误。

附带两个小现象也解释的通:

1. 完全相同的逻辑,m0p没有这个问题 - m0p访问指令、数据、外设都用这同一组总线,总线表示自己很忙,控制信号可能不会跑的那么快(只是这么猜测,不确定)。

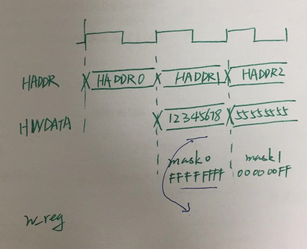

2. KEIL调试的时候一个现象,对于如下代码:

*(int *)(0x40000000) = 0x12345678;

*(char *)(0x40000000) = 0x55;

如果单步调试,第二拍写入会导致0x40000000地址处其他字节都变为零0x00000055,但如果在中间塞一个访问总线的语句,比如这样:

1 *(int *)(0x40000000) = 0x12345678;

2 c0 = *(int *)(0x40000000)

3 *(char *)(0x40000000) = 0x55;

就没问题,执行完第三行,0x40000000地址处数据为0x12345655,正确写入不影响其他。又想起cm4手册里对LDR STR指令的注释:总线流水可达到一周期仿问。

因为总线流水的时候,din刚刚好保持了上一个时钟里给写进来的数据,虽然寄存器变了,但下一拍的寄存器数据是这一拍数据和寄存器的组合电路,由于mask和din的状态,保证刚好下一拍写入寄存器的数据没有变。就是这样:

数据的正确不是因为总线流水的时候写使能信号怎么了,是因为上一拍的写入数据刚好在。

modelsim仿真正确FPGA运行不正确的可能原因 - cm4写寄存器错的更多相关文章

- Modelsim SE 仿真 ALTERA FPGA IP

Modelsim SE 仿真 ALTERA FPGA IP 最近,有几个朋友问过我是不是有新版本的Modelsim altera,其原因是 Qii 升级为新版本的,但是没配套的modelsim,没办法 ...

- jmeter链接数据库,信息全部填写正确,运行之后没有结果

之前遇到一个很苦恼的问题,jmeter链接数据库,数据库填写的资料全部都没有问题,在其他电脑jmeter上都可以正常链接,但是在我的电脑上运行却总是不出结果, 用mysql链接数据库也一切正常,一直找 ...

- 【黑金原创教程】【Modelsim】【第一章】Modelsim仿真的扫盲文

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- ModelSim仿真教程

本文章详细介绍了怎样用ModelSim仿真Verilog,虽然只是很简单的一个二分频器的例子,但却正式小白入门所需要的. 本教程以ModelSim SE 10.4为例 1. 新建工程 file-> ...

- cordic算法的verilog实现及modelsim仿真

1. 算法介绍 CORDIC(Coordinate Rotation Digital Computer)算法即坐标旋转数字计算方法,是J.D.Volder1于1959年首次提出,主要用于三角函数.双曲 ...

- 用ModelSim仿真SDRAM操作

之前写了两篇关于Modelsim仿真的blog,其中模块管脚的命名可能让人觉得有些奇怪,其实不然,之前的两篇内容都是为了仿真SDRAM操作做铺垫的. 由于SDRAM的仿真过程相对比较复杂,也比较繁琐. ...

- ModelSim仿真入门

ModelSim仿真入门之一:软件介绍 编写这个教程之前,为了让不同水平阶段的人都能阅读,我尽量做到了零基础入门这个目标,所有的操作步骤都经过缜密的思考,做到了详细再详细的程度. 如果您是FPGA开发 ...

- Vivado级联Modelsim仿真Re-launch问题

前两天在群里看到有朋友说Vivado级联Modelsim仿真出现修改设计代码后重新run do文件,波形没有随着代码修改而改变,这个问题博主之前没有注意到,因为把Vivado和Modelsim级联好后 ...

- 每天进步一点点------ModelSim仿真Altera的ROM

1. 在QuartusII中生成rom的初始化文件,可以是hex,也可以是mif.MIF文件的格式很简单明了,所以我一向都是用MIF. 2.下载convert_hex2ver.dll文件,conver ...

随机推荐

- 重写Object的equals方法

Object的equals比较两个对象是否相同,没有重写时比较的是内存地址是否相同(==). 但我们有时候比较的是两个对象中的属性是否相同, 重写equals: package cn.sasa.dem ...

- 洛谷P4823 拯救小矮人 [TJOI2013] 贪心+dp

正解:贪心+dp 解题报告: 传送门! 我以前好像碰到过这题的说,,,有可能是做过类似的题qwq? 首先考虑这种显然是dp?就f[i][j]:决策到了地i个人,跑了j个的最大高度,不断更新j的上限就得 ...

- 【PyQt5-Qt Designer】PyQt5+eric6 安装和配置

PyQt5+eric6 安装及配置 1.利用pip命令安装PyQt5 第一步:安装PyQt5 在cmd命令行中输入: pip install PyQt5 第二步:安装Qt的工具包 pip instal ...

- TensorFlow安装之后导入报错:libcudnn.so.6:cannot open sharedobject file: No such file or directory

转载自:http://blog.csdn.net/silent56_th/article/details/77587792 系统环境:Ubuntu16.04 + GTX1060 目的:配置一下pyth ...

- ZedBoard上运行linux系统的准备工作框架

目标:ZedBoard上运行linux系统. 需要什么:图中上色部分. 应该做哪些工作:上色部分之前的所有步骤. 由上图得知,为了顺利在zedboard上构建嵌入式Linux操作系统,我们一般需要如下 ...

- Redis和Memcache的区别是什么

Redis和Memcache都是内存数据库,但它们之间还是有区别的,跟着ytkah看看Redis和Memcache的区别吧 Redis 支持多种数据结构,如string,list,dict,set,z ...

- windows系统redmine安装总结

今天在公司服务器上安装了redmine,主要用于项目管理和缺陷跟踪.安装过程比较简单,总结如下: 1.网上下载redmine安装包(bitnami-redmine-3.3.1-0-windows-in ...

- 设置 matlab 画图格式

1:设置 matlab 画图格式 clear;clc; % load("array.mat"); % Bestallarray=array; % rllofcircle(Besta ...

- Mac提醒事项如何设置为24小时制

- IOP知识点(3)-Modal.show

1.position 模态框初始位置.可设为字符串 "左位置 上位置" 或数组 [左位置, 上位置],规则如下: 左位置 可设为 left|center|right 三者之一,上位 ...