FPGA时钟分频(转)

http://www.cnblogs.com/fpga/archive/2009/10/24/1589318.html

占空比为50%的分频

偶数分频比较简单

比如N分频,那么计数到N/2-1,然后时钟翻转,代码如下:

1 module even(clk_in,clk_out,rst_n);

2 input clk_in;

3 input rst_n;

4 output clk_out;

5

6 parameter N=6;

7

8 reg [3:0] cnt;

9 reg clk_out;

10

11 always @(posedge clk_in or negedge rst_n) begin

12 if(!rst_n) begin

13 cnt<=4'b0000;

14 clk_out<=0;

15 end

16 else if(cnt==(N/2-1)) begin

17 clk_out<=~clk_out;

18 cnt<=4'b0000;

19 end else cnt<=cnt+1;

20 end

21 endmodule

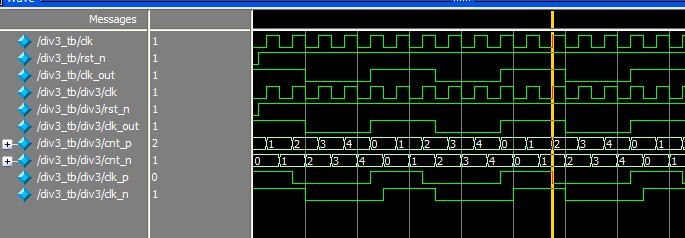

实现奇数分频,分别用上升沿计数到(N-1)/2-1,再计数到N-1,再用下降沿计数到(N-1)/2-1,再计数到N-1,,得到两个波形,然后相或即可 代码如下:

1 module div3(clk,clk_out,rst_n);

2 input clk,rst_n;

3 output clk_out;

4

5 reg [3:0] cnt_p,cnt_n;

6 reg clk_p,clk_n;

7 parameter N=5;

8

9 always @(posedge clk or negedge rst_n) begin

10 if(!rst_n)

11 cnt_p<=4'h0;

12 else if(cnt_p==N-1)

13 cnt_p<=0;

14 else cnt_p<=cnt_p+1;

15 end

16

17 always @(negedge clk or negedge rst_n) begin

18 if(!rst_n)

19 cnt_n<=4'h0;

20 else if(cnt_n==N-1)

21 cnt_n<=0;

22 else cnt_n<=cnt_n+1;

23 end

24

25 always @(posedge clk or negedge rst_n) begin

26 if(!rst_n)

27 clk_p<=1;

28 else if(cnt_p==(N-1)/2-1)

29 clk_p<=~clk_p;

30 else if(cnt_p==(N-1))

31 clk_p<=~clk_p;

32 end

33

34 always @(negedge clk or negedge rst_n) begin

35 if(!rst_n)

36 clk_n<=1;

37 else if(cnt_n==(N-1)/2-1)

38 clk_n<=~clk_n;

39 else if(cnt_n==(N-1))

40 clk_n<=~clk_n;

41 end

42 assign clk_out=clk_n|clk_p;

43 endmodule

FPGA时钟分频(转)的更多相关文章

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- 时钟分频方法---verilog代码

时钟分频方法---verilog代码 本文以SDI播出部分的工程为例,来说明一种时钟分频的写法.SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据 ...

- FPGA奇数分频

在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2.4.8.16.32.64等这些以2的整数倍的. 这里说的是奇数倍分频,如时钟是100MH ...

- FPGA三分频,五分频,奇数分频

我们在做FPGA设计时,有时会用到时钟频率奇数分频的频率,例如笔者FPGA的晶振为50M,当我们需要10M的时钟时,一种方式可以使用DCM或PLL获取,系统会内部分频到10M,但其实VERILOG内部 ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- 基于FPGA的飞机的小游戏

基于FPGA的飞机的小游戏 实验原理 该实验主要分为4个模块,采用至上而下的设计方法进行设计.由50M的晶振电路提供时钟源,VGA显示控制模块.图形显示控制模块.移动模块的时钟为25M,由时钟分频电路 ...

- 实验箱FPGA部分测试报告及A8与FPGA链接测试报告

其实,我一开始还以为实验箱不会有什么问题只是让我们多学习东西才做这个测试的,结果发现还真的有不少问题. 1.实验准备部分 安装驱动时,win10系统无法正确安装usb-blaster Windows ...

- verilog实现奇数倍分频

在学习FPGA的过程中,最简单最基本的实验应该就是分频器了, 同时分频器也是FPGA设计中使用频率非常高的基本设计之一, 尽管在芯片厂家提供的IDE中集成了锁相环IP, 如altera 的PLL,Xi ...

随机推荐

- c#中list使用示例

protected void Page_Load(object sender, EventArgs e) { List<string> studentNames = new List< ...

- EL&&JSTL

一.JSP技术 1.jsp脚本和注释 jsp脚本: 1)<%java代码%> ----- 内部的java代码翻译到service方法的内部 2)<%=java变量或表达式> - ...

- Linux入门(12)——解决双系统下Ubuntu16.04不能访问Windows分区

解决办法一: 进入windows系统,关闭快速启动,关机. 解决办法二: 如果办法一不能解决问题,用这个办法. 查看盘符: sudo fdisk -l 需要在查看盘符后记下目标盘符的数字,比如想解除C ...

- SQL Server Alwayson概念总结

一.alwayson概念 “可用性组” 针对一组离散的用户数据库(称为“可用性数据库” ,它们共同实现故障转移)支持故障转移环境. 一个可用性组支持一组主数据库以及一至八组对应的辅助数据库(包括一个主 ...

- Windows Server 2008通过计划任务定时执行bat文件

前段时间在Windows Server 2008安装了一套基于MySQL数据库的软件,处于数据安全的考虑,希望每天能够自动进行数据库备份.我在别人脚本的基础上自己写了一个数据库备份的bat脚本,双击该 ...

- LINUX 笔记-watch命令

命令格式:watch[参数][命令] 可以将命令的输出结果输出到标准输出设备,多用于周期性执行命令/定时执行命令 命令参数: -n或--interval watch缺省每2秒运行一下程序,可以用-n ...

- Java反射机制(Reflect)解析

一.导读 反射的概念是由Smith在1982年首次提出的,主要是指程序可以访问.检测和修改它本身状态或行为的一种能力.这一概念的提出很快引发了计算机科学领域关于应用反射性的研究.它首先被程序语言的设计 ...

- 更新Android Studio 3.0碰到的问题

更新完后试下运行正在维护的旧项目,出现各种错误,因为后来发现问题不在这,所以没记完整,大概如下: A larger heap for the Gradle daemon is recommended ...

- 快速部署PostgreSQL

PostgreSQL通常也简称Postgres,是一个关系型数据库管理系统,适用于各种Linux操作系统.Windows.Solaris.BSD和Mac OS X.本文基于CentOS7,使用yum源 ...

- python学习笔记(十一)之函数

牛刀小试: 定义一个无参函数 >>> def myFirstFunc(): ... print("Hello python") ... print("h ...