AMD移动FP5平台时序解释

好文章推荐:https://wenku.baidu.com/view/199379576137ee06eef91828.html

AMD(FP5封装)时序全解。

由于刚开始接触AMD移动平台,难免有错误;如有错误请指出共同进步。

配置如下:

APU:FP5 Processor

EC: ITE5570

CorePMU:RT3662AC

一、基本知识概括

1、IC pin脚信号解释

(1)一般OK是外部信号(对于IC来说是Input);PG是IC发出的(对于IC来说是Output);

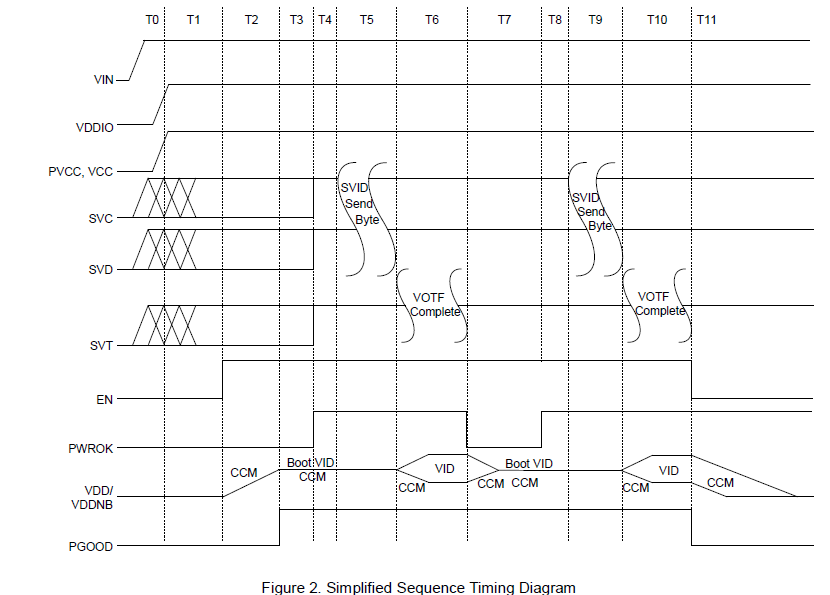

AMD开机:EN----》Boot VID固定设置(此时电压soft-start到VID电压值)-->PGOOD输出(达到vid设定电压后)------》

CPU(可以外部电路设计)---------》PWROK(CPU返回通知电源ic的能待SVID命令)------》SVI2接口解码--------动态输出电压

------》当VID电压又达到boot VID设置电压。

AMD关机:EN_LOW-------->PGOOD立即拉低------》output voltages enter soft-shutdown

2、SVID技术的本质

3、AMD单双桥主板

现在北桥的功能基本都分别整合到CPU和南桥里了

(1)单桥就是指CPU和北桥整合在一起,外带南桥;

(2)双桥就是指CPU、北桥、南桥都分别独立在主板上;

(3)我们这个AMD的APU是指CPU北桥南桥都整合在一起,低端笔记本。(不属于单双桥)

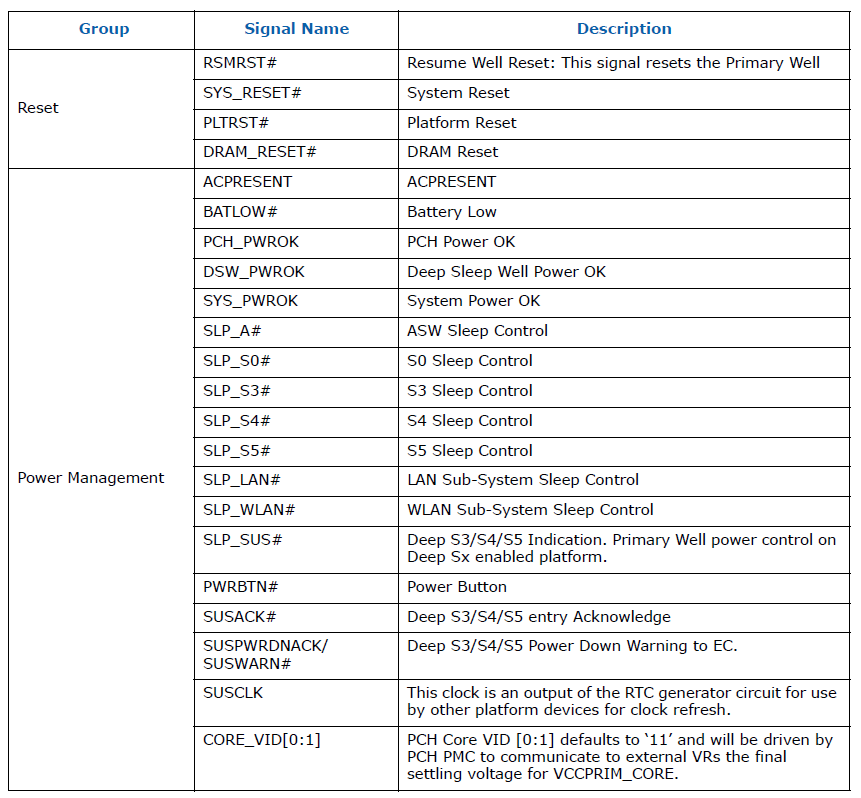

把VRMPWRGD更名为SYS_PWROK

Sequence:

1.插入3V 电池,通过LDO产生1.5V的VDDBT_RTC_G 给桥的RTC 电路供电

2.插入适配器或电池,经过隔离保护,产生公共点+VDC;

3.接着 产生EC待机供电,待机电压正常后EC给晶振供电产生EC待机时钟(也有免晶振的),待机供电延时产生EC待机复位,EC读取程序配置自身脚位;

(如果EC和BIOS Sharing SPI ROM则是EC复位后开启1.8A电压待EC读取程序配置自身脚位完成后,关闭1.8A。这是因为AMD FP5 APU espi接口只支持1.8V的电平 ‘’)

4.如果EC 检测到适配器,会自动发出EC_ALW_EN信号开启桥的待机供电(VDDIO_33_S,VDDCR_11_S等A电);

5.当桥的待机电压正常输出后外部电压调节器汇总产生ALW_PWRGD送给EC;

6.之后EC发送RSMRST#通知桥待机电压正常;

7.如果EC 检测不到适配器(电池模式),EC 需要收到开关触发信号后,才会开启桥待机供电,以节省电力;

8.按下开关,EC 收到高-低-高跳变的PWESW信号,延时并送给桥PWRBTN#脚;

9.桥的待机条件正常且收到PWRBTN#信号后,依次拉高SLP_S5#,SLP_S3#;

10.SLP_S5#控制产生内存主供电,SLP_S3#控制产生桥供电( 二级电压3.3V/5V/1.5V//1.8V/1.1V)CPU 多个供电);

.或者应EC做时序;SLP_S5#和SLP_S3#(RUN_ON)发给EC,再转出去控制内存供电和桥供电( 二级电压3.3V/5V/1.5V//1.8V/1.1V)CPU 多个供电);

11.内存VDDIO电压正常输出后反馈一个VRAM_PWRGD给EC,EC发出RUN_ON产生S0电(non-CORE);

12.S0(non-CORE)电压产生后,通过外部线路反馈一个ALL_SYS_PWRGD(MAIN_PWROK ),或者再发出RUN_ON就直接EC内部延迟在发送APU_PWR_EN。

13.CPU供电正常后(此时CPU为固定电压0.8-1.1V带SVID通讯成功后再动态变化), 最终汇总产生SYS_PWROK给桥PWR_GOOD脚;

14.南桥收到SYS_PWROK和48M 晶振都正常后,产生CLK_P/N时钟,时钟产生大一1ms后;PCH发PWROK(PWROK就是PCH发送给CPU的RESET_L,CPU和南北桥集合成的APU在内部进行不用管)给PMIC的PWROK pin脚 (同时这个这个引脚也送给EC,作用待定),PMIC芯片收到PWROK后,才启用SVID解码器,开始执行CPU发来的SVID信号,RT3662AC正常解码SVID信号后,Vcore电压稍微下降开始动态变化。

PWROK:是一个输出信号,用于标明内部PLL已经被锁,并且ALL POWER平面已经被激活和system clock产生器的电已经被供电和运行一毫秒。

LDT_PWROK:LDT_PWROK is a power good signal to drive PWROK for reset sequence

15.桥发出PLT_RST#,PCIE_RST#

16.桥发出APU_RST#(LDT_RST#)给CPU

intel:新平台时序信号名称更新:

1、增加了VCCDSW3_3、DPWROK、SLP_SUS#,用于支持深度睡眠,但大部分机器不采用

2、增加了SLP_M#(从ICH8开始就增加了),用于控制ME模块供电,但大部分机器不采用

3、增加了SLP_LAN#,用于控制网卡的供电(跟随SLP_M#的状态)

4、增加了VCCME,给ME模块供电,1.05V(不支持AMT时,VCCME与总线供电是一起的)

5、SLP_M#更名为SLP_A#

6、VCCME更名为VCCASW

7、CPU供电时序推后了,它是在CPU得到PROCPWRGD后,发出SVID控制产生

6、桥发出PWROK的条件:供电正常、PWROK正常、时钟正常、能正确读取BIOS

7、取消了PCIRST#,桥只发出PLTRST#

8、集显供电一般是需要在跑码之后,过了内存才会产生

9、ALL_SYSTEM_PWRGD:由DDR_PWRGD SUS_PWRGD 1.05VPWRGD 1.5V_PWRGD PWR_OK_VGA逻辑相与产生,信号有效时代表所有系统电压电源好

10、CLK_PWRGD:在南桥内存SLP_S3#与VRMPWRGD信号逻辑相与产生CLK_PWRGD至时钟IC,用于开启时钟信号

11、H_CPURST#:北桥收到PLTRST#信号后发出H_CPURST#至CPU

12、把VRMPWRGD更名为SYS_PWROK(VRMPWRGD就是指Vcore电压调节器OK)

13、增加了MEPWROK(ICH时叫CLPWROK),不支持AMT的时候,MEPWROK会跟PWROK连一起

AMD移动FP5平台时序解释的更多相关文章

- [转帖]AMD第三代锐龙处理器首发评测:i9已无力招架

AMD第三代锐龙处理器首发评测:i9已无力招架 Intel 从之前的 CCX 到了 CCD 增加了缓存 改善了 ccx 之间的延迟. https://baijiahao.baidu.com/s?id= ...

- JavaSript模块规范 - AMD规范与CMD规范介绍

JavaSript模块化 在了解AMD,CMD规范前,还是需要先来简单地了解下什么是模块化,模块化开发? 模块化是指在解决某一个复杂问题或者一系列的杂糅问题时,依照一种分类的思维把问题 ...

- AMD与CMD(转载)

JavaSript模块化 在了解AMD,CMD规范前,还是需要先来简单地了解下什么是模块化,模块化开发? 模块化是指在解决某一个复杂问题或者一系列的杂糅问题时,依照一种分类的思维把问题 ...

- JavaSript模块规范 - AMD规范与CMD规范介绍(转)

JavaSript模块规范 - AMD规范与CMD规范介绍 JavaSript模块化 在了解AMD,CMD规范前,还是需要先来简单地了解下什么是模块化,模块化开发? 模块化是指在解决某一个复杂问题或者 ...

- 微信平台ASPX高级定制开发(一):如何使用C#建立响应微信接入和自动回复的代码

微信平台不解释了,如果不了解的百度一下下,如果不会用微信,请自宫,光盘重启电脑,打开CMD输入Format C:.网上有很多针对企业级的高级定制ASPX开发,写得草草了事,很多男人干事都草草了事,这可 ...

- JavaSript模块化-AMD规范与CMD规范

JavaScript模块化 在了解AMD,CMD规范前,先来简单地了解下什么是模块化,模块化开发. 模块化是指在解决某一个复杂问题或者一系列的杂糅问题时,依照一种分类的思维把问题进行系统性的分解以之处 ...

- js模块化AMD/CMD

JavaSript模块化 在了解AMD,CMD规范前,还是需要先来简单地了解下什么是模块化,模块化开发? 模块化是指在解决某一个复杂问题或者一系列的杂糅问题时,依照一种分类的思维把问题进行系统 ...

- JavaSript模块规范 - AMD规范与CMD规范介绍 (转载lovenyf.blog.chinaunix.net)

JavaSript模块化 在了解AMD,CMD规范前,还是需要先来简单地了解下什么是模块化,模块化开发? 模块化是指在解决某一个复杂问题或者一系列的杂糅问题时,依照一种分类的思维把问题 ...

- APU平台DirectX 12性能测试:超级大惊喜!

APU平台DirectX 12性能测试:超级大惊喜! 转自:http://www.ithome.com/html/digi/129840.htm [size=1pc]微软将会在接下来的GDC 2015 ...

随机推荐

- 九度oj 题目1513:二进制中1的个数

题目描述: 输入一个整数,输出该数二进制表示中1的个数.其中负数用补码表示. 输入: 输入可能包含多个测试样例. 对于每个输入文件,第一行输入一个整数T,代表测试样例的数量.对于每个测试样例输入为一个 ...

- [luoguP1251] 餐巾计划问题(费用流)

传送门 模型 网络优化问题,用最小费用最大流解决. 实现 把每天分为二分图两个集合中的顶点Xi,Yi,建立附加源S汇T. 1.从S向每个Xi连一条容量为ri,费用为0的有向边. 2.从每个Yi向T连一 ...

- 刷题总结——湫湫系列故事——设计风景线(hdu4514 并差集判环+树的直径)

题目: 随着杭州西湖的知名度的进一步提升,园林规划专家湫湫希望设计出一条新的经典观光线路,根据老板马小腾的指示,新的风景线最好能建成环形,如果没有条件建成环形,那就建的越长越好. 现在已经勘探 ...

- 刷题总结——分糖(ssoj 容斥原理+逆元+快速幂+组合数求插板)

题目: 题目描述 有 N 个(相同的)糖果,M 个(不同的)小朋友.M 和 N 满足:1≤M≤N≤100000(105).要求:1.每个小朋友都至少有一个糖果.2.不存在正整数 X(X>=2), ...

- [USACO13JAN] Cow Lineup (单调队列,尺取法)

题目链接 Solution 尺取法板子,算是复习一波. 题中说最多删除 \(k\) 种,那么其实就是找一个颜色种类最多为 \(k+1\) 的区间; 统计一下其中最多的颜色出现次数. 然后直接尺取法,然 ...

- java面试题之BIO、NIO、AIO的应用场景

定义: 1.BIO:同步并阻塞,服务器实现模式为一个连接一个线程,即客户端有连接请求时,服务器就启动一个线程来处理,如果这个连接不处理任何事情会造成不必要的线程开销,可以通过线程池机制改善. 2.NI ...

- UVa12333 Revenge of Fibonacci

高精度 trie 暴力预处理出前100000个fibonacci数,将每个数的前40位数字串插入到trie中,记录每个结点最早可以由哪个数字串到达. 然后依次回答询问即可. 存fibonacci数的数 ...

- CodeForces 232E.Quick Tortoise

John Doe has a field, which is a rectangular table of size n × m. We assume that the field rows are ...

- poj 3204(最小割--关键割边)

Ikki's Story I - Road Reconstruction Time Limit: 2000MS Memory Limit: 131072K Total Submissions: 7 ...

- Codeforces 919 B. Perfect Number

B. Perfect Number time limit per test 2 seconds memory limit per test 256 megabytes input standa ...