FPGA等占空比奇偶分频和半整数分频

1. 偶数分频比较简单,如果分频系数是N(如果N是偶数,那么N/2是整数),那么在输入时钟的每隔N/2个周期时(计数器从0到N/2-1),改变输出时钟的电平即可得到50%固定占空比的时钟。需要的代码如下

module even(clk_in,clk_out,rst_n);

input clk_in;

input rst_n;

output clk_out; parameter N=; reg [:] cnt;

reg clk_out; always @(posedge clk_in or negedge rst_n) begin

if(!rst_n) begin

cnt<='b0000;

clk_out<=;

end

else if(cnt==(N/-)) begin

clk_out<=~clk_out;

cnt<='b0000;

end else cnt<=cnt+;

end

endmodule

2. 如果N是奇数,那么N/2非整数,使用2个寄存器,分别用上升沿寄存器计数到(N-1)/2-1电平翻转信号A,再计数到N-1电平翻转信号A,再用下降沿寄存器计数到(N-1)/2-1电平翻转信号B,再计数到N-1电平翻转信号B,,得到两个波形A和B,然后A和B相或即可,代码如下:

module div3(clk,clk_out,rst_n);

input clk,rst_n;

output clk_out; reg [:] cnt_p,cnt_n;

reg clk_p,clk_n;

parameter N=; always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_p<='h0;

else if(cnt_p==N-)

cnt_p<=;

else cnt_p<=cnt_p+;

end always @(negedge clk or negedge rst_n) begin

if(!rst_n)

cnt_n<='h0;

else if(cnt_n==N-)

cnt_n<=;

else cnt_n<=cnt_n+;

end always @(posedge clk or negedge rst_n) begin

if(!rst_n)

clk_p<=;

else if(cnt_p==(N-)/-)

clk_p<=~clk_p;

else if(cnt_p==(N-))

clk_p<=~clk_p;

end always @(negedge clk or negedge rst_n) begin

if(!rst_n)

clk_n<=;

else if(cnt_n==(N-)/-)

clk_n<=~clk_n;

else if(cnt_n==(N-))

clk_n<=~clk_n;

end

assign clk_out=clk_n|clk_p;

endmodule

仿真截图如下

3. 半整数分频,本次以2.5分频为例子

//===========================================================

// Author: seuchenrui@126.com

//

// Description:

// This is a simple verilog code for clock frequency division

// this code can be used to get

// 1. divided by 2.5

//===========================================================

module iCLK_div_shift_register_25

(

input iCLK,

input iRESET,

output oCLK

); wire [:] tmp_shift; reg tmp_0_;

reg tmp_2_;

reg tmp_3_; reg [:] tmp;

assign tmp_shift = 'b0_0001; always@(posedge iCLK or negedge iRESET)

begin

if(!iRESET)

tmp<=tmp_shift;

else

tmp<={tmp[:], tmp[]};

end always@(negedge iCLK or negedge iRESET)

begin

if(!iRESET)

tmp_0_<='b0;

else

tmp_0_<=tmp[];

end always@(negedge iCLK or negedge iRESET)

begin

if(!iRESET)

tmp_2_<='b0;

else

tmp_2_<=tmp[];

end always@(negedge iCLK or negedge iRESET)

begin

if(!iRESET)

tmp_3_<='b0;

else

tmp_3_<=tmp[];

end assign oCLK = tmp[]|tmp[]|tmp_0_|tmp_2_|tmp_3_|tmp[]; endmodule

3. 半整数分频,这个主要是利用时钟的上升沿和下降沿进行计数。不过分出来的占空比不是50%。问题在于如果被分的时钟不是50%占空比,那么按照下面出来的时钟频率还对吗?不对。

//2.5分频 module div_5(clk,clk_div, rst, temp_out1, temp_out2);//N+0.5

input clk;

input rst;

output clk_div;

reg [:] cnt1,cnt2;

//output reg temp1,temp2;

reg temp1,temp2;

output temp_out1, temp_out2;

parameter N = ; //设定分频系数为N+0.5

reg start_negedge;

//inital语句不可被综合

//initial

//begin

// temp1=0;temp2=1;

//end //首先进行初始化,temp1=0;temp2=1 //所有的判断信号都要写入 always @(posedge clk or negedge rst) //temp1上升沿跳变

begin if(!rst)

begin

cnt1<='b0;

temp1<=;

start_negedge <= ;

end else begin if(cnt1 == *N)

begin cnt1<='b0;end else begin cnt1 <= cnt1 + 'b1;end if(cnt1=='b0) begin temp1<=1; start_negedge <= 1;end //高电平时间为N+1;

else if(cnt1==N+) begin temp1<=;end //低电平时间为N;

end end always@(negedge clk or negedge rst) //temp2下降沿跳变

begin

if(!rst)

begin

cnt2<='b0;

temp2<=; end

else if(start_negedge == )

begin

cnt2<='b0;

temp2<=; end

else begin if(cnt2==*N) //2*N

begin cnt2<='d0;end

else begin cnt2<=cnt2+'d1;end

if(cnt2=='d0) begin temp2<=0;end //低电平时间为N;

else if(cnt2==N) begin temp2<=;end //高电平时间为N+1;

end end assign clk_div=temp1&temp2; //逻辑与

assign temp_out1 = temp1;

assign temp_out2 = temp2;

endmodule

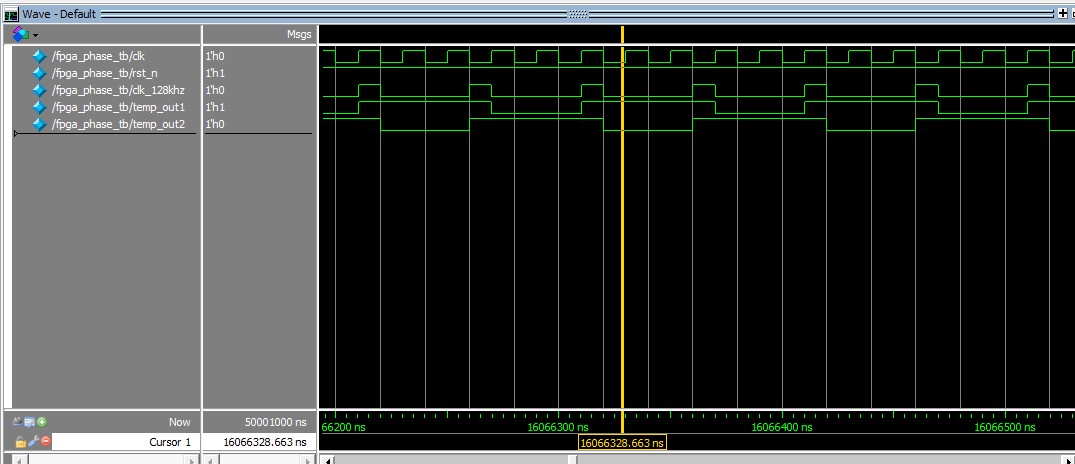

仿真截图如下

FPGA等占空比奇偶分频和半整数分频的更多相关文章

- 基于Verilog的偶数、奇数、半整数分频以及任意分频器设计

在FPGA的学习过程中,最简单最基本的实验应该就是分频器了.由于FPGA的晶振频率都是固定值,只能产生固定频率的时序信号,但是实际工程中我们需要各种各样不同频率的信号,这时候就需要对晶振产生的频率进行 ...

- 基于verilog的分频器设计(半整数分频,小数分频:下)

第二种方法:对进行奇数倍n分频时钟,首先进行n/2分频(带小数,即等于(n-1)/2+0.5),然后再进行二分频得到.得到占空比为50%的奇数倍分频.下面讲讲进行小数分频的设计方法. 小数分频:首先讲 ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

- 关于分频器的FPGA实现整理思路

分频器是用的最广的一种FPGA电路了,我最初使用的是crazybingo的一个任意分频器,可以实现高精度任意分频的一个通用模块,他的思想在于首先指定计数器的位宽比如32位,那么这个计数器的最大值就是2 ...

- FPGA数字鉴相鉴频器的开发记录

1. 对于电机的锁相控制,需要对相差进行PI性质的环路滤波,但现有的锁相环中鉴频鉴相器输出为相差脉冲而非数字量,难以直接进行PI特性的环路滤波. 通过对晶振的非整数分频获取准确的参考时钟,基于触发器机 ...

- FPGA奇数分频

在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2.4.8.16.32.64等这些以2的整数倍的. 这里说的是奇数倍分频,如时钟是100MH ...

- FPGA三分频,五分频,奇数分频

我们在做FPGA设计时,有时会用到时钟频率奇数分频的频率,例如笔者FPGA的晶振为50M,当我们需要10M的时钟时,一种方式可以使用DCM或PLL获取,系统会内部分频到10M,但其实VERILOG内部 ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

随机推荐

- 高效实时的网络会议数据传输库—UDT

在视频会议系统的研发当中,我们的音.视频数据必须要有相应的可靠性作为保障,因为视频会议系统是一个实时性非常强的系统,如果其数据在网络不太好的情况下,有可能会出现丢包.数据延迟.数据堵塞等现象,出现这些 ...

- 三、HTTP协议

1. 基础概念篇 HTTP协议是Hyper Text Transfer Protocol(超文本传输协议)的缩写,是用于从万维网(WWW:World Wide Web )服务器传输超文本到本地浏览器的 ...

- PHP设计模式——装饰器模式

<?php /** * 装饰器模式 * 如果已有对象的部分内容或功能发生变化,但是不需要修改原始对象的结构,应使用装饰器模式 * * 为了在不修改对象结构的前提下对现有对象的内容或功能稍加修改, ...

- 2018.10.10 Java的The superclass "javax.servlet.http.HttpServlet" was not found on the Java Build Path 错误

我们在用Eclipse进行Java web开发时,可能会出现这样的错误:The superclass javax.servlet.http.HttpServlet was not found on t ...

- build.gradle中的dependencies

demo_myna中的build.gradle中的dependencies是依赖项目.比如之前开发的一个项目A,现在新的项目B要使用项目A的功能,那么把项目A作为类库关联进来,这样b就能直接使用A的功 ...

- 【题解】洛谷P2426删数

链接 https://www.luogu.org/problemnew/show/P2426 念念碎 第一次接触到区间DP(瑟瑟发抖) 所以象征性地看了一下题解 这好像是一道比较基础的区间DP吧 但是 ...

- FFMPEG系列一:Mac下FFMPEG编译安装配置及使用例子

系统环境:10.13以前系统版本,没有升级到macOS High Sierra.正常情况是直接输入brew install ffmpeg即可安装ffmpeg,但是该过程还是有一些坑需要填. 一.mac ...

- CentOS 7设置网卡开机自动启用

一.查看网卡配置 root权限 [root@dbsyn ~]# ip addr 1: lo: <LOOPBACK,UP,LOWER_UP> mtu 65536 qdisc noqueue ...

- TCP协议与UDP协议

网络通信协议规定了网络通信时,数据必须采用的格式.常见的协议有TCP协议,UDP协议. TCP协议 :(Transmission Control Protocol)传输控制协议. TCP是一种面向连接 ...

- 用HANA STADIO 开发ABAP程序

Help-->Install New Software-->ADD NAME: hana_on_mars Location: https://tools.hana.ondemand.com ...