FPGA多时钟处理应用

FPGA项目设计中,通常会遇到多时钟处理。即一个PLL输出多个时钟,根据条件选择合适的时钟用作系统时钟。

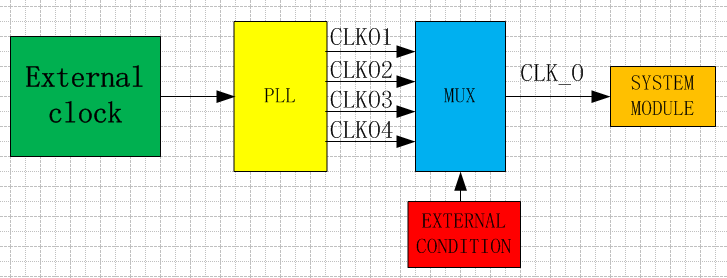

方案一:

外部晶振时钟进入PLL,由PLL输出多个时钟,MUX根据外部条件选择时钟输出做为系统使用。

方案在时钟频率比较低的情况下是可行的。设计时注意MUX使用组合逻辑实现的,注意case语句中default选项必须有输出,否则会出现锁存器。

当输出时钟频率较高时,这种方案的时序约束就比较麻烦。除了使用creat_clock命令约束PLL输入时钟,使用creat_generate_clock约束PLL输出时钟外,还要根据PLL输出的多个时钟之间的关系,使用set_clock_groups约束。set_clock_groups:

- asynchronous表示时钟同时有效,但没有相位关系。

- exclusive 表示时钟是互斥的

- group,group之内的时钟相关,group之间的时钟互不相关。

这种设计使得时钟约束变得繁琐,时序变得紧张。

同时PLL输出时钟后使用MUX进行选择输出,会增加时钟布线延时,高速情况下并不可靠。

时序是设计出来的,不是约束出来的。

设计出好的时序一般不需要约束。

方案二:

在高速情况下,应该更改设计,提高电路速度。ALTERA FPGA提供PLL重配功能。可根据条件对PLL进行重配。

调用ALTERA提供的PLL重配模块,根据官方资料,可以动态的对PLL重新配置。这样PLL输出时钟直接驱动系统模块,将多时钟域转换到单时钟域上。不需要添加附加约束电路都可以正常工作。

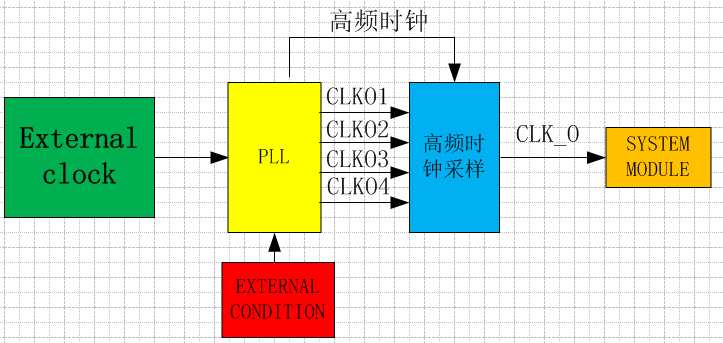

方案三:

第三种方案,这里稍微介绍一下。

PLL输出一个高频时钟HCLK,其他时钟作为HCLK的使能端,用HCLK采样其他时钟,这也是一个可以考虑的方案,这个方案也不会造成多时钟处理及约束。但此方案也有限制,要求HCLK时钟频率至少是PLL输出其他时钟最高频率的两倍以上,这样才能满足采样定理,即奈奎斯特定理。在时钟频率比较低时,亦可以考虑此方案。

文章来源:FPGA极客空间微信公众号

版权所有权归卿萃科技,转载请注明出处。

作者:卿萃科技ALIFPGA

原文地址:bbs.alifpga.com

扫描二维码关注FPGA极客空间。

FPGA多时钟处理应用的更多相关文章

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- FPGA跨时钟域握手信号的结构

FPGA跨时钟数据传输,是我们经常遇到的问题的,下面给出一种跨时钟握手操作的电路结构.先上图 先对与其他人的结构,这个结构最大的特点是使用 req 从低到高或者高到低的变化 来表示DIN数据有效并开始 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- FPGA 异步时钟处理方

1 假设FPGA设计,包括不同的频率的时钟,它会发出涉及异步时钟. 我们需要一些方法来使时钟同步,从而保证FPGA可靠性设计. 2 在建立和保持时间所构成的有效时间窗体内,数据输入到触发器进行转换. ...

- FPGA跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- 对FPGA的时钟资源理解(更新中)

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟.内部时钟进行处理,生成需要的低抖动时钟.PLL是MMCM的功能子集, ...

随机推荐

- .Net Mvc实现各种表格随意切换插件

一套Js代码,.只要改参数 在3种表格之间任意切换-(使用Js面向对象封装,可重写方法) 任意表格皮肤随便切换 flextgrid/bootstrapt/jqgrid 1 001 @{ 002 ...

- NET .NET深入体验和实战精要

在学习.NET之前要充分理解基础,在这里将基础的知识点一一列举. 万丈高楼平地起 1.命名空间 命名空间是一种特殊的分类机制,他将与一个特定功能集有关的所有类型都分到一起,是.避免类名冲突的一种方式 ...

- Spring Cloud在国内中小型公司能用起来吗?

今天吃完饭休息的时候瞎逛知乎,突然看到这个一个问题Spring Cloud在国内中小型公司能用起来吗?,吸引了我的注意.仔细的看了题主的问题,发现这是一个好问题,题主经过了一番思考,并且用图形全面的将 ...

- Jenkins关于tomcat地址和端口映射的配置

<?xml version='1.0' encoding='utf-8'?><!-- Licensed to the Apache Software Foundation (ASF) ...

- Mybatis源码解析-BoundSql

mybatis作为持久层,其操作数据库离不开sql语句.而BoundSql则是其保存Sql语句的对象 前提 针对mybatis的配置文件的节点解析,比如where/if/trim的节点解析可见文章Sp ...

- 团队作业4——第一次项目冲刺(Alpha版本)2017.4.24

在下午3-4节Linux课结束后,我们teamworkers全体队员留在禹州楼304进行约20分钟的短暂会议,会议讨论关于昨天任务的总结并分配了今天的新任务,大家畅所欲言,情绪高昂,各自阐述了自己不一 ...

- 201521123030《Java程序设计》第5周学习总结

1. 本周学习总结 1.代码阅读:Child压缩包内源代码 1.1 com.parent包中Child.java文件能否编译通过?哪句会出现错误?试改正该错误.并分析输出结果. 因为i在类中是priv ...

- 201521123020 《Java程序设计》第4周学习总结

本周学习总结 1.1 尝试使用思维导图总结有关继承的知识点. 1.2 使用常规方法总结其他上课内容. (1)类注释的使用方法是: /** *(要注释的内容) */ (2)学习了Object类,学会了覆 ...

- 201521123056 《Java程序设计》第13周学习总结

1. 本周学习总结 2. 书面作业 1. 网络基础 1.1 比较ping www.baidu.com与ping cec.jmu.edu.cn,分析返回结果有何不同?为什么会有这样的不同? 1.1 答: ...

- 201521123114《Java程序设计》第9周学习总结

1. 本章学习总结 2. 书面作业 Q1. 常用异常 题目5-1 1.1 截图你的提交结果(出现学号) 1.2 自己以前编写的代码中经常出现什么异常.需要捕获吗(为什么)?应如何避免? 经常出现的异常 ...