SPI接口扫盲 SPI定义/SPI时序(CPHA CPOL)

SPI接口扫盲

百度上找出来的SPI接口中文描述都说的太过简略,没有一篇文档能够详尽的将SPI介绍清楚的。wikipedia英文版[注释1]中,SPI接口介绍的很好,但是毕竟是英文版,读起来终究不如母语舒服,所以我结合自己的工作经验,对其进行了汉化、整理。

SPI接口是什么?

SPI ( Serial Peripheral Interface,串行外设接口)是一种同步、串行通讯接口规格,常用于短距离通讯,主要是在嵌入式系统中。此接口由Mototola公司推出,已成为一种事实标准(没有统一的协议规范,但是基于其广泛的使用,根据实际使用中大家通用的习惯形成了一个类似行规的标准)。

SPI典型的应用场景包括SD卡(SD接口中包含SPI接口)和液晶显示。

SPI是一种高速的,全双工,同步的通信总线。分为主(master)、从(slave)两种模式,一个SPI通讯系统需要包含一个(且只能是一个)maser(主设备),一个或多个slave(从设备)。

SPI接口的读写操作,都是由master发起。当存在多个从设备时,通过各自的片选(slave select)信号进行管理。

硬件开发人员设计、提供的SPI接口,其实只是一个数据读写通道 ,具体读写数据所代表的意义需要在应用中定义。不像SD接口那样,对于命令有着明确详细的定义。

SPI接口都包含哪些IO线?

除了供电、接地两个模拟连接以外,SPI总线定义四组数字信号:

注释:

SPI接口如何连接?

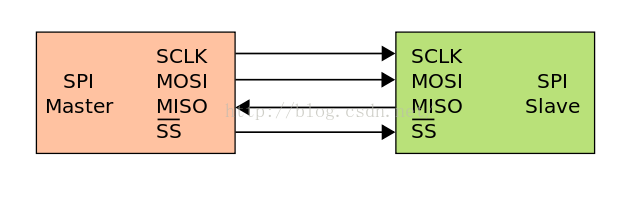

当只有一个maser、一个slave时,将master与slave上名字相同的4对接口两两互联,即可完成了接口的互联。如下图所示:

注释:

当存在一个master、多个slave时(注意,当master上有n个SS时,对应可以连接n个slave),连接方式如下图所示,注意SCLK/MOSI/MISO三个接口采取复用模式连接,不同SS单独连接对应的slave,SS信号绝不可复用:

SPI接口如何进行数据传输?

SPI接口是一种典型的全双工接口,通过同步时钟SCLK的脉冲将数据一位位地传送。所以在开始通讯前,master首先要配置接口时钟(确定其通讯频率是SLAVE可以支持的,通常为数兆赫兹)。

当MASTER片选一个SLAVE时,每向SLAVE发送一个周期的SCLK信号,都会有1bit的数据从MOSI发送至slave,与此同时,slave每收到一个周期的SCLK信号,都会从MISO向master发送1bit的数据。这种全双工通讯,是由硬件保证的(MASTER与HOST中各有一个移位寄存器作为收发数据的缓存)。

SPI是一个很开放的接口,指令解析、帧大小、LSB/MSB(Least Significant Bit/Most Significant Bit)等规则并没有一个完善的定义,不同的SPI设备在这些方面的定义会有不同:

不同于SD等接口的严谨的command定义,SPI接口的master与slave之间的命令、数据解析都可以自定义,只要保证master与slave之间采用相同的规则就好。

不同SPI芯片,每次连续传输的数据量的大小(取决于MASTER、SLAVE中缓存最小的那个)常常不同。当一次连续通讯的的数据量超过帧的大小时,会出现数据丢失的现象。所以,每完成1帧的传输后,MASTER会停止接口时钟输出,master、slave读取、处理收到的数据,然后进行下一帧的传输。

在SPI接口协议中,并没有中断的定义,但是实际应用中,我们可以使用接口中断提高接口通讯速度。比如SLAVE是负责数据数据加解密的,MASTER下发一组明文给SLAVE加密,如果此时有个SLAVE输出到MASTER的中断信号,那么MASTER可以清楚的知道何时SLAVE完成了数据处理并读出处理结果,不必通过查询一遍遍的等待结束。

SPI接口的变形

以上我们讲的SPI接口,一个时钟周期可以进行全双工的1bit数据通讯。实际应用中,如果对于全双工的需求不高,而且期望提高通讯速度的话,SPI有两种常见变形可供选用:

一、 两线模式的SPI

CLK与SS信号保持不变,MOSI与MISO则变形为DATA_0与DATA_1。

DATA_0与DATA_1是输入输出状态由MASTER配置的数据管脚:当MASTER打算向SLAVE中写数据时,处于输出状态;当MASTER打算从SLAVE读数据时,处于输入状态。

二、 四线模式的SPI

CLK与SS信号保持不变,MOSI与MISO删除,新增四条数据线DATA0~3。

DATA0_~3是输入输出状态由MASTER配置的数据管脚:当MASTER打算向SLAVE中写数据时,处于输出状态;当MASTER打算从SLAVE读数据时,处于输入状态。

这样一来,大大提高了单方向上数据传输的速度,但是增加了接口资源的开销。

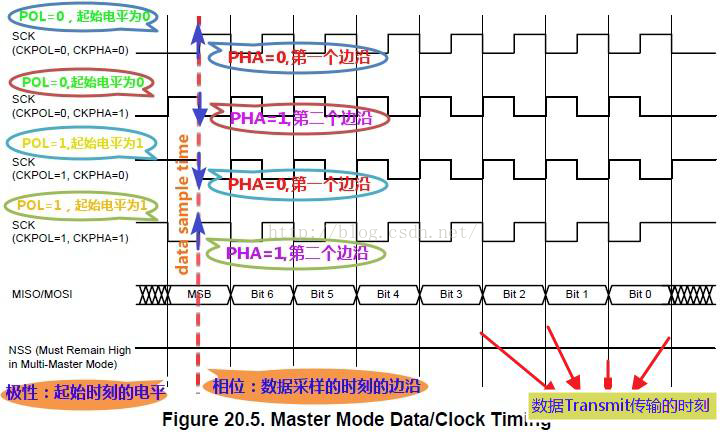

由于SPI缺乏一个统一的规范,所以在时序描述上存在一定的差异性。CPOL与CPHA的定义,有些芯片DATASHEET中描述与通用的规则是相反的,所以选型时候一定要以DATASHEET中的时序图为准。

另外,某些芯片上,关于SPI接口时序不使用CPOL/CPHA进行定义,而是使用CKP和CKE进行定义,在此不再详细解释这两个概念的意义(比较绕,这些参数看多了特容易混淆),建议直接参考时序图。

关于SPI时序的说明,之前我参考了crifan的博客,其中还有个问题待解决:

对于CPOL和CPHA这四种模式,不同的模式之间,相对来说有何优缺点,比如是否哪种模式更稳定,数据更不容易出错等等,还是不清楚。

我这里给出我的思考结果:

首先是CPOL的选择,我们从芯片设计角度开始谈这个问题。首先,如果寄存器赋值时没有特殊要求必须是下降沿触发赋值时,我们会选择上升沿触发,且时钟关闭时固定为低电平。这样一来,保证了时钟关闭时漏电最小(低电平下没有电压差,减小了漏电流IDDQ,同时上升沿触发也保证了来了时钟能够立刻采样信号,快速响应)。当然了,如果要求寄存器下降沿采样,那么时钟关闭时固定为高电平了。

借用此思想,对于CPOL的选择,如果配置可以选择的话,我建议参考MASTER与SLAVE接口IO的配置参数。如果两边都是上拉,那么建议选择CPOL为1,这样一来,当我们配置CPOL时,不会在接口上制造出一个下降沿(单SLAVE的应用场景下,SLAVE的片选有时会直接连接GND,而此时MASTER本不想通讯但是传入了一个下降沿,SLAVE那边区分不出来这是不是有效通讯);而且这样在IO上的漏电也能有效控制(没有电势差,没有电流)。如果一边上拉一边下拉,如果从功耗的角度考虑,建议选择下拉电阻更小(漏电流更大)的IO的上下拉配置进行CPOL赋值。

关于CPHA的选择,我个人更倾向于使用CPHA配置为1的状态。此配置下,第一个时钟沿驱动数据数据输出,第二个时钟沿驱动数据采样,比较符合硬件上的使用习惯。

当然了,这都是纸上谈兵,很多时候时序类型的选择还要结合芯片硬件条件、功能实现需求等问题考虑。

注释1:维基百科上SPI接口的详细描述http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus

SPI接口扫盲 SPI定义/SPI时序(CPHA CPOL)的更多相关文章

- 嵌入式物联网之SPI接口原理与配置

本实验采用W25Q64芯片 W25Q64是华邦公司推出的大容量SPI FLASH产品,其容量为64Mb.该25Q系列的器件在灵活性和性能方面远远超过普通的串行闪存器件.W25Q64将8M字节的容量分为 ...

- SPI、I2C、UART三种串行总线协议的区别和SPI接口介绍(转)

SPI.I2C.UART三种串行总线协议的区别 第一个区别当然是名字: SPI(Serial Peripheral Interface:串行外设接口); I2C(INTER IC BUS) UART( ...

- STC8A8K64S4A12通过SPI接口操作基于ST7920的LCD12864液晶模块

文章地址:https://www.cnblogs.com/jqdy/p/12665430.html 1. 硬件连接 1.1 64引脚的STC8A8K64S4A12 使用的是最小核心板,所以引脚皆引出可 ...

- 国产CPLD(AGM1280)试用记录——做个SPI接口的任意波形DDS [原创www.cnblogs.com/helesheng]

我之前用过的CPLD有Altera公司的MAX和MAX-II系列,主要有两个优点:1.程序存储在片上Flash,上电即行,保密性高.2.CPLD器件规模小,成本和功耗低,时序不收敛情况也不容易出现.缺 ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- flash读写学习笔记与spi接口及简单测试验证(三)

FPGA中的视频图像资源,以及想要永久存储的程序都是要存储在flash中,flash是FPGA一个不可缺少的部分,flash的种类有很多,根据winbond公司的128Mbit Qual SPI接口的 ...

- Blackfin DSP(五):BF533的SPI接口

533SPI的特性 最高速度可达SCLK/4: 支持主模式和从模式: 可使用8个GPIO口作为从选择线: 1 slave select input pins 7 slave select output ...

- [转载]Linux驱动-SPI驱动 之二:SPI通用接口层

通过上一篇文章的介绍,我们知道,SPI通用接口层用于把具体SPI设备的协议驱动和SPI控制器驱动联接在一起,通用接口层除了为协议驱动和控制器驱动提供一系列的标准接口API,同时还为这些接口API定义了 ...

- NUC980 运行 RT-Thread 驱动 SPI 接口 OLED 播放 badapple

badapple 是什么,上网随便查了下,没看出个究竟,不过有个关于这个挺火的标签或者主题 < 有屏幕的地方就有 badapple >,网上有很多人用很多方式播放 badapple 动画, ...

随机推荐

- ASP.NET Core 2.1 源码学习之 Options[2]:IOptions

在 上一章 中,介绍了Options的注册,而在使用时只需要注入 IOption<T> 即可: public ValuesController(IOptions<MyOptions& ...

- Mongodb副本集+分片集群环境部署记录

前面详细介绍了mongodb的副本集和分片的原理,这里就不赘述了.下面记录Mongodb副本集+分片集群环境部署过程: MongoDB Sharding Cluster,需要三种角色: Shard S ...

- 最小生成树模板题POJ - 1287-prim+kruskal

POJ - 1287超级模板题 大概意思就是点的编号从1到N,会给你m条边,可能两个点之间有多条边这种情况,求最小生成树总长度? 这题就不解释了,总结就算,prim是类似dijkstra,从第一个点出 ...

- Scrum Meeting 5

第五次会议 No_00:工作情况 No_01:任务说明 待完成 已完成 No_10:燃尽图 No_11:照片记录 待更新 No_100:代码/文档签入记录 No_101:出席表 ...

- Java 类的加载

package com.cwcec.p2; class C { public static final int SIZE; static { SIZE = 100; System.out.printl ...

- 在Windows Server 2008R2中部署 AspNetCore

1.部署时,先安装运行时 https://dotnet.microsoft.com/download 2.安装vc_redist.x64 https://www.microsoft.com/en- ...

- ACL访问控制

/etc/squid/squid.conf 定义语法: acl aclname acltype string acl aclname acltype "file" s ...

- 第五届蓝桥杯C++B组 地宫取宝

代码: #include <bits/stdc++.h> using namespace std; #define ll long long const ll mod = 1e9 + 7; ...

- LY tomcat 的闪退问题

http://www.cnblogs.com/1693977889zz/archive/2018/04/06/8726920.html 在bin文件夹里打开此文件setclasspath.bat 举例 ...

- SQL 中GO的作用

use db_CSharp go select *, 备注=case when Grade>= then '成绩优秀' when Grade< and Grade>= then '成 ...