MIPS指令的CPU实现:ALU设计

设计CPU的第一步,设计一个简单的逻辑运算单元ALU。同时对Verilog语言也有一定要求。

一、实验内容

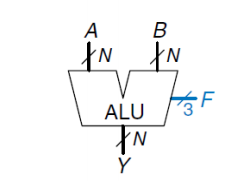

- 如图,ALU接受两个N位的输入,得到N位的输出,通过控制信号F决定运算功能。

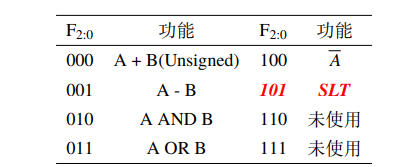

- 将ALU的输出结构与七段数码管显示模块连接,使用实验配置的NEXYS4开发板。

结构如下:

- 编写顶层模块top连接上述模块。

- 仿真,编写约束文件,生成二进制文件,在开发板上验证。

整体难度不大,主要任务就是编写ALU和top,以及约束文件。

但是这学期之前在摸鱼,这个小实验都没认真弄好。。。地基打不好,CPU肯定写不出来啊。

二、RTL级的部分Verilog代码,也是重点部分

ALU.v

真的很简单,方法两种,一种是always逻辑,一种是assign逻辑。

- always:

module ALU(

input wire [31:0] A,

input wire[31:0] B,

input wire [2:0] OP, // 输入用wire

output reg [31:0] F //输出用寄存器reg

);

always @(*) begin

case(OP)

3'b000: begin F <= A + B; end //这里实际上连进位都没有考虑

3'b001: begin F <= A - B; end

3'b010: begin F <= A & B; end

3'b011: begin F <= A | B; end

3'b100: begin F <= ~A; end

3'b101: begin F <= A<B; end

default: begin F <= 0; end

endcase

end

endmodule

- assign:

assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,所以赋值的类型应用wire。

module ALU(

input wire [31:0] A,

input wire[31:0] B,

input wire [2:0] OP,

output wire [31:0] F

);

assign F = (OP == 3'b000) ? A + B:

(OP == 3'b001) ? A + B:

(OP == 3'b010) ? A + B:

(OP == 3'b011) ? A + B:

(OP == 3'b100) ? A + B:

(OP == 3'b101) ? A + B:

32'b0;

endmodule

数码管显示模块display.v和seg7.v(实验提供)

- display.v

module display(

input wire clk,reset,

input wire [31:0]s,

output wire [6:0]seg,

output reg [7:0]ans

);

reg [20:0]count;

reg [4:0]digit;

always@(posedge clk,posedge reset)

if(reset)

count = 0;

else

count = count + 1;

always @(posedge clk)

case(count[20:18])

0:begin

ans = 8'b11111110;

digit = s[3:0];

end

1:begin

ans = 8'b11111101;

digit = s[7:4];

end

2:begin

ans = 8'b11111011;

digit =s[11:8];

end

3:begin

ans = 8'b11110111;

digit = s[15:12];

end

4:begin

ans = 8'b11101111;

digit = s[19:16];

end

5:begin

ans = 8'b11011111;

digit = s[23:20];

end

6:begin

ans = 8'b10111111;

digit =s[27:24];

end

7:begin

ans = 8'b01111111;

digit = s[31:28];

end

endcase

seg7 U4(.din(digit),.dout(seg));

endmodule

- seg7.v

module seg7(

input wire [3:0]din,

output reg [6:0]dout

);

always@(*)

case(din)

5'h0:dout = 7'b000_0001;

5'h1:dout = 7'b100_1111;

5'h2:dout = 7'b001_0010;

5'h3:dout = 7'b000_0110;

5'h4:dout = 7'b100_1100;

5'h5:dout = 7'b010_0100;

5'h6:dout = 7'b010_0000;

5'h7:dout = 7'b000_1111;

5'h8:dout = 7'b000_0000;

5'h9:dout = 7'b000_0100;

5'ha:dout = 7'b000_1000;

5'hb:dout = 7'b110_0000;

5'hc:dout = 7'b011_0001;

5'hd:dout = 7'b100_0010;

5'he:dout = 7'b011_0000;

5'hf:dout = 7'b011_1000;

default:dout = 7'b111_1111;

endcase

endmodule

top.v

module top(

input wire clk, rst,

output wire[6:0] seg,

output wire[7:0] ans,

input wire [2:0] op,

input wire [7:0] num_1

);

wire [31:0] f; // f从ALU传给display

ALU U1(.A({24'b0,num_1}),.B(32'h1),.OP(op),.F(f)); // 输入a为8位扩充至32位,b为固定值32'h1

display U2(.clk(clk),.reset(rst),.s(f),.ans(ans),.seg(seg));

endmodule

三、存在的问题

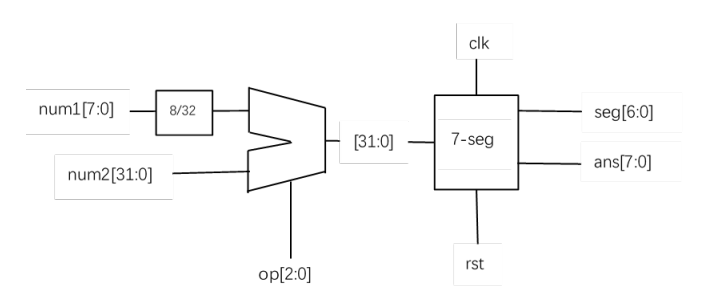

- 仿真测试中得不到结果,但是下到板子上以后能正常运行

test文件:

module test();

reg [7:0] num_1;

reg [2:0] op;

wire [6:0]seg;

wire [7:0]ans;

reg clk,rst;

always #25 clk = ~clk;

initial begin

clk = 1;

rst = 0;

num_1 = 8'h 11;

op = 3'b 111;

# 100 op = 3'b 000;

# 100 op = 3'b 001;

# 100 op = 3'b 010;

# 100 op = 3'b 011;

# 100 op = 3'b 100;

# 100 op = 3'b 101;

end

top x(

.clk(clk),

.rst(rst),

.seg(seg),

.ans(ans),

.num_1(num_1),

.op(op)

);

endmodule

MIPS指令的CPU实现:ALU设计的更多相关文章

- 自己动手写CPU之第五阶段(3)——MIPS指令集中的逻辑、移位与空指令

将陆续上传本人写的新书<自己动手写CPU>(尚未出版),今天是第17篇.我尽量每周四篇 5.4 逻辑.移位操作与空指令说明 MIPS32指令集架构中定义的逻辑操作指令有8条:and.and ...

- 16位CPU多周期设计

16位CPU多周期设计 这个工程完成了16位CPU的多周期设计,模块化设计,有包含必要的分析说明. 多周期CPU结构图 多周期CPU设计真值表 对应某一指令的情况,但仅当对应周期时才为对应的输出,不是 ...

- verilog实现的16位CPU单周期设计

verilog实现的16位CPU单周期设计 这个工程完成了16位CPU的单周期设计,模块化设计,包含对于关键指令的仿真与设计,有包含必要的分析说明. 单周期CPU结构图 单周期CPU设计真值表与结构图 ...

- 3.6 MIPS指令简介

计算机组成 3 指令系统体系结构 3.6 MIPS指令简介 MIPS秉承着指令数量少,指令功能简单的设计理念.那这样的设计理念是如何实现的呢?在这一节,我们就将来分析MIPS指令的特点. 相比于X86 ...

- MIPS指令 MIPS架构

华中科技大学 - 计算机组成原理 华中科技大学 - 计算机硬件系统设计 Microprocessor without Interlocked Pipleline Stages 无内部互锁流水级的微处理 ...

- verilog简易实现CPU的Cache设计

verilog简易实现CPU的Cache设计 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4661147.html所增加的Cache,相同的内容就不重复写了 ...

- QtSpim实现MIPS指令的编写

QtSpim实现MIPS指令的编写 由于各种对齐问题,cnblogs的格式难以控制,故贴图片,谅解.

- MIPS指令学习二

1.MIPS寻址方式 MIPS架构的寻址模式有寄存器寻址.立即数寻址.寄存器相对寻址和PC相对寻址4种,其中寄存器相对寻址.PC相对寻址介绍如下: 1.1.寄存器相对寻址 这种寻址模式主要被加载/存储 ...

- P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2.p3.p4.p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽 ...

随机推荐

- Ambassador-07-熔断

Ambassador的熔断机制的定义 circuit_breakers: - priority: <string> max_connections: <integer> max ...

- (十八)VMware Harbor 镜像同步

为什么需要镜像同步 由于对镜像的访问是一个核心的容器概念,在实际使用过程中,一个镜像库可能是不够用的,下例情况下,我们可能会需要部署多个镜像仓库: 国外的公有镜像下载过慢,需要一个中转仓库进行加速 容 ...

- 网络编程Netty IoT百万长连接优化

目录 IoT推送系统 IoT是什么 IoT推送系统的设计 心跳检测机制 简述心跳检测 心跳检测机制代码示例 百万长连接优化 连接优化代码示例 TCP连接四元组 配置优化 IoT推送系统 IoT是什么 ...

- .NET Core - 自定义项目模板

前言: 前面介绍 自定义项目模板 中介绍了一种简单的方式--通过创建项目导出为项目模板方式实现.本次将采用dotenet cil(手脚架)来创建项目模板. 那么,我们首先看下当前dotnet 支持的项 ...

- 模拟退火算法(1)Python 实现

1.模拟退火算法 模拟退火算法借鉴了统计物理学的思想,是一种简单.通用的启发式优化算法,并在理论上具有概率性全局优化性能,因而在科研和工程中得到了广泛的应用. 退火是金属从熔融状态缓慢冷却.最终达到能 ...

- 1036 Boys vs Girls

This time you are asked to tell the difference between the lowest grade of all the male students and ...

- 04- HTML常用标签

HTML标签分类 通过上节博客我们知道了网页的组成:文字 图片 连接 视频 音频.在HTML页面中,带有"< >"符号的元素被称为HTML标签,如上面提到的 <H ...

- 04- cookie与缓存技术

什么是cookie 定义:Cookies是一种能够让网站服务器把少量数据储存到客户端的硬盘或内存,或是从客户端的硬盘读取数据的一种技术.Cookies是当你浏览某网站时,由Web服务器置于你硬盘上的一 ...

- 分享几个网址二维码生成api

分享几个网址二维码生成api 传入网址参数,或许二维码图片,扫二维码能直接跳转网址 http://b.bshare.cn/barCode?site=weixin&url=https://www ...

- yapi简介,安装及使用

简介 YApi 是高效.易用.功能强大的 api 管理平台,旨在为开发.产品.测试人员提供更优雅的接口管理服务.可以帮助开发者轻松创建.发布.维护 API,YApi 还为用户提供了优秀的交互体验, ...