P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2、p3、p4、p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽快调整状态,下决心只要学不死,就往死里学,尽快迎头赶上鸭!!

由于p4断断续续做的,现在临考前来总结一下p4,顺便恢复一下记忆,对Verilog命名规范、p4设计CPU技巧、实现细节等等进行初步总结,如有不对烦请指正。

一、Verilog设计单周期CPU流程

由于p3和理论部分我们已经掌握了单周期CPU的理论知识,也对CPU的实现有形象化的认识。我们要做的就是“翻译”一遍。

我主要是先设计CPU文档,再用Verilog描述CPU。

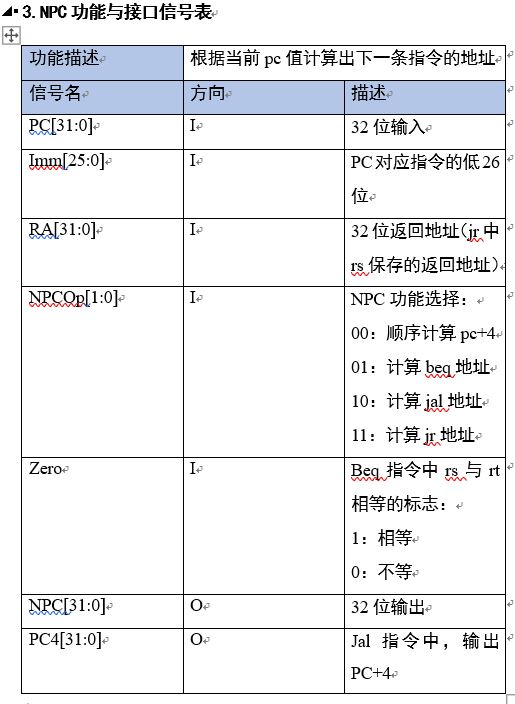

1.画出各个部件的端口及功能定义表,定义各个基础部件的端口,描述部件的功能。在这里我们不需要考虑部件功能的实现细节,只需要遵循高内聚低耦合的特点划分部件,将各个部件的功能描述清楚就可以了。

关于部件的划分,在这里我主要遵循高小鹏老师的《计算机组成与实现》,单独设计了NPC组合逻辑部件,将求beq,jal等跳转指令的地址都放到这里来,我认为在设计单周期CPU时会显得更加清晰,不容易出错。

关于各个部件的命名规范,我稍后再提。

大概表头设计如下:

2.设计各条指令的数据通路,同时修正扩展第一步中相应模块的端口和功能。

在这里其实理论上可以建一个以指令为列各个部件端口为行的表格,但我最初是在word里画的,所以把他拆分成了各个部件。

表头列出单个部件的信号端口(输入端)和驱动源(其他部件的输出端),各条指令,我称之为数据综合表:

由图所示,表头设计好了,需要的做的只是按照每一条指令数据通路进行填空而已,在这个过程中,如果需要对部件端口功能进行修改扩展则及时修改扩展。

填表的过程就相当于在logisim中连线,这样就不要照着图就能设计出Verilog描述的CPU了。

注意:端口名称需要严格按照之前表格里的名称来写,方便后面verilog的描述。

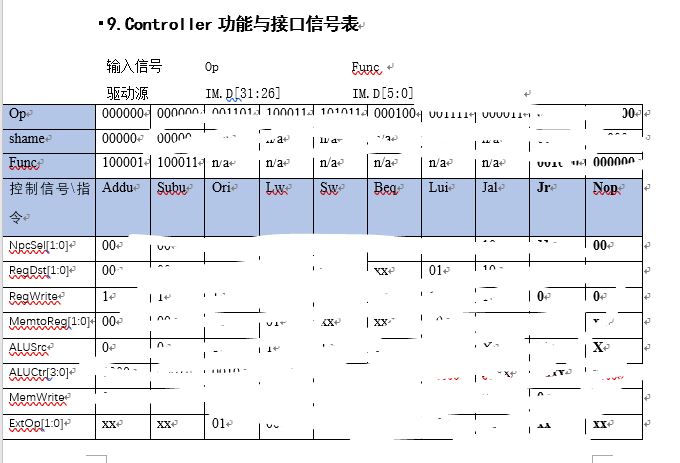

3.综合数据通路 初步构建Controller

如上表所示,综合数据通路的过程就是添加多路选择器以及描述控制器的过程。

四、构建Controller端口与功能表

直接上图,关注表头:

端口定义也可从图中获得。

4.利用上述端口与功能定义表使用Verilog描述各个部件和多路选择器(包括controller)

注意:实验中reset需要对所有时序部件(包括GRF DM PC进行同步复位,不包括IM);

理解:将CPU看成大型的有限状态机,复位代表保存的状态全部清零。

5.描述数据通路

利用设计的数据通路综合表,就能知道端口之间的连接关系。

用Verilog描述时,由于需要模块实例化,不同部件端口不能直接相连,必须使用wire型作为媒介,命名规范之后提。

6.测试程序

二、描述Controller的方法

我是采用assign赋值、和或逻辑,

或逻辑就是或门;和逻辑可以利用三目运算符从而代替直接描述logisim中的门级描述,避免出错。

例如 assign subu=(Op==6'b000000&&Func==6'b100011)?1:0;

至于if-else和case语句我觉得并没有更简单,宏定义我就想不到了,评论区可以指正完善我的思考题orz。

我的P4 Verilog的命名规范(尝试总结,试行版)大概率P5要修改

1.各部件端口定义与功能表

杜绝单纯的I O 等毫无意义千篇一律的设置。

在填写表格时,可以PC.DO 部件名+.+端口名

DO DI WD RD Addr 只要在表格中写清楚就好·····注意大小写

2.在写数据通路时,wire和各个部件的输出端口同名,从而确保CPU连接的正确性

PC.DO -> PCDO去掉.

特殊情况下须标注

3.多路选择器按顺序命名Mux1 Mux2 Mux3 实例化时改为M1 M2 M3

好像没有要强调的啊。。。。啊先这样吧

加油鸭!

P4-verilog实现mips单周期CPU的更多相关文章

- 使用Verilog搭建一个单周期CPU

使用Verilog搭建一个单周期CPU 搭建篇 总体结构 其实跟使用logisim搭建CPU基本一致,甚至更简单,因为完全可以照着logisim的电路图来写,各个模块和模块间的连接在logisim中非 ...

- Verilog hdl 实现单周期cpu

参考计组实验测试指令 - 简书,添加了一些细节. 1.添加 bne指令 修改 ctrl.v 之后修改mipstestloopjal_sim.asm,mars dump 为 bnetest. ...

- Verilog单周期CPU(未完待续)

单周期CPU:指令周期=CPU周期 Top模块作为数据通路 运算器中有ALU,通路寄存器(R1.R2.R3.R4),数据缓冲寄存器(鉴于书上的运算器只有R0)........... 此为ALU和通用寄 ...

- 单周期cpu设计代码解读

目录 写在前面 单周期cpu设计代码讲解 概念回顾 Verilog代码讲解 写在前面 欢迎转载,转载请说明出处. 单周期cpu设计代码讲解 概念回顾 一.电子计算机的部件 分为:中央处理器(cpu). ...

- 单周期CPU设计的理论基础

写在前面:本博客内容为本人老师原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文! 本博客全网唯一合法UR ...

- 单周期CPU设计

终于有点时间了,恰好多周期的设计也已经完成,其实只想写写多周期的,无奈单周期补上才好,哈哈哈~ —————+—————黄金分割线—————+————— 首先要理解什么叫单周期CPU(与后面多周期CPU ...

- 为什么现在使用多周期CPU,而单周期CPU被弃用?

最初设计的CPU结构简单,内部不复杂.之所以制造它是为了让机器自动跑程序,算数. 早期CPU都是单周期的,人们没考虑那么多,性能啥的.就让CPU每个时钟周期跑一个指令,这些时钟周期等长.这样下来,有的 ...

- 单周期CPU

一个时钟周期执行一条指令的过程理解(单周期CPU): https://blog.csdn.net/a201577F0546/article/details/84726912 单周期CPU指的是一条指令 ...

- 使用logisim搭建单周期CPU与添加指令

使用logisim搭建单周期CPU与添加指令 搭建 总设计 借用高老板的图,我们只需要分别做出PC.NPC.IM.RF.EXT.ALU.DM.Controller模块即可,再按图连线,最后进行控制信号 ...

随机推荐

- 无 PowerShell.exe 执行 Empire 的几种姿势

在实战中,Empire成为域渗透.后渗透阶段一大利器,而Empire是一个Powershell RAT,所以PowerShell必须要能运行Empire中几乎所有的启动方法都依赖于使用PowerShe ...

- CDN实现原理

避让:尽可能避开互联网上有可能影响数据传输速度和稳定性的瓶颈和环节,使内容传输的更快.更稳定. 检测:通过在网络各处放置节点服务器所构成的在现有的互联网基础之上的一层智能虚拟网络,CDN系统能够实时监 ...

- xpath相关用法及技巧

本节讲解网页解析神器----XPath lxml下载 xpath基本用法 xpath插件 Xpath及XML路径语言,它是一门在XML文档查找信息的语言. 一:lxml下载以及安装 首先需要解决lxm ...

- MFC中如何分割CString类型的数据

[才疏学浅,难免有纰漏,若有不正确的地方,欢迎指教] MFC中有一个库函数 Tokenize(); 函数原型:CStringT Tokenize( PCXSTR pszTokens , int& ...

- 01--Java语言概述与开发环境 最适合入门的Java教程

Java 程序运行机制 编译型语言: 使用专门的编译器,针对特定平台(操作系统)将某种高级语言源代码一次性"翻 译"成可被该平台硬件执行的机器码(包括机器指令和操作数),并包装成该 ...

- 面试必问:ACID/CAP

转载: https://www.jdon.com/artichect/acid-cap.html ACID和CAP的详尽比较 事务机制ACID和CAP理论是数据管理和分布式系统中两个重要的概念,很不巧 ...

- LeetCode122——Best Time to Buy and Sell Stock II

题目: Say you have an array for which the ith element is the price of a given stock on day i. Design a ...

- 第一章、Python环境搭建

一.安装Python解释器 Windows下 Python开发环境搭建 1.官网下载: https://www.python.org/downloads/ 2.选择对应的版本 3.双击运行 4.选 ...

- hash算法的应用

一.单词模式匹配 描述:单词模式字符串为“一二二一”,目标字符串为"苹果 香蕉 香蕉 苹果"则匹配成功 a=[1,2,2,1,1,3] b=['x','y','y','x','x' ...

- [Java] 生成二维码源码,可以在二维码中间加logo,底部可以加文字介绍

链接:https://pan.baidu.com/s/1bc1h-ix-No-2o9Ysd4_B3Q提取码:0ad4