Quartus Prime 与 Modelsim 调试 及do文件使用

Quartus Prime 与 Modelsim 调试 及do文件使用

Quartus Prime 与 Modelsim 调试 及do文件使用

前言

最新从Xilinx转到Intel,摸索quartus调试做的一些总结

推荐使用quartus加modelsim-intel edition,原因后面讲。但是本博客的目的是总结出quartus prime pro的modelsim使用(这个是最麻烦,自动化最差的),所以选择modelsim的独立版本。本文通过学习standard版本中自动生成的do文件,学习并总结modelsim仿真库的配置(基于quartus)和do文件的详细使用。

调试1,调试2 作为学习仿真操作和do文件编写的一个探索,调试3是pro版真正实操的流程

困难:目前只能对a10及以下芯片仿真,Stratix 10(pro edition才能用)找不到对应的仿真库(器件库已经装了,但是找不到仿真库),目前没法仿真,若有大佬知道怎么解决,望告知,感激不尽。

Quartus本身的一些信息

- 2017开始quartus prime 分standard和pro版本,standard版本支持器件到a10,pro能s10.

- standard版本支持直接调用modelsim(通过run simulation tool),pro版本没有这个选项

- 安装quartus时可以直接不勾选modelsim(starter版也可以,但是不推荐,有些仿真限制(1w行代码))

- 可以勾选modelsim-intel edition(需单独和谐),这样仿真的时候do文件就不用编译和链接(vmap)基础库了,但是ip核相关的文件还是要加

- 接下来的演示以modelsim独立版本为例,目的是探索pro版本的全部操作

调试 1(基于无IP核模式and简单Verilog代码)

安装完quartus(standard edition)后:

安装modelsim10.5se 并和谐:

下面基于是modelsim独立版本

- 在quartus中链接modelsim(每个新工程都需要这样做一次):

- 并且编译一次器件库到modelsim中,在quartus中也定位一下编译好的库(这样就不用每次仿真前都编译一下,但是每个工程都需要设 置一次

- 定位好了以后就可以顺利仿真了,通过run simulation tool。

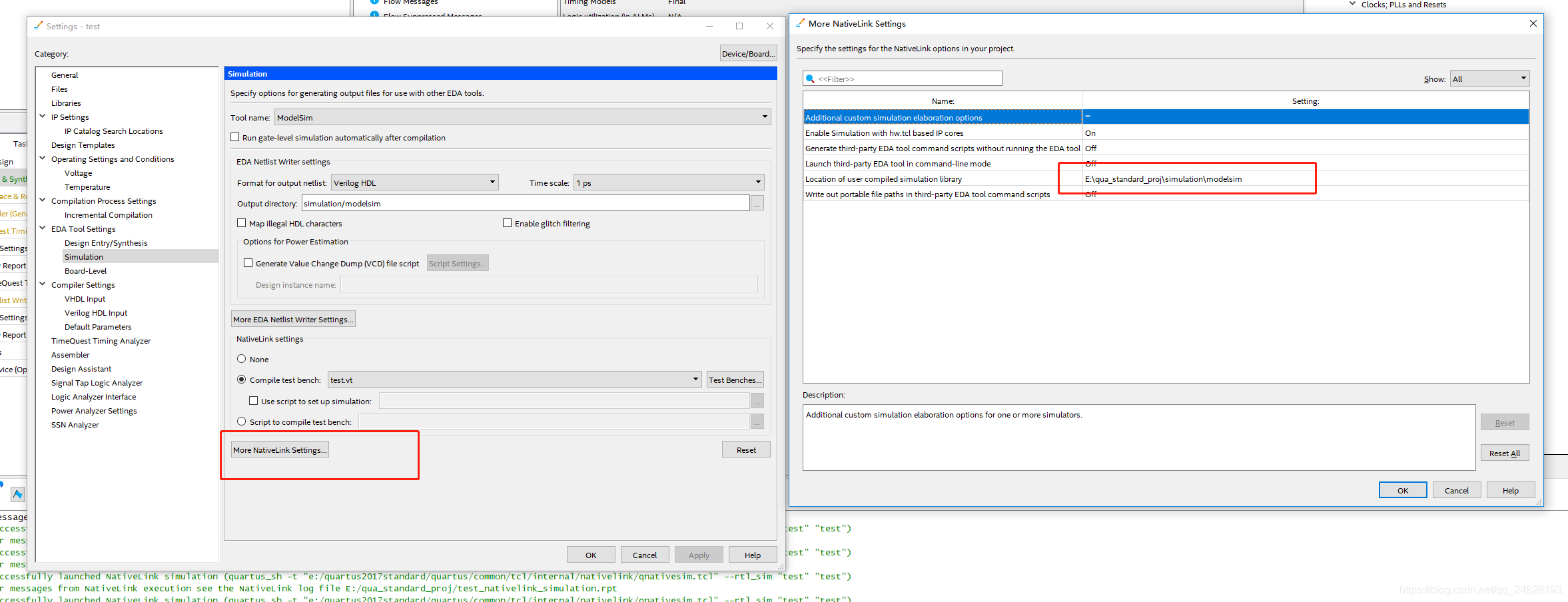

这里是编译基础库和quartus中链接user compiled library location 的方法

这里是quartus设置仿真软件及testbench的方法

调试2 (基于有ip核)

使用简单的 IOPLL IP核进行测试,基于quartus prime 2017 standard:调试仿真

- 按照调试1中的步骤进行设置,发现会报错误,类似于找不到编译库(PLL相关)

do文件(通过run simulation tool 生成的do)编译ip核的包的时候可能会出现错误(找不到ip核的相关包) - 这种情况就不能如1中一样设置 user compiled library location为quartus预先编译的modelsim库(会缺ip核的包)

- 把这个选项reset成none,也就是不设置

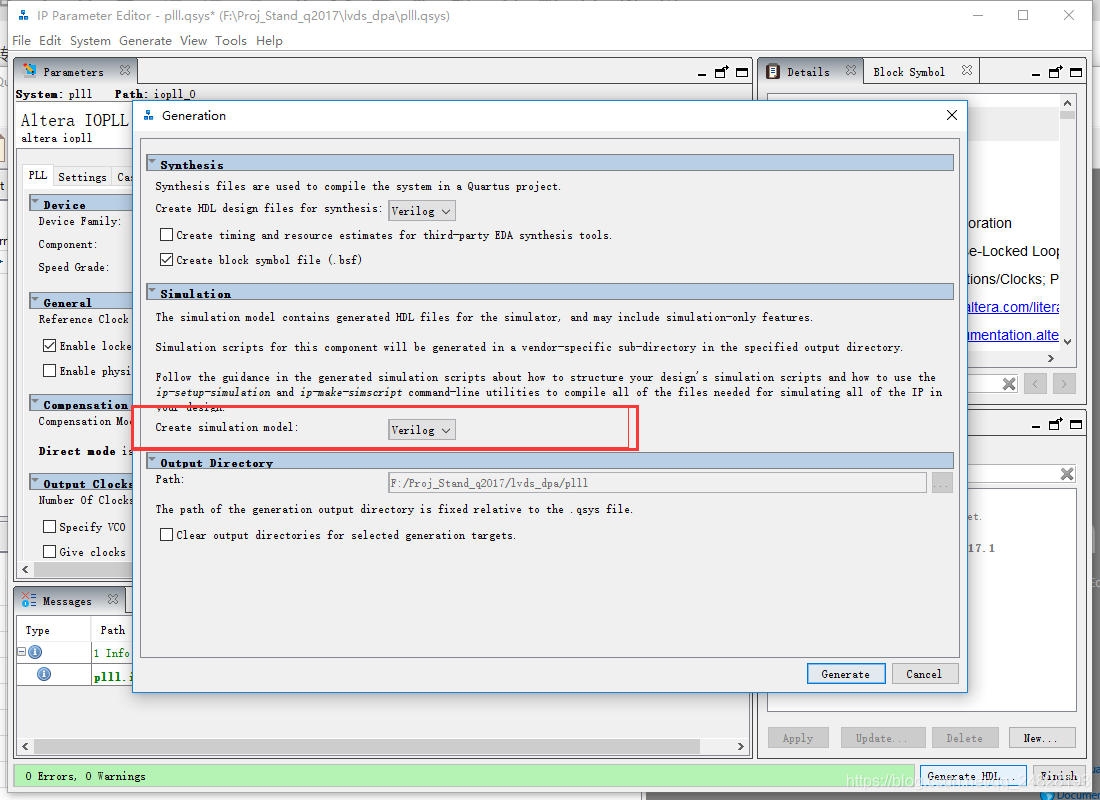

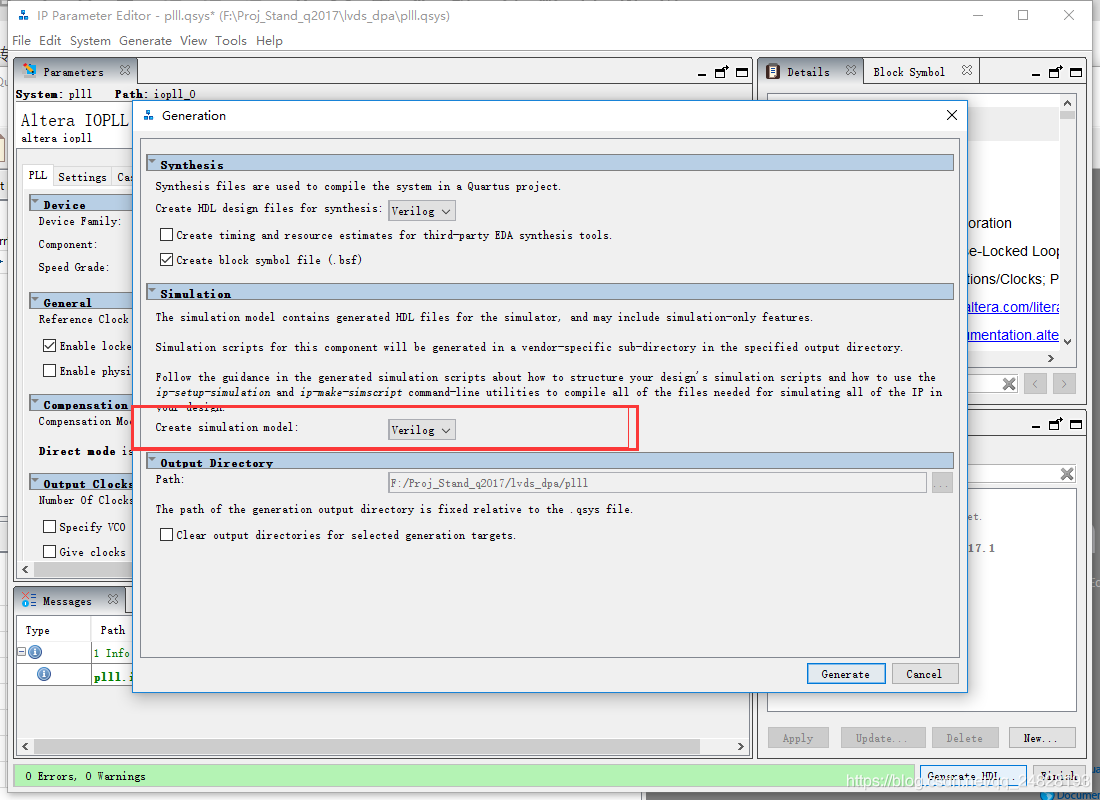

- 同时,IP核的仿真文件需要在设置IP核generate HDL的时候勾选simulation

若不设置user compiled labrary,则每次的do文件都会编译一次基础库(从quartus安装目录下面)和ip核相关文件(这个ip核的仿真文件需要在设置IP核generate HDL的时候勾选simulation ),.do文件实例如下(quartus standard 生成的),可以看出除了基础库,还会编译pll.vo,这个是生成ip核时同时生成的,这个就是最完整的.do文件,作为pro版自己编写时的参考

可以看到,modelsim仿真需要 的所有操作, 链接编译 基本库、ip核vo,v(包含ip核顶层文件v,还有主体文件vo)、 编译用户文件.v、 编译testbench , 并仿真testbench

这部分代码一定不能跳过,要仔细研究

transcript on

if ![file isdirectory test_iputf_libs] {

file mkdir test_iputf_libs

}

if ![file isdirectory verilog_libs] {

file mkdir verilog_libs

}

vlib verilog_libs/altera_ver

vmap altera_ver ./verilog_libs/altera_ver

vlog -vlog01compat -work altera_ver {e:/quartus2017standard/quartus/eda/sim_lib/altera_primitives.v}

vlib verilog_libs/lpm_ver

vmap lpm_ver ./verilog_libs/lpm_ver

vlog -vlog01compat -work lpm_ver {e:/quartus2017standard/quartus/eda/sim_lib/220model.v}

vlib verilog_libs/sgate_ver

vmap sgate_ver ./verilog_libs/sgate_ver

vlog -vlog01compat -work sgate_ver {e:/quartus2017standard/quartus/eda/sim_lib/sgate.v}

vlib verilog_libs/altera_mf_ver

vmap altera_mf_ver ./verilog_libs/altera_mf_ver

vlog -vlog01compat -work altera_mf_ver {e:/quartus2017standard/quartus/eda/sim_lib/altera_mf.v}

vlib verilog_libs/altera_lnsim_ver

vmap altera_lnsim_ver ./verilog_libs/altera_lnsim_ver

vlog -sv -work altera_lnsim_ver {e:/quartus2017standard/quartus/eda/sim_lib/altera_lnsim.sv}

vlib verilog_libs/twentynm_ver

vmap twentynm_ver ./verilog_libs/twentynm_ver

vlog -vlog01compat -work twentynm_ver {e:/quartus2017standard/quartus/eda/sim_lib/twentynm_atoms.v}

vlog -vlog01compat -work twentynm_ver {e:/quartus2017standard/quartus/eda/sim_lib/mentor/twentynm_atoms_ncrypt.v}

vlib verilog_libs/twentynm_hssi_ver

vmap twentynm_hssi_ver ./verilog_libs/twentynm_hssi_ver

vlog -vlog01compat -work twentynm_hssi_ver {e:/quartus2017standard/quartus/eda/sim_lib/mentor/twentynm_hssi_atoms_ncrypt.v}

vlog -vlog01compat -work twentynm_hssi_ver {e:/quartus2017standard/quartus/eda/sim_lib/twentynm_hssi_atoms.v}

vlib verilog_libs/twentynm_hip_ver

vmap twentynm_hip_ver ./verilog_libs/twentynm_hip_ver

vlog -vlog01compat -work twentynm_hip_ver {e:/quartus2017standard/quartus/eda/sim_lib/mentor/twentynm_hip_atoms_ncrypt.v}

vlog -vlog01compat -work twentynm_hip_ver {e:/quartus2017standard/quartus/eda/sim_lib/twentynm_hip_atoms.v}

if {[file exists rtl_work]} {

vdel -lib rtl_work -all

}

vlib rtl_work

vmap work rtl_work

###### Libraries for IPUTF cores

vlib test_iputf_libs/PLL_altera_iopll_171

vmap PLL_altera_iopll_171 ./test_iputf_libs/PLL_altera_iopll_171

###### End libraries for IPUTF cores

###### MIF file copy and HDL compilation commands for IPUTF cores

vlog "E:/qua_standard_proj/PLL/altera_iopll_171/sim/PLL_altera_iopll_171_qwujbna.vo" -work PLL_altera_iopll_171

vlog "E:/qua_standard_proj/PLL/sim/PLL.v"

vlog -vlog01compat -work work +incdir+E:/qua_standard_proj {E:/qua_standard_proj/test.v}

vlog -vlog01compat -work work +incdir+E:/qua_standard_proj/simulation/modelsim {E:/qua_standard_proj/simulation/modelsim/test.vt}

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L twentynm_ver -L twentynm_hssi_ver -L twentynm_hip_ver -L rtl_work -L work -L PLL_altera_iopll_171 -voptargs="+acc" top_vlg_tst

add wave *

view structure

view signals

run 1 us

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

到此就可以正常的仿真了,但是这样每次都要编译一次基础库,很麻烦,所以编译一次以后,就可以进行这样的设置:、

- 在user compiled library location设置本工程simulation/modelsim的路径(之前的那个do文件,会把所有的编译结果存储在同文件夹下,这个是可以直接调用的)

设置示例:

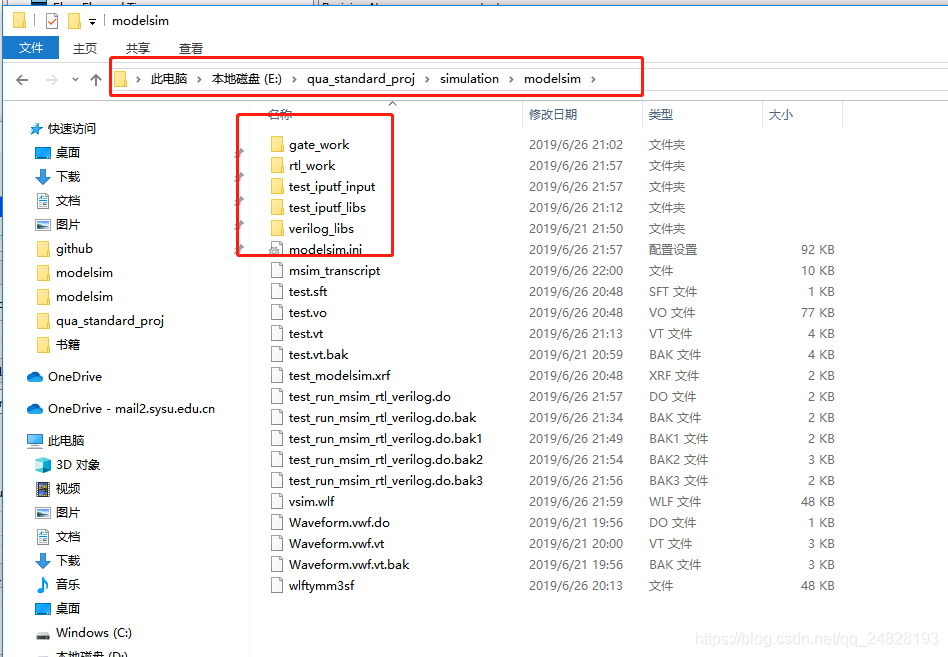

目录结构,红框标记的就是编译生成的库和modelsim的project文件夹(work)

这样每次仿真需要的库这边都有了

如果再次使用run simulation tool ,查看产生的新的.do文件,这次没有编译基础库,只是链接(vmap)了一下已有的编译结果。

transcript on

if ![file isdirectory test_iputf_libs] {

file mkdir test_iputf_libs

}

#vmap altera_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/altera_ver

#vmap lpm_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/lpm_ver

#vmap sgate_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/sgate_ver

#vmap altera_mf_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/altera_mf_ver

#vmap altera_lnsim_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/altera_lnsim_ver

#vmap twentynm_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/twentynm_ver

#vmap twentynm_hssi_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/twentynm_hssi_ver

#vmap twentynm_hip_ver E:/qua_standard_proj/simulation/modelsim/verilog_libs/twentynm_hip_ver

if {[file exists rtl_work]} {

vdel -lib rtl_work -all

}

vlib rtl_work

vmap work rtl_work

###### Libraries for IPUTF cores

vlib test_iputf_libs/PLL_altera_iopll_171

vmap PLL_altera_iopll_171 E:/qua_standard_proj/simulation/modelsim/test_iputf_libs/PLL_altera_iopll_171

###### End libraries for IPUTF cores

###### MIF file copy and HDL compilation commands for IPUTF cores

vlog "E:/qua_standard_proj/PLL/altera_iopll_171/sim/PLL_altera_iopll_171_qwujbna.vo" -work PLL_altera_iopll_171

vlog "E:/qua_standard_proj/PLL/sim/PLL.v"

vlog -vlog01compat -work work +incdir+E:/qua_standard_proj {E:/qua_standard_proj/test.v}

vlog -vlog01compat -work work +incdir+E:/qua_standard_proj/simulation/modelsim {E:/qua_standard_proj/simulation/modelsim/test.vt}

#-L 后面接着要链接的库,类似于 #include xxx.h

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L twentynm_ver -L twentynm_hssi_ver -L twentynm_hip_ver -L rtl_work -L work -L PLL_altera_iopll_171 -voptargs="+acc" top_vlg_tst

add wave *

view structure

view signals

run 1 us

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

用这样的do文件进行仿真,不用重复编译

参考这个设计:

就可以在pro edition里面先设置仿真软件为modelsim后

参考完整的do文件(第一个),编写对应其设计和路径的do文件

在modelsim 中File-Change Directory 到do所在的文件夹后

运行do xxx.do 编译全部需要库并开始第一次仿真。

第二次仿真可以参考本文第二个do文件编写do文件,(主要操作是Vmap)

即可脱离quartus直接使用modelsim仿真,使用编辑器编译工程Verilog代码和testbench后运行do文件就可以重新编译和仿真了(库没变所以不用重新编译)。

调试3 PRO edition+Modelsim-Intel edition

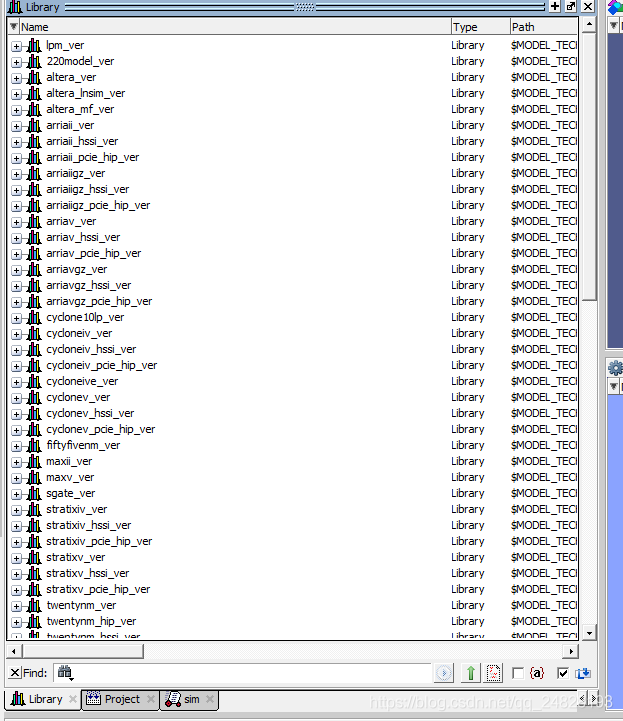

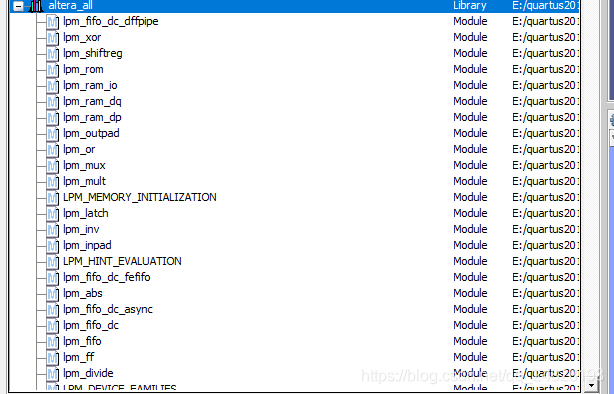

前期工作,安装Modelsim-Intel edition 这个软件已经把需要的库全部编译链接好了

如图

软件安装和quartus建立工程部分略去

quartus pro 中 assignment-setting-EDA Tool Setting 中选择modelsim-intel FPGA

IP核还是选择如下

top.v文件如下

module top

(

input wire a,

input wire b,

output reg c,

input wire clk,

input wire reset

);

reg aa,bb;

wire locked;

wire sysclk;

pll_custom u0 (

.rst (reset), // reset.reset

.refclk (clk), // refclk.clk

.locked (locked), // locked.export

.outclk_0 (sysclk) // outclk0.clk

);

always@(posedge sysclk)

begin

aa<=a;

bb<=b;

c<=aa&bb;

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

test.vt 或者test.v 如下:其模块名字为 top_vlg_tst

`timescale 1 ns/ 1 ps

module top_vlg_tst();

// constants

// general purpose registers

parameter period = 10;

// test vector input registers

reg a;

reg b;

// wires

wire c;

reg clk;

reg reset;

// assign statements (if any)

top t1 (

// port map - connection between master ports and signals/registers

.a(a),

.b(b),

.c(c),

.clk(clk),

.reset(reset)

);

initial

begin

clk = 0;

a = 0;

b = 0;

reset = 0;

#(5*period)

reset = 1;

#(5*period)

reset = 0;

#(200*period)

#(5*period)

a = 1;

b = 1;

#(5*period)

a = 0;

b = 1;

// --> end

//$display("Running testbench");

end

always #(period/2) clk = ~clk;

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

编写rtl_verilog.do 文件

transcript on

#由于是这个modelsim Intel edtion已经把库编译链接了,可以直接访问相关库,所有这里不需要用vmap链接库

if {[file exists rtl_work]} {

vdel -lib rtl_work -all

}

vlib rtl_work

vmap work rtl_work

#编译需要的工程文件

vlog -vlog01compat -work work +incdir+E:\project_2017_pro\simulation\modelsim {E:\project_2017_pro\simulation\modelsim\top.v}

vlog -vlog01compat -work work +incdir+E:\project_2017_pro\simulation\modelsim {E:\project_2017_pro\simulation\modelsim\test.v}

#编译生成的IP核文件

vlog -vlog01compat -work work +incdir+E:\project_2017_pro\pll_custom\sim {E:\project_2017_pro\pll_custom\sim\pll_custom.v}

vlog -vlog01compat -work work +incdir+E:\project_2017_pro\pll_custom\altera_iopll_171\sim {E:\project_2017_pro\pll_custom\altera_iopll_171\sim\pll_custom_altera_iopll_171_vidhshy.vo}

#开始仿真, vsim -L library ,这里类似于include,由于软件中已经预先链接了这些库,这里可以直接include,而不需要根据路径去找,再用vmap链接

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L twentynm_ver -L twentynm_hssi_ver -L twentynm_hip_ver -L rtl_work -L work -voptargs="+acc" top_vlg_tst

#top_vlg_tst 这个就是testbench里面的测试model名字

add wave *

view structure

view signals

run 10 us

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

单独打开Moselsim-Intel-FPGA-edition

File-change derectory…

选择.do文件所在文件夹

运行命令 do rtl_verilog.do 开始仿真

TIPS

仿真时 这些-L的参数也有些烦,容易漏

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L twentynm_ver -L twentynm_hssi_ver -L twentynm_hip_ver -L rtl_work -L work -voptargs="+acc" top_vlg_tst

- 1

参考这个链接中的Modelsim库编译过程()

https://blog.csdn.net/pianzhiwdy1996/article/details/80099780

但是不全照搬,为了方便,只生成和compile一个 Altera_all 的library,但是这个library要编译 E:\quartus2017pro\quartus\eda\sim_lib 这个路径下所有的 .v 和 .sv文件,包括二级目录下(for Verilog,compile过程有报错,目前无视)

根据链接中的步骤,最终添加好altera_all library的时候,do文件中就可以这样启动仿真

vsim -t 1ps -L altera_all -voptargs="+acc" top_vlg_tstvs

- 1

最终开始仿真

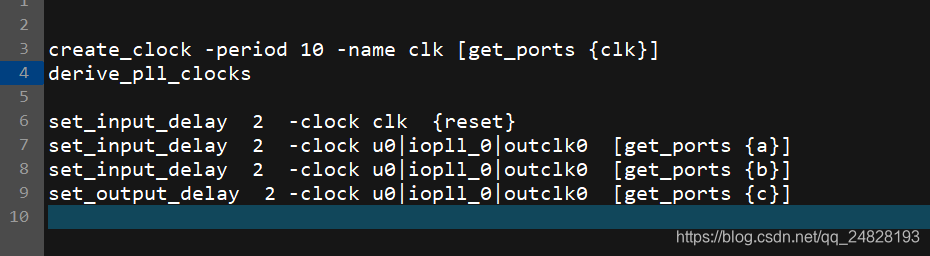

调试4:Quartus 2017 standard timequst Timing Analyer and sdc

添加Pll的时钟约束,然后端口参考PLL时钟,参考sdc,添加约束,这样就不会报uncontrain约束warning。PLL时钟是在时钟报告中找到的具体名字

目前还有的问题:

1.gate level simulation中没有看到波形延迟,存疑

Quartus Prime 与 Modelsim 调试 及do文件使用的更多相关文章

- 【转】Quartus II调用modelsim无缝仿真

Quartus II调用modelsim无缝仿真 ★emouse 思·睿博客文章★ 原创文章转载请注明:http://emouse.cnblogs.com 本篇文章为转载,写的不错,最近在学mode ...

- Quartus II调用modelsim无缝仿真

本篇文章为转载,写的不错,最近在学modelsim仿真,网上的教程很乱,把自己认为不错的整理贴出来,后面有机会会写个详细点的. Quartus 中调用modelsim的流程 1. 设定仿真工具 ass ...

- Quartus 中调用modelsim的流程及*.vt或*.vht自动生成

一.自动生成验证程序testbench的方法,setting-EDA Tool->simylation->选择对应的语言(verilog对应*.vt,VHDL对应*.vht)process ...

- Quartus II 使用 modelsim 仿真

转自:http://www.cnblogs.com/emouse/archive/2012/07/08/2581223.html Quartus 中调用modelsim的流程 1. 设定仿真工具 as ...

- Quartus II 与 Modelsim 联调【转】

Quartus II 9.0版本的时候软件还有自带的仿真工具,现在安装的是11.0以上版本,才发现 Quartus II 11.0以上取消了软件自带的波形仿真工具,因此需要波形仿真就要调用专业的仿真工 ...

- (转)Quartus II和Modelsim的联合仿真(详细)

这篇文章不需要在modelsim中建库.映射.建工程等一些繁琐的步骤,直接使用modelsim中的默认work库.使用quartus+modelsim联合仿真. 首先推荐一篇文章 http://www ...

- Quartus II 与modelsim连接不上的问题

在Quartus II 中tools>options>General>EDA Tool Options 设置modelsim 路径 说明:不管是Quartus II 与modelsi ...

- [vim配置]windows下在vim中使用gcc/g++编译调试c/cpp文件

在Linux里面混了一个多月,vim编程用得甚爽.无奈前天将Linux里面的编程文件夹误删,而技术不精无法找回,悲痛欲绝.再者,无限怀念windows里面的游戏,并觉得现在在Linux里面也学不到什么 ...

- Viavdo&ISE&Quartus II级联Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

随机推荐

- Linux 下的7种文件类型

普通文件类型 (-)Linux中最多的一种文件类型, 包括 纯文本文件(ASCII):二进制文件(binary):数据格式的文件(data);各种压缩文件.第一个属性为 [-] ,这些文件一般是用一些 ...

- 使用代码获得Hybris Commerce里显示的产品图片

使用下面这个API去取Hybris Commerce系统里产品主数据的明细信息: https://:9002/rest/v2/electronics/products/300938?fields=FU ...

- Spark编译的三种方式

有三种编译方式,此文采用make-distribution.sh编译 其余两种为maven 和SBT编译 1.配置jdk 配置maven 配置scala 2.修改spark下make-distribu ...

- tensorflow提示:No module named ''tensorflow.python.eager".

版权声明:本文为博主原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接和本声明. 本文链接:https://blog.csdn.net/qq_27921205/articl ...

- AR-运行自动开票主程序报错

问题: 在AR运行自动开票主程序时出现如下错误提示: 错误日志: raagsp()+ 当前的系统时间为 12-09-2014 07:23:58 raagsp()- 当前的系统时间为 12-09-201 ...

- fiddler模拟弱网测试

1.首先设置手机代理 设置手机代理到本机ip,端口号8888(Fiddler默认设置): 手机访问http://ip:port安装Fiddler证书 2.修改fiddler配置 勾选上后,已经开始限速 ...

- Python 去除文件中的空行

def clear_space(): with open("test","r",encoding="utf-8") as fr: for l ...

- php享元模式(flyweight pattern)

周日一大早,今天要送老婆孩子去火车站, 所以练代码要早点哈. <?php /* The flyweight pattern is about performance and resource r ...

- 指针数组(int *a[])和数组指针 (int (*a)[])

1.对指针有关的表达式阅读遵循的规则是“从右到左.由近到远.括号优先”. int *a[10] 从字符a开始,右侧是[10],表示a 为一个包含10个元素的数组,左侧为指针标记,表示这个数组中保存 ...

- _IplImage

IplImage结构 由于OpenCV主要针对的是计算机视觉方面的处理,因此在函数库中,最重要的结构体是IplImage结构.从本质上讲,他是一个CvMat对象,但它还有一些其他成员变量将矩阵解释为图 ...