FPGA中的时序分析(五)

时序约束实例详解

本篇博客结合之前的内容,然后实打实的做一个约束实例,通过本实例读者应该会实用timequest去分析相关的实例。本实例以VGA实验为基础,介绍如何去做时序约束。

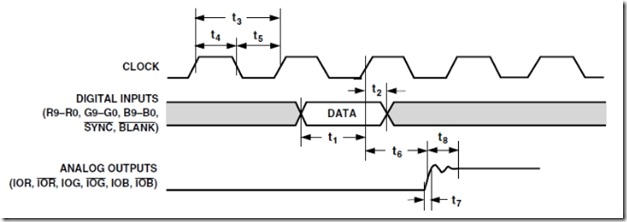

首先VGA这种情况属于供源时钟情况,不明白供源时钟的可以参看之前博客讲解。首先查看ADV7123的数据手册,查看其时序图。如下图所示,是建立时间和保持时间要求。

下图是时序图,可见t1和t2在时钟上升沿的位置,数据在时钟的上升沿进行采集。

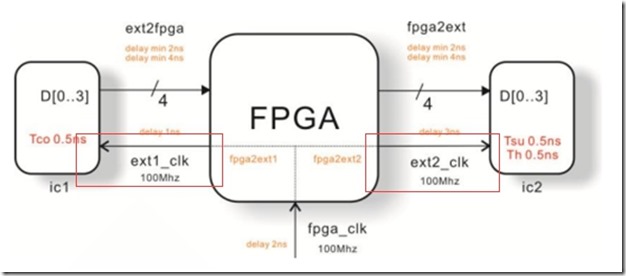

对于VGA实验来说,FPGA是发送端,ADV7123是接收端,如果传输的速率比较高的话,数据和时钟上升沿的严格对齐就要依靠PLL产生可调相位的时钟信号来保证,不过对于对于25MHz时钟通过较好的时序约束和分析后,则不必动用PLL。

接下来需要产生虚拟时钟,对于reg2reg路径的分析,其时钟都是FPGA内部,不用产生虚拟时钟,但是对于pin2reg或者reg2pin这种情况,需要产生一个虚拟时钟,作为pin端的时钟来分析时序。如下图中的标注所示。

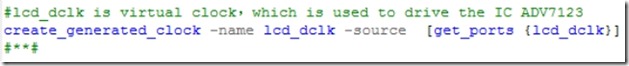

所以ADV7123和FPGA进行时钟相关的信号就是ADV7123的驱动时钟,明白这个信号之后,需要设置其虚拟时钟约束,如下图所示。

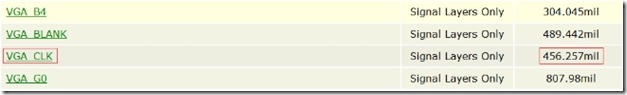

由于FPGA是相对于ADV7123为输出ADV7123所需要的信号,所以需要设置输出延迟约束。这一部分结合上一篇博客的分析,首先需要计算FPGA到ADV7123芯片的延迟,这一部分主要是PCB上面的信号走线延时。所以需要结合PCB走线来估计延迟时间。

打开altium designer,然后查看VGA模块的走线长度如下图1所示,长度大约是11.589mm。

图1 VGA模块走线长度

在FPGA核心板(笔者设计的一款学习板)上面的lcd_dclk的走线长度如下图2所示。长度大约是41.4mm。

图2 核心板走线长度

根据上述的计算,所以lcd_dclk总得走线长度 = 52.989mm。

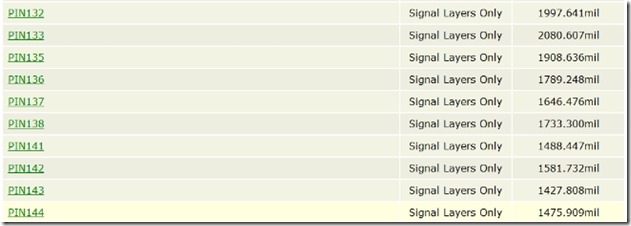

同样的道理,数据走线长度如下图3所示,此走线长度是VGA模块上面的长度,长度大约在7.72~43.152mm,那么对于核心板上面的走线模块长度如图4所示,大概长度约为28.65 ~ 53.32mm,总的长度为36.37mm~96.472mm,根据0.17ns/25.4mm,lcd_clk走线延迟0.35ns,数据总线延迟0.24ns~0.646ns。

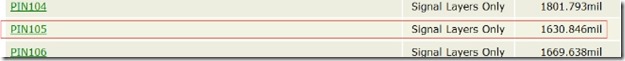

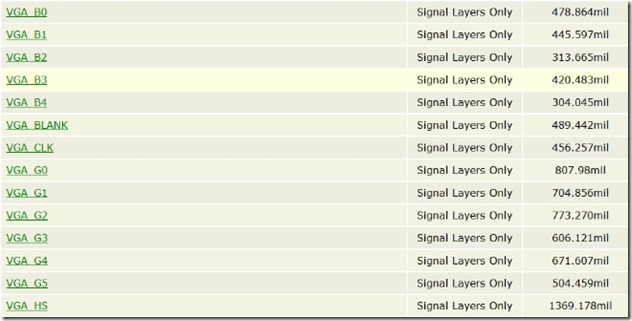

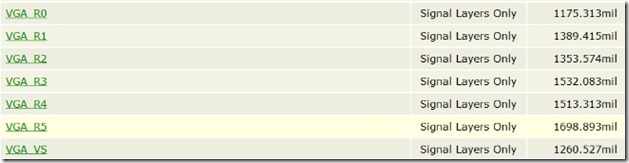

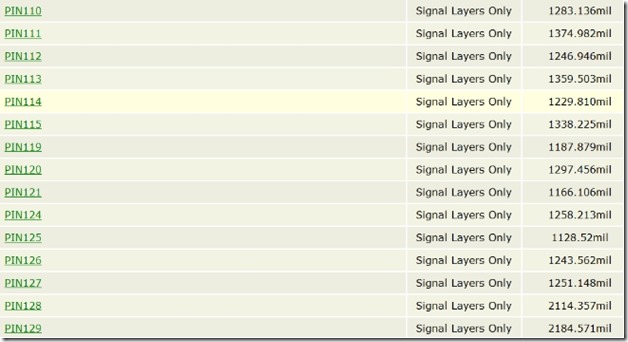

图3 各信号走线延迟

图4 核心板各信号走线延迟

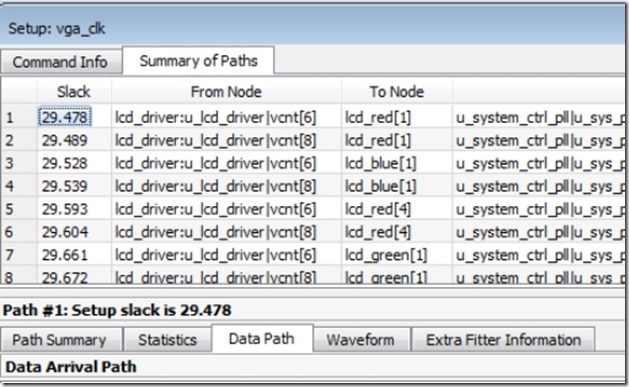

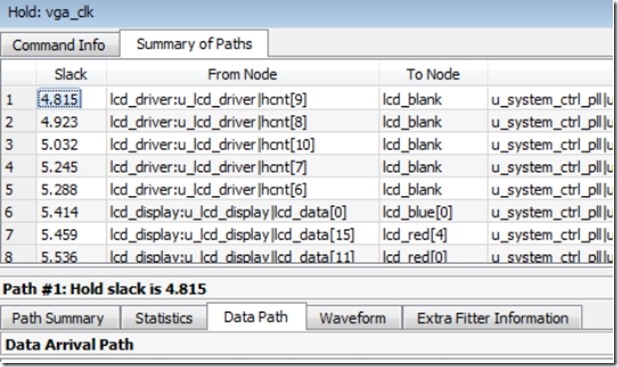

若是不考虑时钟偏移,那么进行时序分析得到的余量如图5所示。

图5 建立和保持余量

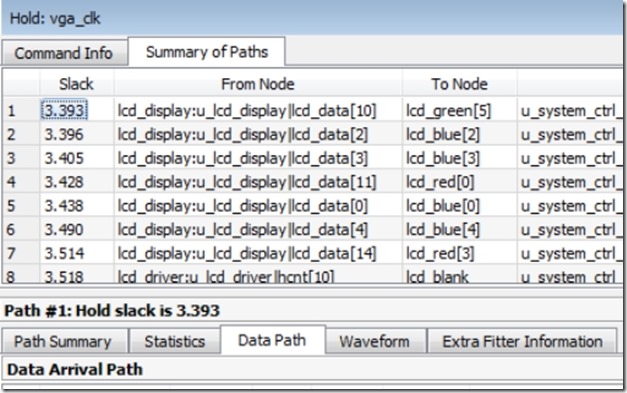

上述是计算完了FPGA到外部IC的延迟,但是还有时钟偏斜没有计算,那么需要用到set max/min delay 命令,对于lcd_dclk先估计一个范围,如0~5ns即可,这个范围肯定是满足要求,但是可能会不能够留有更多的余量。然后在将有时钟偏移的延迟时间代入set output delay的表达式中,此处利用公式将lcd_dclk 最大延迟设为3ns,lcd_dclk最小延迟设为1ns,那么考虑时钟偏斜的输出最大值 = 0.646 + 0.2 -3 = -2.154ns;输出最小值 = 0.24 - 1.5 - 1 = -2.26ns;

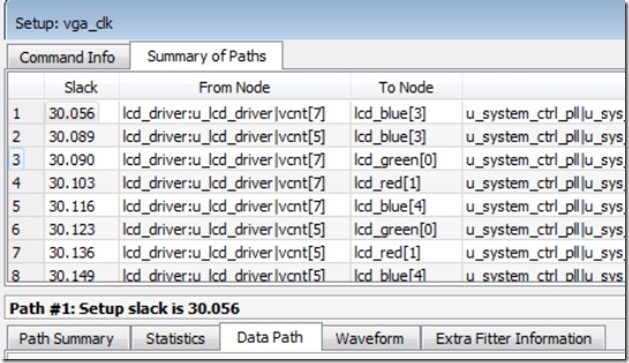

图6是约束后的建立余量和保持余量,可以看到满足时序要求,并保有很大的时序余量。

图6 建立余量和保持余量

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================

FPGA中的时序分析(五)的更多相关文章

- FPGA中的时序分析(一)

谈及此部分,多多少少有一定的难度,笔者写下这篇文章,差不多是在学习FPGA一年之后的成果,尽管当时也是看过类似的文章,但是都没有引起笔者注意,笔者现在再对此知识进行梳理,也发现了有很多不少的收获.笔者 ...

- FPGA中的时序分析(四)

常用约束语句说明 关于Fmax 上述是实现Fmax的计算公式,clock skew delay的计算如下图, 就是两个时钟的差值.到头来,影响Fmax的值的大小就是组合逻辑,而Fmax是针对 ...

- FPGA中的时序分析(三)

验证公式正确性 前两篇博客提及了关于时序的建立余量和保持余量的计算.结合实际情况,验证公式的运算正确性.结合之前博客提及的LED实验,看一下建立余量和保持余量是否都合格. 建立余量 图1是最大时钟 ...

- FPGA中的时序分析(二)

使用Timequest 笔者对Altera较熟悉,这里以quartus ii中的timequest作为讲解. Timequest分析时序的核心,也就是在于延迟因数的计算.那么建立约束文件,去告诉tim ...

- 【转载】FPGA 中的latch 锁存器

以下这篇文章讲述了锁存器的一些概念和注意事项.原文标题及链接: FPGA 中的latch 锁存器 - 快乐至永远上的博客 - 与非博客 - 与网 http://www.eefocus.com/liuy ...

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- 巧用FPGA中资源

随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元.DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中.在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利 ...

- Android中Button的五种监听事件

简单聊一下Android中Button的五种监听事件: 1.在布局文件中为button添加onClick属性,Activity实现其方法2.匿名内部类作为事件监听器类3.内部类作为监听器4.Activ ...

- FPGA中的delay与latency

delay和latency都有延迟的意义,在FPGA中二者又有具体的区别. latency出现在时序逻辑电路中,表示数据从输入到输出有效经过的时间,通常以时钟周期为单位. delay出现在组合逻辑电路 ...

随机推荐

- 有关google的appengine部署服务器的简单教程

以下的内容都是看这个网址:https://developers.google.com/appengine/. 1.既然是google的东西.当然就要注册一个google的账号吧. (记得注册后要顺便把 ...

- 读取word到二进制,再转成word

static void Main(string[] args) { try { var strParams = new Dictionary<string, string>(); stri ...

- 淘宝分布式数据层TDDL

剖析淘宝 TDDL ( TAOBAO DISTRIBUTE DATA LAYER ) 注:原文:http://gao-xianglong.iteye.com/blog/1973591 前言 在开始 ...

- lua--clone

clone 深度克隆一个值. 格式: value = clone(值) 用法示例: -- 下面的代码,t2 是 t1 的引用,修改 t2 的属性时,t1 的内容也会发生变化 , b = } local ...

- raft Paxos

CONSENSUS: BRIDGING THEORY AND PRACTICE https://ramcloud.stanford.edu/~ongaro/thesis.pdf https://web ...

- RequestDispatcher.forward和HttpServletResponse.sendRedirect

(1)RequestDispatcher.forward方法只能将请求转发给同一个WEB应用中的组件:而HttpServletResponse.sendRedirect 方法不仅可以重定向到当前应用程 ...

- vim学习笔记(12):在vim中修改文件编码,解决vim 打开乱码

在linux 中查看文件编码可以通过以下几种方式: 一.查看文件编码 1.查看文件编码file命令 :file ip.txt ip.txt: UTF-8 Unicode text, with esca ...

- Dubbo实践笔记

注意的地方 默认情况下,cluster=failover.retries=2,意为失败重试两次,不包含原生调用.如需配置不重试,需设置retries=-1,或者使用failfast(快速失败)模式 如 ...

- 10款jQuery图片左右滚动插件

在现代的网页设计中,图片和内容滑块是一种极为常见和重要的元素.你可以从头开始编写自己的滑动效果,但是这将浪费很多时间,因为网络上已经有众多的优秀的 jQuery 滑块插件.当然,如果要从大量的 jQu ...

- word中的域代码

说明(2017-5-23 13:33:11): 1. Shift+F9显示域代码 2. Alt+F9显示全部域代码 3. Ctrl+F9添加一个域代码(一对大括号) 4. Ctrl+Shift+F9取 ...