FPGA学习笔记. DDS

DDS原理

直接数字式频率合成器(Direct Digital Synthesizer)

频率计算公式

Fout = FW * Fclk / 2^N

Fout 输出频率, Fw 频率控制字, N 位数 精度 Fclk / 2^N

设计思路

设置一个计数cnt作累加,Fw频率控制字,作为计数步长。

时钟clk下,cnt <= cnt + Fw.

设输入时钟是100mHz,目标Fo为115200Hz,计数器为32位,据上面的公式可以得出

Fw = Fo * 2^32 / Fc = 115200 * 2^32 / (100*10^6) = 4947802.3249992

取整 Fw = 4947802,

占空比为50%,cnt <= 2^N ,Fo = 0 ; cnt > 2^N ,Fo = 1。

添加一个block menery IP,存放 正弦波相位-幅度 表,由相位累加来查询地址。

生成COE文件

位宽32bit 深度2^12,code

clear;

close all;

%%

width = ; %data width

N = ; %addr witdh

depth = ^N;%memery depth

x = linspace(,*pi,depth);

y_sin = sin(x)+;

y_sin_q=round(y_sin*(^(width-)));

fid = fopen('CosWaveWid32Def2e12.coe','w');

%write header

fprintf(fid,'MEMORY_INITIALIZATION_RADIX=16;\n');

fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');

%write data

if(fid>)

fprintf(fid,'%x,\n',y_sin_q);

end

fclose(fid);

verilog 程序

累加与查询地址

/*

fc = 100MHz

fo = 1kHz

N = 32 (width)

fw = (fo * 2^N) / fc = 42949.67296 => 42950 */

module DdsTopV

#(

parameter COUNTWIDTH = ,

parameter FW = 'd429497

)

(

input wire clk,

input wire rst_n,

output reg clk_out,

// output wire [11:0] addr,

output wire [:] phase,

output wire [:] sin_o

); //wire [31:0] phase;

wire [:] addr;

reg [COUNTWIDTH-:] cnt; //相位累加

always @(posedge clk or posedge rst_n)

begin

if(!rst_n)

cnt <= ;

else

cnt <= cnt + FW; //计数器步长FW

end

//clk_out

always @(posedge clk or posedge rst_n)

begin

if(!rst_n)

clk_out <= 'b0;

else if(cnt < 'h7FFF_FFFF)

clk_out <= 'b0;

else

clk_out <= 'b1;

end assign phase = cnt;

assign addr = {phase[:]}; blk_mem_gen_0 blk_mem_gen_0(

.clka(clk),

.addra(addr),

.douta(sin_o)

); endmodule

TestBench

module testbench(); reg clk;

reg rst_n;

wire clk_out;

//wire [11:0] addr;

wire [:] phase;

wire [:] sin_o; /*

Fo = 115200Hz

Fw = 4947802.3

*/

DdsTopV

#(

// .COUNTWIDTH(32'd32),

.FW('d4947802)

)

uut

(

.clk(clk),

.rst_n(rst_n),

.phase (phase),

// .addr(addr),

.clk_out(clk_out),

.sin_o(sin_o)

); initial begin

clk = ;

rst_n = ;

# rst_n=;

end always # clk=~clk; endmodule

设置Block Memery

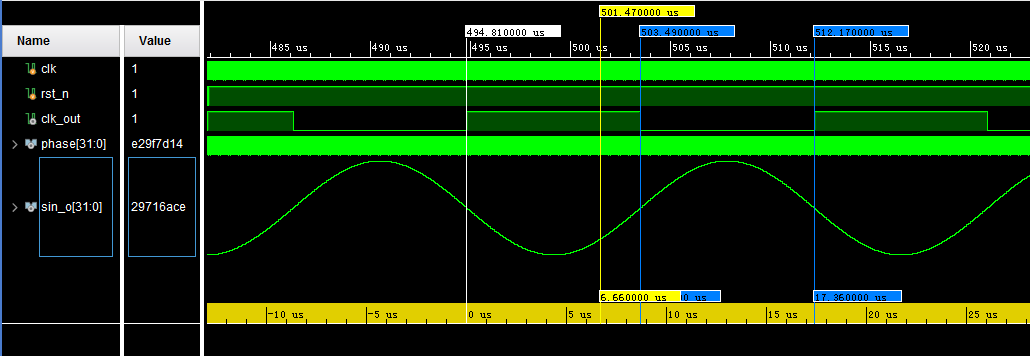

仿真结果

via

https://www.cnblogs.com/christsong/p/5536995.html

FPGA学习笔记. DDS的更多相关文章

- FPGA学习笔记(二)——FPGA学习路线及开发流程

###### [该随笔部分内容转载自小梅哥] ######### 一.FPGA学习路线 工具使用 -> 语法学习 -> 逻辑设计 -> IP使用 ->接口设计 -& ...

- FPGA学习笔记(三)—— 数字逻辑设计基础(抽象的艺术)

FPGA设计的是数字逻辑,在开始用HDL设计之前,需要先了解一下基本的数字逻辑设计-- 一门抽象的艺术. 现实世界是一个模拟的世界,有很多模拟量,比如温度,声音······都是模拟信号,通过对模拟信号 ...

- FPGA学习笔记(一)——初识FPGA

###### [该随笔部分内容转载自小梅哥] ######### FPGA(Field-Programmable Gate Array,现场可编程门阵列),正如其名,FPGA内部有大量的可 ...

- FPGA学习笔记(七)——FSM(Finite State Machine,有限状态机)设计

FPGA设计中,最重要的设计思想就是状态机的设计思想!状态机的本质就是对具有逻辑顺序和时序规律的事件的一种描述方法,它有三个要素:状态.输入.输出:状态也叫做状态变量(比如可以用电机的不同转速作为状态 ...

- Xilinx FPGA 学习笔记

一.时序设计 方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢. 方法2.FPGA中运行CPU 把逻辑控制顺序复杂的事情用C代码来实现,而实时处理部分用veri ...

- FPGA学习笔记之Altera FPGA使用JIC文件配置固化教程(转)

很多做过单片机的朋友都知 道,我们在对MCU烧写完程序固件后,那么该程序固件就存储在了该MCU内部.即使MCU断电了再重新上电,程序也能继续运行.这是因为对MCU烧写固件 的实质就是将程序固件写入到M ...

- FPGA学习笔记(八)—— 状态机设计实例之独立按键消抖

###### [该随笔中部分内容转载自小梅哥] ######### 独立按键消抖自古以来在单片机和FPGA中都是个不可避免的问题,首先,解释一下什么叫做按键抖动,如图,按键在按下和松开的那个瞬间存在大 ...

- FPGA学习笔记(六)—— 时序逻辑电路设计

用always@(posedge clk)描述 时序逻辑电路的基础——计数器(在每个时钟的上升沿递增1) 例1.四位计数器(同步使能.异步复位) // Module Name: coun ...

- FPGA学习笔记之按键控制

参考: [黑金原创教程][FPGA那些事儿-驱动篇I ]实验二:按键模块① - 消抖 源码如下: key_funcmod.v module key_funcmod(clk, rst, key, led ...

随机推荐

- PAT甲题题解-1015. Reversible Primes (20)-素数

先判断n是否为素数然后把n转化成d进制下再反转,转化为十进制的num判断num是否为素数 注意n为0和1时,不是素数!!!注意反转后的num也有可能为1,不是素数!!! #include <io ...

- 2017-2018 第一学期201623班《程序设计与数据结构》-第7&8周作业问题总结

一.作业内容 第7周作业 http://www.cnblogs.com/rocedu/p/7484252.html#WEEK07 第8周作业 http://www.cnblogs.com/rocedu ...

- 冲刺Two之站立会议1

今天我们开始了第二个冲刺期的工作,大家重新讨论了下个阶段的工作内容,由于上次演示我们主要只是实现了摄像头开启.通信和语音通话的功能,而且各部分还有待完善.所以我们决定了之后的主要工作的内容:之前服务器 ...

- 计算机启动出现 Invalid Partition Table

计算机启动出现 Invalid Partition Table 解决办法 使用大白菜启动盘进入临时系统,打开程序DiskGenius 如果系统盘(一般为 C 盘)非活动状态,先激活 如果装系统的硬盘不 ...

- YOLO(You Only Look Once)

参考 YOLO(You Only Look Once)算法详解 YOLO算法的原理与实现 一.介绍 YOLO算法把物体检测问题处理成回归问题,用一个卷积神经网络结构就可以从输入图像直接预测boundi ...

- DataGridView显示行号-RowPostPaint

DataGridView控件在显示数据时,我们有时候需要显示行号,以便检索查看方便使用. 但DataGridView默认没有设置显示行号的属性. 此时我们只要在DataGridView的RowPost ...

- (改进)Python语言实现词频统计

需求: 1.设计一个词频统计的程序. 2.英语文章中包含的英语标点符号不计入统计. 3.将统计结果按照单词的出现频率由大到小进行排序. 设计: 1.基本功能和用法会在程序中进行提示. 2.原理是利用分 ...

- 洛谷 P2245 星际导航 解题报告

P2245 星际导航 题目描述 sideman做好了回到Gliese 星球的硬件准备,但是sideman的导航系统还没有完全设计好.为了方便起见,我们可以认为宇宙是一张有N 个顶点和M 条边的带权无向 ...

- 洛谷 P2224 [HNOI2001]产品加工 解题报告

P2224 [HNOI2001]产品加工 题目描述 某加工厂有A.B两台机器,来加工的产品可以由其中任何一台机器完成,或者两台机器共同完成.由于受到机器性能和产品特性的限制,不同的机器加工同一产品所需 ...

- 解题:CTSC 2008 祭祀

题面 洛谷要求输出方案,懒得写了,但是还是放一下链接看看吧 (虽然现在二分图已经过气了=.=) 要求最长反链,最长反链=最小链覆盖,先Floyd传递闭包之后链覆盖就变成了边覆盖,然后最小边覆盖=总点数 ...