STM32F4 Timer Internal Trigger Connection

The Timers can be cascaded to make more complex timing relationships, or longer periods.

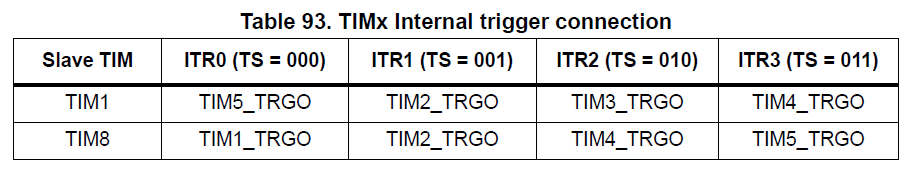

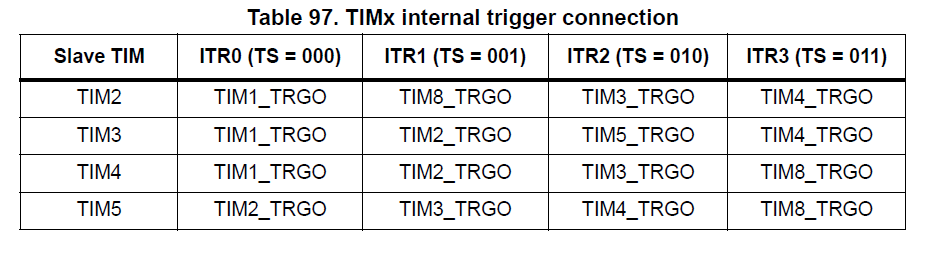

Internally only some timers can trigger others.

This is a Master/Slave relationship and is handled by the SMS register.

For example, you can see below that TIM8 can be triggerd by TIM1.

- Uses TRGI to map.

- One Timer can be used as the prescaler for another.

- The first timer update_event, or output_compare signal is used as clock for the second.

- The counter mode sets whether the update_event occurs on overflow and/or underflow of the Timer

- Counter mode is set using the TIMx_CR1 reg and CMS bits as indicated in the example below.

Example for internal trigger

Internal trigger clock mode 1 (ITRx)

TIM_CLK is replaced by ITRx_CLK which is the internal trigger freq mapped to timer Trigger input TRGI.

The counter mode indicates if the update_event is generated:

- on overflow - if mode = up counting, the DIR bit is reset in TIMx_CR1

- on underlfow - if mode = down counting, the DIR bit is set in TIMx_CR1

- both - if mode is center aligned, the CMS bits are non zero

The update_event is also generated by:

- software if the UG bit (Update Generation) is set in TIM_EGR reg.

- update generation through the slave mode controller

refer to Timer app note: DM00042534.pdf

Timer synchronisation

A Master can control a slave Timer using a Trigger TRGO.

A Timer is slaved if its ITRx is connected to a Slave and the Master is set to use TRGO

Trigger outputs from the Master can be selected from:

- Reset:

- UG bit from EGR reg is used as TRGO

- Enable:

- Counter enable is used as TRGO.

- Used to start several timers at the same time or control window for Slave start

- Update:

- the update_event is TRGO.

- e.g. a master timer can act as a prescaler for a slave timer.

- Compare pulse:

- as soon as a capure or match occurs TRGO goes high when CC1IF flag is to be set

- OC1REF: use OC1REF as TRGO

- OC2REF: use OC2REF as TRGO

- OC3REF: use OC3REF as TRGO

- OC4REF: use OC4REF as TRGO

Master mode:

- Configure the Timer

- Select Trigger output to be used

- in CR2 reg - set MSM bits

- Enable Master/slave mode

- in SMCR reg - enable MSM bit

/*

* Trigger select mapping for slave timer from master timer. This is

* unfortunately not very straightforward; there's no tidy way to do this

* algorithmically. To avoid burning memory for a lookup table, use macros to

* compute the offset. This also has the benefit that compilation will fail if

* an unsupported master/slave pairing is used.

*

* Slave Master

* 1 15 2 3 4 (STM32F100 only)

* 2 9 10 3 4

* 3 9 2 11 4

* 4 10 2 3 9

* 9 2 3 10 11 (STM32L15x only)

* --------------------

* ts = 0 1 2 3

*/

#define STM32_TIM_TS_SLAVE_1_MASTER_15 0

#define STM32_TIM_TS_SLAVE_1_MASTER_2 1

#define STM32_TIM_TS_SLAVE_1_MASTER_3 2

#define STM32_TIM_TS_SLAVE_1_MASTER_4 3

#define STM32_TIM_TS_SLAVE_2_MASTER_9 0

#define STM32_TIM_TS_SLAVE_2_MASTER_10 1

#define STM32_TIM_TS_SLAVE_2_MASTER_3 2

#define STM32_TIM_TS_SLAVE_2_MASTER_4 3

#define STM32_TIM_TS_SLAVE_3_MASTER_9 0

#define STM32_TIM_TS_SLAVE_3_MASTER_2 1

#define STM32_TIM_TS_SLAVE_3_MASTER_11 2

#define STM32_TIM_TS_SLAVE_3_MASTER_4 3

#define STM32_TIM_TS_SLAVE_4_MASTER_10 0

#define STM32_TIM_TS_SLAVE_4_MASTER_2 1

#define STM32_TIM_TS_SLAVE_4_MASTER_3 2

#define STM32_TIM_TS_SLAVE_4_MASTER_9 3

#define STM32_TIM_TS_SLAVE_9_MASTER_2 0

#define STM32_TIM_TS_SLAVE_9_MASTER_3 1

#define STM32_TIM_TS_SLAVE_9_MASTER_10 2

#define STM32_TIM_TS_SLAVE_9_MASTER_11 3

STM32F4 Timer Internal Trigger Connection的更多相关文章

- Stop logging "internal dummy connection" in Apache

Apache 2.x keeps child processes alive by creating internal connections which appear in the log file ...

- 解决Apache日志"internal dummy connection"方法

最近查看服务器中apache日志,发现有大量的 OPTIONS * HTTP/1.0" 200 - "-" "Apache (internal dummy co ...

- STM32F4 Timer simplified block diagram

Timers TIM1 and TIM8 use 16-bit counters and are the most complex timers of all timers included in t ...

- (STM32F4) Timer Compare mode 操作

Timer 比較模式(compare) 具體會用在哪種狀況目前還沒有這種經驗,但Compare有配置功能pin想必有應用會用到這個模式 從Function Block來看比較模式比基本Timer多了比 ...

- (STM32F4) Timer 基本操作

Timer (計時器) 就是慢慢數時間,在timer內部有一個計數器. 而計數器會數到Register的value當數值數到設定值Timer就會發起IRQ 而程式就會轉跳到中斷向量裡頭去執行想要做的事 ...

- STM32F4 Timer External Clock TI2 Both Edges Demo

#define CLK_FREQ ( 10000 ) #define CORE_FREQ ( 168000000 ) static void TIM_GPIO_Config( void ) { GPI ...

- STM32 System and Timer Clock Configurations

STM32 System and Timer Clock Configurations I've started writing some software to drive a series of ...

- STM32 Timer Clock sources -- External Clock Both Edge

Timers get their clock source from External pins or Internal timer sources. External External = pins ...

- Advanced Replication同步复制实验(基于Trigger&基于Materialized View)

1. 高级复制和流复制介绍 1.1 高级复制(Advanced Replication) 高级复制也称为对称复制,分为多主体站点复制(Multiple Master Rplication).物化视图站 ...

随机推荐

- xmlhttprequest upload

html5 带进度上传 function fileSelected() { var file = document.getElementById('fileToUpload').files[0]; i ...

- Django进阶之缓存和信号

一.缓存 简介 由于Django是动态网站,所有每次请求均会去数据进行相应的操作,当程序访问量大时,耗时必然会更加明显,最简单解决方式是使用:缓存,缓存将一个某个views的返回值保存至内存或者mem ...

- 第一篇:初始Golang

Golang简介 编程语言已经非常多,偏性能敏感的编译型语言有 C.C++.Java.C#.Delphi和Objective-C 等,偏快速业务开发的动态解析型语言有PHP.Python.Perl.R ...

- ajax请求成功但不执行success-function回调函数的问题

在success:function(data){}下面加个error:function(){},看看是不是出错了走了error.如果是,说明返回值类型不符合要求. 比如:下面代码返回String类型. ...

- Ubuntu下SSH安装

step: 1.输入命令: sudo apt-get install openssh-server 2.验证sshserver是否启动了,以下两条命令均可 ps -e | grep ssh netst ...

- FormData介绍

FormData XMLHttpRequest Level 2添加了一个新的接口FormData.利用FormData对象,我们可以通过JavaScript用一些键值对来模拟一系列表单控件,我们还可以 ...

- js中ajax异步问题

1.JS的执行顺序问题 浏览器是按照从上到下的顺序解析页面,因此正常情况下,JavaScript脚本的执行顺序也是从上到下的,即页面上先出现的代码或先被引入的代码总是被先执行,即使是允许并行下载Jav ...

- Redis持久化存储(RDB和AOF)

参考了: https://blog.csdn.net/canot/article/details/52886923 和 https://www.cnblogs.com/zhangchao-letv/ ...

- Android Studio 3.0正式版填坑之路

原文:https://www.jianshu.com/p/9b25087a5d7d Android Studio 3.0启动图 序言 总看别人的文章,今天尝试着自己来写一篇.在逛论坛时候,无意间发 ...

- 【BZOJ】4380: [POI2015]Myjnie

题解 区间dp,先离散化所有价值 \(f[i][j][k]\)表示\([i,j]\)区间里最小值为\(k\)的价值最大是多少 只考虑\(i <= a <= b <= j\)的区间,枚 ...