调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下

编译

在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是编译所有文件,这里选择 Compile->Compile All,如下图所示;

在脚本窗口中将出现一行绿色字体

# Compile of altera_mf.v was successful.

# Compile of counter.v was successful.

# Compile of rom.v was successful.

# Compile of rom_top.v was successful.

# Compile of rom_tst.v was successful.,说明文件编译成功,在该文件的状态栏后有一绿色的对号,表示编译成功;

同时,状态那一栏出现两个问号变成了√,表明编译成功,没有语法错误。

添加仿真信号

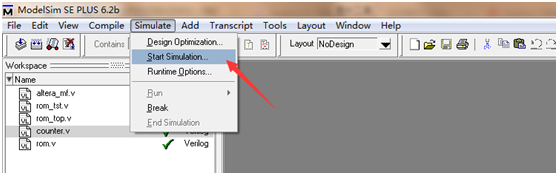

下面我们开始仿真,点击菜单 Simulate->start Simulate。

出现如下图所示的界面,展开 Design 选项卡下的 work 库,并选中其中的 rom_tst,这是在 Simulate 中出现了 work. rom_tst表示要仿真的对象,在优化那一栏不选择优化,如果选择优化的话,有些信号在仿真的时候会被优化掉,观察不了。点击 OK;

点击OK后,选中的仿真模块将会被加载到工程里面进行仿真,这里可能会出现错误,一般的问题是在testbench例化的模块名,模块信号有错误或者是信号参数有错误,如果出现错误则需要修改然后重新编译将待测试的模块加载到工程。

加载成功后,工程工作窗口会跳到sim窗口,会出现如下界面:

在sim窗口可以看到testbench设计的3个部分,初始化、always、例化的模块。这里需要观察的信号就是例化模块输出的信号,由此右击rom_top_1,选择add->add to wave,将待测试模块的信号添加到波形观察窗口中进行仿真观察。

添加后的wave窗口如下图所示

仿真开始

仿真可以采用窗口上的工具栏进行设置,如下图所示

同时也可以通过再脚本窗口输入运行时间后按下回车键进行运行:run 1ms,这里运行1ms。

仿真信号查看

仿真运行后,波形窗口会出现如下所示的信号。

这里选中信号counter_out、rom_data,右击如下图所示,设置信号显示的数制,这里选择无符号整形进行显示。

可以看到counter_out信号由0在每个时钟上升沿进行加一操作,在计数到255后重新再从0计数。rom_data则在每个时钟信号上升沿下将sin信号输出。

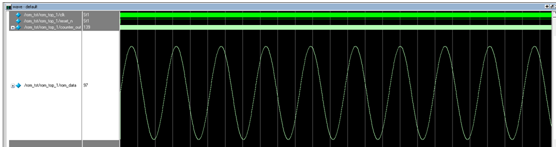

在信号显示中,有时为了观察信号更直接,需要将信号采用模拟的方式进行显示,modelsim软件可以满足这一要求,这里选中rom_data信号,右击如下图所示

将信号设置为模拟显示,接着弹出如下窗口,可以设置调整信号显示的幅值,这里默认原始值,点击ok。

最后还要设置下波形窗口中模拟信号显示所占有的宽度,以满足信号采用模拟显示后不会和其他信号显示重叠在一起。选择rom_data信号,右击如下图所示。

进行设置信号显示的格式,如下图所示,这里设置显示的高度为300,可以满足信号最大值255。

最后可以看到将rom_data显示为模拟信号会得到如下的结果。

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

调用altera IP核的仿真流程—下的更多相关文章

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- 基于modelsim-SE的简单仿真流程—下

基于modelsim-SE的简单仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile A ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- altera DDR2 IP核之仿真

在生成的IP核文件夹下,有一个testbench文件夹,里面包含了一个example测试激励和DDR2仿真模型. 如下 20 -rw-r--r-- 1 Administrator 197121 171 ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- altera ip 核小究

用quartus的MegaWizard工具生成一个乘法器multiplier,会在工程目录下产生 multiplier.qip (可选) multiplier_bb.v (可选) multip ...

- 基于modelsim-SE的专业进阶仿真流程

基于modelsim-SE的专业进阶仿真流程 通过<基于modelsim-SE的简单仿真流程>和<调用altera IP核的仿真流程>是否感受到仿真流程中的繁琐步骤,特别是在m ...

随机推荐

- Node学习笔记(二):事件驱动

接触Node,提得最多的可能就是回调,异步非阻塞处理,思前想后,JavaScript从前端语言过渡到服务器端,最大的劣势可能就是线程,当然这方面的不足现在也被慢慢弥补起来了(很多第三方的npm包可供下 ...

- 学习Redis你必须了解的数据结构——双向链表(JavaScript实现)

本文版权归博客园和作者吴双本人共同所有,转载和爬虫请注明原文链接 http://www.cnblogs.com/tdws/ 下午分享了JavaScript实现单向链表,晚上就来补充下双向链表吧.对链表 ...

- Vertical Menu ver4

以前一直使div来创建Vertical菜单,也曾有过3个版本.http://www.cnblogs.com/insus/archive/2011/10/19/2217314.html 现今Insus. ...

- Mybatis的choose when otherwise

<select id="getCount" resultType="int"> select count(1) from <choose> ...

- 开源跨平台IOT通讯框架ServerSuperIO,集成到NuGet程序包管理器,以及Demo使用说明

物联网涉及到各种设备.各种传感器.各种数据源.各种协议,并且很难统一,那么就要有一个结构性的框架解决这些问题.SSIO就是根据时代发展的阶段和现实实际情况的结合产物. 各种数据信息,如下图 ...

- Android Weekly Notes Issue #218

Android Weekly Issue #218 August 14th, 2016 http://androidweekly.net/issues/issue-218 ARTICLES & ...

- java web之个人通讯录系统

前天下了第一场雪,专业课老师给我们布置了一个期末小作业,真的感觉到寒假就要来临了.这个学期没过多久就要结束了.总结这学期,感觉还是有不少收获的.完成了当初许下的诺言,现在也越来越喜欢软件这个行业了,虽 ...

- Json对象与Json字符串互转(4种转换方式)

Json字符与Json对象的相互转换方式有很多,接下来将为大家一一介绍下,感兴趣的朋友可以参考下哈,希望可以帮助到你 1>jQuery插件支持的转换方式: 复制代码代码如下: $.parseJS ...

- 转载: 黄聪:C#中 Excel列字母与数字的转换

using System; using System.Collections.Generic; using System.Linq; using System.Text; using System.T ...

- Shell中字符串分割的三种方法

问题:对于’1,2,3,4,5’这样的字符串输出采用,分隔开的1 2 3 4 5 特征:在字符串中没有空格 解决方法1: #!/bin/bash var=’1,2,3,4,5’ var=${var// ...