EMC机理------串扰

转:电子工程师不得不知道的EMC机理------串扰(韬略科技EMC)

串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

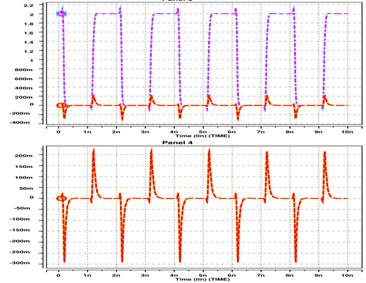

图1.串扰使得信号产生畸变

当串扰噪声叠加在受害信号的高低电平上时,会产生幅度噪声或影响眼图高度。当串扰噪声叠加在受害信号的跳变边沿位置时会产生边沿的抖动,进而影响时序或者是眼图宽度。从统计的角度来说,由于干扰源的不确定性,串扰噪声一般会同时影响信号的边沿和幅度。因此,对于串扰来说两个方面的影响都应该考虑。

串扰形成的根源在于耦合。在多导体系统中,导体间通过电场和磁场发生耦合。这种耦合会把信号的一部分能量传递到邻近的导体上,从而形成噪声。耦合的方式主要有两种:1、容性耦合。2、感性耦合。

容性耦合

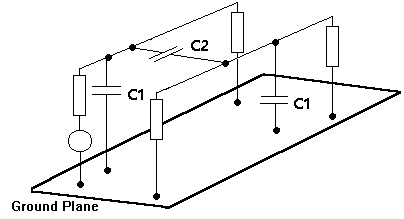

回忆一下我们所熟悉的平行板电容,两个规则平行板导体,周围充满介质就形成了一个电容器。对于PCB板上的情况,两条走线之间和参考平面之间也会形成电容器,图3中C1表示走线和参考平面之间形成的电容,C2表示两走线之间形成的电容。从电容的角度来看,当一条走线上电压变化时,相当于电容C2两端电压变化,电容C2充电邻近的导体(电容的另一端)上必然也会有电流,串扰随之产生。走线之间的电容与走线之间的间距密切相关,当间距增大时,耦合电容迅速减小,耦合作用急剧减弱。如果在两条走线之间放入另一根走线,这两跳走线之间耦合电容会进一步减小,这种现象正是使用隔离底线抑制串扰的出发点之一。

图2.容性耦合(Capacitivecoupling)

感性耦合

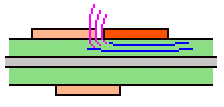

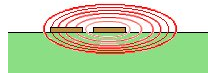

如果一条走线上有数字信号传输,在信号电平跳变过程中,即信号处于跳变边沿时,走线上电压不断变化,走线上的电流也不断变化,这样在走线周围产生变化的磁场,而变化的磁场在邻近走线上产生感应电流。这就是感性耦合。同样的拉开PCB板上走线的间距,能明显减小两天线之间的互感耦合。感性耦合机理如图3

图3.感性耦合(Inductive coupling

EMC机理------串扰的更多相关文章

- 设计上如何避免EMC问题

最近经常被问到EMC相关的问题,比如怎么设计才能避免EMC的问题,我想经常关注高速先生的同鞋们有机会肯定也会问到这个问题.首先这是一个系统 性的问题,不是那么好回答,尤其是对于聚焦在高速信号这个领域而 ...

- 高速PCB之EMC设计47则

高速PCB之EMC设计47则 差模电流和共模电流 辐射产生 电流导致辐射,而非电压,静态电荷产生静电场,恒定电流产生磁场,时变电流既产生电场又产生磁场.任何电路中存在共模电流和差模电流,差模信号携带数 ...

- EMC (电磁兼容性)

电磁兼容性EMC(Electro Magnetic Compatibility),是指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁干扰的能力.因此,EMC包括两个方面 ...

- 常见EMC疑问及对策

1. 在电磁兼容领域,为什么总是用分贝(dB)的单位描述?10mV是多少dBmV? 答:因为要描述的幅度和频率范围都很宽,在图形上用对数坐标更容易表示,而dB就是用对数表示时的单位,10mV是20dB ...

- EMC与电容(二)-电容参数意义、各电容的特点及应用

上次的问题,看到很多回答里都有关于X电容,Y电容,NPO之类,这些很奇怪的参数到底代表什么意义呢?以前很多次都在BOM表里看到这些参数,一直都无视过去,正好这次的EMC课程里也提到这方面的知识,正好跟 ...

- 电容与EMC-电容不同功能时对整板EMC的作用

一般我们的pcb板的器件有很多种类,但是值得特别关注的,很多人都会说是BGA.接口.IC.晶振之类,因为这些都是layout功能模块以及设计难点.然而数量上占绝对优势的器件却是阻容器件,之前围殴阻抗时 ...

- EMC与地之重新认识地

记得在Mark的培训中,他手上拿了一个无线鼠标,然后问了一个很有意思的问题:“这个无线鼠标的地在哪里?同样,我们的手机没有和任何大地有接 触,那么这个地又在哪里呢?”这个问题确实很有意思,也确实让人很 ...

- EMC学习之电磁辐射

我们在接触新鲜事物的时候,通常习惯用自己熟悉的知识去解释自己不熟悉的事物.EMC知识更多的涉及到微波和射频,对于像我这种专注于信号完整性而 对EMC知识知之甚少的菜鸟来说,最初也只能用SI的一些基础知 ...

- 特邀美国EMC实战专家Mark来华授课

“轻松搞定EMC-PCB和系统设计”课程介绍 本次课程特邀美国EMC领域权威专家Mark Montrose主讲,将涵盖满足产品电磁兼容性和信号完整性的基本原理.课程涉及多个领域,不仅仅针对PCB设计, ...

随机推荐

- How Many to Be Happy?

How Many to Be Happy? 时间限制: 1 Sec 内存限制: 128 MB 题目描述 Let G be a connected simple undirected graph wh ...

- request.setAttribute()、session.setAttribute()和request.getParameter()的联系与区别

1.session.setAttribute()和session.getAttribute()配对使用,作用域是整个会话期间,在所有的页面都使用这些数据的时候使用. 2.request.setAttr ...

- 享元模式FlyweightPattern(转)

解释一下概念:也就是说在一个系统中如果有多个相同的对象,那么只共享一份就可以了,不必每个都去实例化一个对象.比如说一个文本系统,每个字母定一个对象,那么大小写字母一共就是52个,那么就要定义52个对象 ...

- 解决mariadb数据库服务无法开启

我的系统Manjaro linux,安装的数据库为mariadb 10.1 1.安装数据库 pacman -S mariadb 2.配置数据库启动环境: mysql_install_db --user ...

- 初始化home目录

mkdir WORKM 公共资料 科学研究 临时文档 项目开发 正在学习 专职教学 自作文档

- 如何得知 GIC 的所有中斷

can get the supported GIC interrupts from the below adb command, adb root adb shell cat /proc/interr ...

- interview fb2

2014.7.8fb #include <iostream> using namespace std; struct TreeNode{ int val; TreeNode *left; ...

- ios开发某个页面横不过来屏幕的时候

某一个页面需要横屏,其他的页面任然保持竖屏需要以下关键的几个步骤: 1.修改系统代理方法的返回值 -(UIInterfaceOrientationMask)application:(UIApplica ...

- php基础 gd图像生成、缩放、logo水印和验证码

gd库是php最常用的图片处理库之一(另外一个是imagemagick),可以生成图片.验证码.水印.缩略图等等. 图像生成 <?php /* 用windows画图板画图 1.新建空白画布(指定 ...

- UVA 10976 Fractions Again?!【暴力枚举/注意推导下/分子分母分开保存】

[题意]:给你一个数k,求所有使得1/k = 1/x + 1/y成立的x≥y的整数对. [分析]:枚举所有在区间[k+1, 2k]上的 y 即可,当 1/k - 1/y 的结果分子为1即为一组解. [ ...