Verilog中的时间尺度与延迟

- 赋值延时分类:

- 根据信号类型可分为连续赋值延时和寄存器赋值延时,

- 根据延迟特性分为内部延迟和外部延迟

- 连续赋值时延:一般可分为普通赋值时延、隐式时延、声明时延;只有 外部时延。

- 寄存器赋值延时:只有在使用时可分为内部时延 和 外部时延, 但没有声明延时。

- 普通赋值时延

- 隐式延时声明:

- 变量声明延时

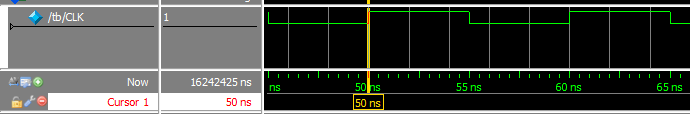

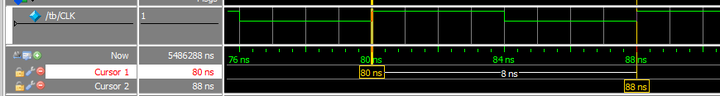

- 惯性延迟

Verilog中的时间尺度与延迟的更多相关文章

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- GCD中使用dispatch_after函数延迟处理任务

在实际的开发中,经常会遇到想要在指定的时间间隔后执行某个处理 <一>在GCD中提供了dispatch_after函数来完成这一操作 dispatch_after(dispatch_time ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 关于Verilog 中的for语句的探讨

在C语言中,经常用到for循环语句,但在硬件描述语言中for语句的使用较C语言等软件描述语言有较大的区别. 在Verilog中除了在Testbench(仿真测试激励)中使用for循环语句外,在Test ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- verilog中always块延时总结

在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论. 观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 . @2时刻, ...

- verilog中读取文件中的字符串_modelsim高级仿真

今天给个程序大家玩玩.因为今天遇到一个问题,就是要向UART发送指令,指令非常多,都是字符串.一直copy 函数 UART ("COMM_1"); UART ("COM ...

- verilog中的有符号数运算

verilog中的有符号数运算 http://hi.baidu.com/lixu1113/item/d00dc095f86aed48f142159a verilog中的有符号数运算 有符号数的计算:若 ...

随机推荐

- 什么是cache

什么是cacheTo minimize the quantity of control information stored, the spatial locality property is use ...

- Telnet登陆网络设备执行命令脚本

# !/usr//bin/python3 # -*- coding:UTF-8 -*- from telnetlib import Telnet import time, os, datetime, ...

- VS Code 快速下载

最近在官网下载Visual Studio Code时,下载速度特别慢,经过搜索后发现,将下载地址前部分更换为国内地址后,下载速度飞快. 具体步骤如下: VSCodeSetup-x64-1.72.0 官 ...

- WPF_MVVM框架(5)

1.NuGet引用MVVM框架包 引入该框架包之后, 默认会在目录下创建ViewModel层的示例代码 2.第二步, 通过在MainViewModel中创建一些业务代码, 将其与MainWindow. ...

- db2入门必看命令清单--日常运维必需

关注 推荐 嘉兴 视频 财经 科技 热点 国际 更多 搜索 34 消息 发布 5 2 收藏 分享 db2入门必看命令清单--日常运维必需 https://www.toutiao.c ...

- Oracle 存储过程4:PL/SQL动态执行DDL语句

- 更改svn地址

svn修改了服务器地址之后,本地要更新一下地址: 1. 在svn目录上右键,选TortoiseSVN->Relocate 2. 在To URL中填写新的地址,点击OK

- Kubernetes之Pod详解

1.Pod生命周期 pod创建 1. API Server 在接收到创建pod的请求之后,会根据用户提交的参数值来创建一个运行时的pod对象. 2. 根据 API Server 请求的上下文的元数据来 ...

- 图片转成gif 变成base64

html2canvas 截屏的插件 http://jnordberg.github.io/gif.js/ GIF.js官网 <script src='https://imgss.githu ...

- spring cloud 配置文件加密解密

1.底包 <dependency> <groupId>org.springframework.security</groupId> <artifact ...