FPGA内部IP核DDS

项目当中需要正弦信号与余弦信号,首先想到了DDS芯片,例如AD9833、AD9834。由于还需要用FPGA 做一些数据处理,后来干脆直接用FPGA 内部的DDSIP核,同时根据IP核内部的相位累加端口,设置触发信号,使得触发信号更加准时,并且通过PSD 算法计算有效值,相位差更小,精度更高。

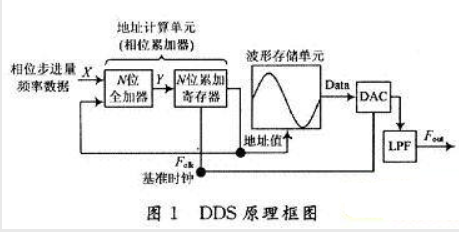

首先了解DDS的原理:

1、 DDS技术是根据奈奎斯特取样定律,从连续信号的相位出发,将正弦信号取样,编码,量化,形成一个正弦函数表,存在EPROM中,合成时,通过改变相位累加器的频率字来改变相位增量,也就是我们所称的步长。相位增量的不同导致一个周期内取样点的不同,在时钟频率即采样频率不变的情况下,通过相位的改变来改变频率。

2、 DDS 以数控振荡器的方式,产生频率、相位可控制的正弦,电路包括了基准时钟源、相位累加器、相位调制器、正弦ROM 查找表、D/A 转换 器和低通滤波器等。 频率控制字N 和相位控制字M 分别控制DDS 所输出的正弦波的频率和相 位。DDS 系统的核心是相位累加器,它由一个N 位累加器与N 位相位寄存器构成。时钟脉冲每触发一次, 累加器便将频率控制数据与相位寄存器输出的累加相位数据相加, 然后把相加后的结果送至相位寄存器的数据输入端。 相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端, 以使加法器在下一个时钟的作用下继续与频率控制数据相加。 这样, 相位累加器在参考时钟的作用下将进行线性相位累加, 当相位累加器累加满时, 就会产生一次溢出, 以完成一个周期性的动作, 这个周期就是DDS 合成信号的一个频率周期, 相位累加器的溢出频率就是DDS 输出的信号频率。 相位寄存器的输出与相位控制字相加, 结果作为正弦查找表的地址。 查找表由ROM 构成, 其内部存有一个完整周期正弦波的数字幅度信息, 每个查找表的地址对应正弦波中的一个相位点。 查找表把输入地址信息映射成正弦波幅度信号, 同时输出到D/A 转换器的输入端, 通过D/A 可将数字量形式的波形幅值转换成所要求的合成频率模拟量形式信号。 低通滤波器用于衰减和滤除不需要的取样分量, 以便输出频谱纯净的正弦波信号。

ISE DDS IP核设置如下图,输出正弦信号为12位,为了实现频率的高分辨率,需要将相位增加足够的小,因此相位宽度为33位。

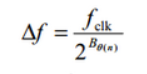

有DDS IP核datasheet当中,可以 看到分辨率计算公式、相位增量公式如下:

当输出38Khz正弦信号,频率分辨为0.01Hz,得到相位增量位宽为33位(50M/0.01=5000000000~~~~~~~BIT=33)

相位增量为38k*8589934592/50M=6528350。

wire [31:0] phase_out;

wire [32:0] poff_in;

assign poff_in = 33'd0;

wire [32:0] data_in; //DDS相位增量

assign data_in = 33'd6528350;

dds dds_inst_M0 (

.clk(clk), // input clk

.pinc_in(data_in), // input [32 : 0] pinc_in

.poff_in(poff_in), // input [32 : 0] poff_in

.cosine(cosine), // output [11 : 0] cosine

.sine(sine), // output [11 : 0] sine

.phase_out(phase_out) // output [32 : 0] phase_out

);

使用ModelSim仿真如下图

FPGA内部IP核DDS的更多相关文章

- 基于AXI4总线卷积FPGA加速IP核的尝试

本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面.使用的硬件平台是Zedboard. 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块 ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- FPGA VGA+PLL+IP核笔记

1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ.2.分辨率使用了800*600@72HZ.3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色.VGA图形基 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- 7 Series GTP IP核使用总结 IP核配置篇

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级.本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用.本文是 ...

- 7系列高速收发器总结 GTP IP核使用篇

上一篇7系列收发器博文讲解了GTP IP核的基本配置,本文继续分析如何将它使用起来.生成IP核后打开example design,先看看工程中包含的文件结构. 顶层文件下包含了gtp ip核系统顶层文 ...

- 浅析Xilinx 三速以太网MAC IP核

之前在使用Altera的三速以太网MAC IP的基础上,完成了UDP协议数据传输.此次为了将设计移植到xilinx FPGA上,需要用到xilinx的三速以太网MAC IP核,当然也可以自己用HDL编 ...

随机推荐

- 你真的了解CSS继承吗?看完必跪

也许你瞧不起以前的 css ,但是你不该再轻视眼下的 css .近年来 css 的变量系统已逐步得到各大浏览器厂商支持,自定义选择器等强势袭来,嵌套系统/模块系统也在路上…为了更好的掌握 css 这门 ...

- 新建maven项目总是需要重新选择maven的配置文件

解决办法: other settings->settings for new projects... 找到maven设置自己的目录和配置

- springboot集成springDataJpa

1.引用依赖 <!--spring-data-jpa--> <dependency> <groupId>org.springframework.boot</g ...

- CSS技术让高度自适应减少很多不必要的检测

高度自适应第一种情况 1.高度不去设置,或者高度设置auto 内容撑开父元素的高度.2.内容撑开父元素的高度 -> 最小高度的设置 min-height3.浮动元素添加高度自适应 -> 添 ...

- MySQL 事务 异常 事务隔离的级别

MySQL 事务 异常 事务隔离的级别 事务 在你操作数据库的同时,有可能其他用户还会不断地对数据进行增删改查操作.为了避免并行进行时出现混乱,就产生了"事务".事务就是要保证 ...

- Golden Tiger Claw,题解

题目链接 题目: 题意: 找到和最小的两个序列a,b满足对于任意i,j有a[i]+b[j]>=c[i][j](矩阵c给出). 分析: 首先很容易看出来要使这题要用KM算法,为啥呢?因为要最小化a ...

- 最大的位或 HDU - 5969 简单思维题

题目描述 B君和G君聊天的时候想到了如下的问题. 给定自然数l和r ,选取2个整数x,y满足l <= x <= y <= r ,使得x|y最大. 其中|表示按位或,即C. C++. ...

- Install-Package : 找不到程序包

将程序包源链接地址改为https://www.nuget.org/api/v2/即可.

- 你是如何理解Vue的响应式系统的

1.响应式系统简述: 任何一个 Vue Component 都有一个与之对应的 Watcher 实例. Vue 的 data 上的属性会被添加 getter 和 setter 属性. 当 Vue Co ...

- Spring-boot 启动报错 调试小技巧

描述: 我们在启动spring-boot,spring-cloud 项目时,是不是经常 遇到报错,但是在控制台 没有能找到 具体 报错信息,只是 提示,启动失败,缺乏具体的报错信息,这样就很不方便我们 ...