习题8 #第8章 Verilog有限状态机设计-1 #Verilog #Quartus #modelsim

1. 设计一个“111”串行数据检测器。要求是:当检测到连续3个或3个以上的“1”时输出为1,其他输入情况下输出为0。

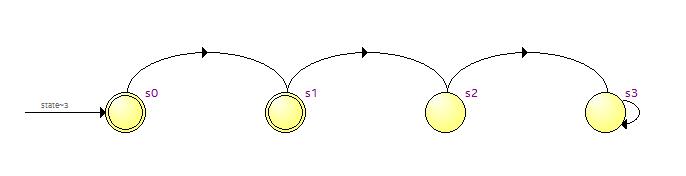

(1)思路分析:参照本章前文的范例,如第224页的【例8.8】,很容易模仿或推断出这个FSM共有4个状态,分别为:

初始化时收到0的s0,然后收到1的s1,连续收到两个1的s2,连续收到3个或更多个1的s3。状态之间的

转换也很简单,收到0就跳转到s0,收到1就按收到的连续个1的个数跳到相应的状态。

(2)111 序列检测电路的源码如下:

- 1 //detect 111

- 2 //2020-10-13

- 3 // by YongFengXie

- 4 module ex8_1(clk,rst_n,x,z);

- 5 input clk;

- 6 input rst_n;

- 7 input x;

- 8 output reg z;

- 9

- 10 reg [3:0] state;

- 11

- 12 parameter s0=4'b0001,

- 13 s1=4'b0010,

- 14 s2=4'b0100,

- 15 s3=4'b1000;

- 16

- 17 always @(posedge clk or negedge rst_n)

- 18 begin

- 19 if(!rst_n)

- 20 begin

- 21 state<=s0;

- 22 z<=1'b0;

- 23 end

- 24 else

- 25 case(state)

- 26 s0:begin

- 27 if(x==1'b0) //0

- 28 begin

- 29 state<=s0;

- 30 z<=1'b0;

- 31 end

- 32 else //1

- 33 begin

- 34 state<=s1;

- 35 z<=1'b0;

- 36 end

- 37 end

- 38 s1:begin

- 39 if(x==1'b0) //10

- 40 begin

- 41 state<=s0;

- 42 z<=1'b0;

- 43 end

- 44 else //11

- 45 begin

- 46 state<=s2;

- 47 z<=1'b0;

- 48 end

- 49 end

- 50 s2:begin

- 51 if(x==1'b0) //110

- 52 begin

- 53 state<=s0;

- 54 z<=1'b0;

- 55 end

- 56 else //111

- 57 begin

- 58 state<=s3;

- 59 z<=1'b1;

- 60 end

- 61 end

- 62 s3:begin

- 63 if(x==1'b0) //1110

- 64 begin

- 65 state<=s0;

- 66 z<=1'b0;

- 67 end

- 68 else //1111

- 69 begin

- 70 state<=s3;

- 71 z<=1'b1;

- 72 end

- 73 end

- 74 default:begin

- 75 state<=s0;

- 76 z<=1'b0;

- 77 end

- 78 endcase

- 79 end

- 80

- 81 endmodule

(3) 111序列检测电路的测试代码如下:

- //ex8_1 testbench

- //2020-10-13

- // by YongFengXie

- `timescale 1ns/1ns

- module ex8_1tb;

- reg clk;

- reg rst_n;

- reg x;

- wire z;

- ex8_1 ut(clk,rst_n,x,z);

- initial begin

- clk=1'b0;

- rst_n=1'b0;

- x=1'b0;

- #40 rst_n=1'b1;

- #10 x=1'b0;

- #10 x=1'b0;

- #10 x=1'b1;

- #10 x=1'b0;

- #10 x=1'b1;

- #10 x=1'b1;

- #10 x=1'b0;

- #10 x=1'b1;

- #10 x=1'b1;

- #10 x=1'b1;

- #10 x=1'b0;

- #10 x=1'b1;

- #10 x=1'b1;

- #10 x=1'b1;

- #10 x=1'b1;

- #300 $stop;

- end

- always #5 clk=~clk;

- endmodule

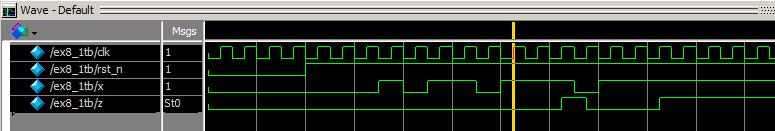

(4) 111序列检测电路的ModelSim仿真结果如图ex8_1_1所示:

图ex8_1_1 111序列检测电路仿真结果

(5) 111序列检测电路FSM状态转换图如图ex8_1_2所示:

图ex8_1_2 111序列检测电路的状态转换图

(6)总结:书上的范例(王金明 《数字系统设计与Verilog HDL》)皆为序列检测电路,所以很容易模仿。FSM的写法3段,2段,1段。

感觉简单的电路,1段搞定,时序逻辑的状态转换,组合逻辑的电路输出, 可以用固定的套路或模板。状态机的设计主要难

点还是在于规划好有几个状态,然后就是顺理成章的转换和输出,有熟练的模板,就直接套用了。

习题8 #第8章 Verilog有限状态机设计-1 #Verilog #Quartus #modelsim的更多相关文章

- [Python学习笔记][第五章Python函数设计与使用]

2016/1/29学习内容 第四章 Python函数设计与使用 之前的几页忘记保存了 很伤心 变量作用域 -一个变量已在函数外定义,如果在函数内需要修改这个变量的值,并将这个赋值结果反映到函数之外,可 ...

- 《.NET 设计规范》第 5 章:成员设计

<.NET 设计规范>第 5 章:成员设计 5.1 成员设计的通用规范 要尽量用描述性的参数名来说明在较短的重载中使用的默认值. 避免在重载中随意地改变参数的名字.如果两个重载中的某个参数 ...

- MySQL性能调优与架构设计——第 18 章 高可用设计之 MySQL 监控

第 18 章 高可用设计之 MySQL 监控 前言: 一个经过高可用可扩展设计的 MySQL 数据库集群,如果没有一个足够精细足够强大的监控系统,同样可能会让之前在高可用设计方面所做的努力功亏一篑.一 ...

- MySQL性能调优与架构设计——第 17 章 高可用设计之思路及方案

第 17 章 高可用设计之思路及方案 前言: 数据库系统是一个应用系统的核心部分,要想系统整体可用性得到保证,数据库系统就不能出现任何问题.对于一个企业级的系统来说,数据库系统的可用性尤为重要.数据库 ...

- MySQL性能调优与架构设计——第12章 可扩展设计的基本原则

第12章 可扩展设计的基本原则 前言: 随着信息量的飞速增加,硬件设备的发展已经慢慢的无法跟上应用系统对处理能力的要求了.此时,我们如何来解决系统对性能的要求?只有一个办法,那就是通过改造系统的架构体 ...

- 《C++Primer》第五版习题答案--第三章【学习笔记】

[C++Primer]第五版[学习笔记]习题解答第三章 ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/10 第三章:字符串,向量和数组 ...

- 《C++Primer》第五版习题解答--第四章【学习笔记】

[C++Primer]第五版习题解答--第四章[学习笔记] ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/11 第四章:表达式 练习4. ...

- 《C++Primer》第五版习题答案--第五章【学习笔记】

<C++Primer>第五版习题答案--第五章[学习笔记] ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/15 第五章:语句 ...

- 《C++Primer》第五版习题答案--第六章【学习笔记】

<C++Primer>第五版习题答案--第六章[学习笔记] ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/16 第六章:函数 ...

- FPGA Prototyping By Verilog Examples第五章 状态机FSM设计

上升沿检测电路之Moore型FSM // Listing 5.3module edge_detect_moore ( input wire clk, reset, input wire level, ...

随机推荐

- JS 为什么0==““ 会是true

0 是逻辑的 false 1 是逻辑的 true空字符串是逻辑的 false null 是逻辑的 false NaN==任何 都是false 所以:空字符串是逻辑的 false , 0是逻辑的fals ...

- C++设计模式 - 观察者模式(Observer)

组件协作模式: 现代软件专业分工之后的第一个结果是"框架与应用程序的划分","组件协作"模式通过晚期绑定,来实现框架与应用程序之间的松耦合,是二者之间协作时常用 ...

- 为什么js项目中金额强烈推荐使用分而不是元

相信我们都已经知道在js中浮点数据精度的问题了 看下面的例子 0.1 + 0.2 0.30000000000000004 如何解决呢? 在前后端交互过程中统一使用分为单位进行通讯,在最后的表示层处理为 ...

- #搜索,计算几何#JZOJ 4016 圈地为王

题目 在\(n\)行\(m\)列的网格中,你要圈一些地. 你从左上角出发,最后返回左上角,路径内部的区域视为被你圈住. 你不可以进入网格内部, 只能在边上行走. 你的路径不能在左上角以外自交, 但是边 ...

- #Splay#洛谷 1486 [NOI2004]郁闷的出纳员

题目 分析 考虑加减工资直接打标记,查询第\(k\)多可以用平衡树, 删除有点恶心,这里考虑Splay,将需要删除的部分的后继splay到根节点并将左子树断边 代码 #include <cstd ...

- 三步就能在OpenHarmony中实现车牌识别

介绍 本车牌识别项目是基于开源项目 EasyPR(Easy to do Plate Recognition)实现.EasyPR 是一个开源的中文车牌识别系统,基于 OpenCV 开源库开发. 本项目使 ...

- MongoDB命令行交互

命令行交互 命令行交互一般是学习数据库的第一步,不过这些命令在后续用的比较少,了解即可. 角色命令 创建角色 use admin db.createUser({"user": &q ...

- HDC2021技术分论坛:ArkUI 3.0让多设备开发更简单!

作者:wanglei,华为UI编程框架技术专家 HarmonyOS自诞生以来,就是为满足分布式多设备应用场景而设计的,大到智慧屏.车机.平板,小到手机.手表.在多设备场景下进行应用UI界面开发,面临新 ...

- Spring Cloud Sleuth:分布式请求链路跟踪

Spring Cloud Sleuth:分布式请求链路跟踪 SpringCloud学习教程 SpringCloud Spring Cloud Sleuth 是分布式系统中跟踪服务间调用的工具,它可以直 ...

- 接口API用例自动转locust测试用例

做接口测试是必要的,写完接口测试用例,再写locust压测脚本,其实差异不大: 写个简单的py,把接口测试脚本转为locust压测脚本,本例只是简单的示范: 原接口校验脚本: 1 # -*- codi ...