SWD and JTAG selection mechanism

SWD and JTAG selection mechanism

SWJ-DP enables either an SWD or JTAG protocol to be used on the debug port.

To do this, it implements a watcher circuit that detects a specific 16-bit selection sequence on the SWDIOTMS pin:

A 16-bit sequence is used to switch from JTAG to SWD operation

Another 16-bit sequence is used to switch from SWD to JTAG.

The switcher defaults to JTAG operation on power-on reset,

therefore the JTAG protocol can be used from reset without sending a selection sequence.

Switching from one protocol to the other can only occur when the selected interface is in its reset state.

JTAG must be in its Test-Logic-Reset (TLR) state and SWD must be in line-reset.

The SWJ-DP contains a mode status output, JTAGNSW,

that is HIGH when the SWJ-DP is in JTAG mode and LOW when in SWD mode. This signal can be used to:

disable other TAP controllers when the SWJ-DP is in SWD mode, for example by disabling TCK or forcing TMS HIGH

multiplex the Serial Wire output, TRACESWO, on to another pin such as TDO when in SWD mode.

Another status output, JTAGTOP, indicates the state of the JTAG-DP TAP controller. These states are:

Test-Logic-Reset

Run-Test/Idle

Select-DR-Scan

Select-IR-Scan.

This signal can be used with JTAGNSW to control multiplexers so that,

for example, TDO and TDI can be reused as General Purpose Input/Output (GPIO) signals when the device is in SWD mode.

The watcher block puts itself to sleep when it has finished tracking a specific sequence and only wakes up again

when it detects the next reset condition.

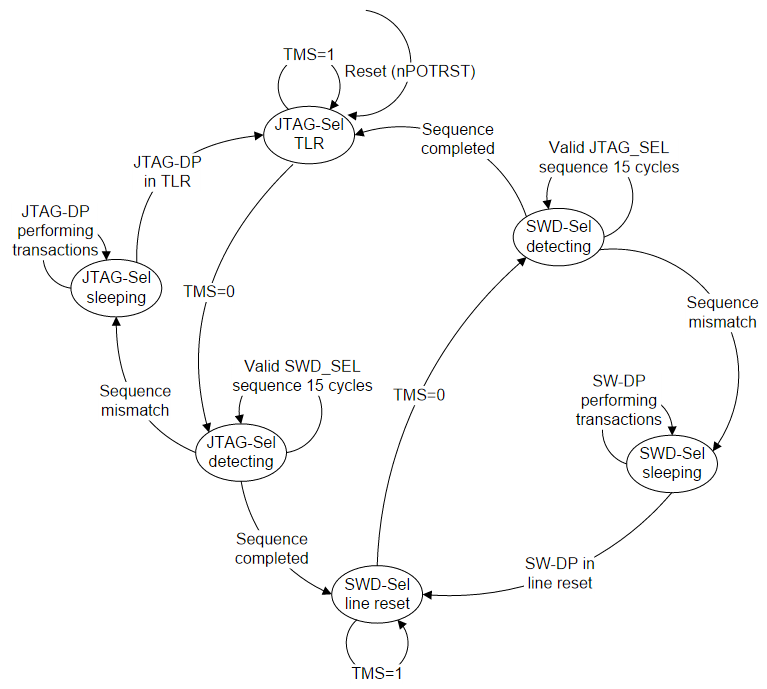

Figure 2.3 is a simplified state diagram that shows how the watcher transitions between sleeping, detecting, and selection states.

Figure 2.3. SWD and JTAG select state diagram

SWJ-DP switching sequences

The SWJ-DP switching sequences are described in:

JTAG to SWD switching

SWD to JTAG switching.

JTAG to SWD switching

To switch SWJ-DP from JTAG to SWD operation:

Send more than 50 SWCLKTCK cycles with SWDIOTMS=1.

This ensures that both SWD and JTAG are in their reset statesSend the 16-bit JTAG-to-SWD select sequence on SWDIOTMS

Send more than 50 SWCLKTCK cycles with SWDIOTMS=1.

This ensures that if SWJ-DP was already in SWD mode,

before sending the select sequence, the SWD goes to line reset.Perform a READID to validate that SWJ-DP has switched to SWD operation.

The 16-bit JTAG-to-SWD select sequence is defined to be 0b0111100111100111, MSB first.

This can be represented as 16'h79E7 if transmitted MSB first or 16'hE79E if transmitted LSB first.

This sequence has been chosen to ensure that the SWJ-DP switches to using SWD

whether it was previously expecting JTAG or SWD.

As long as the 50SWDIOTMS=1 sequence is sent first,

the JTAG-to-SWD select sequence is benign to SW-DP,

and is also benign to SWD and JTAG protocols used in the SWJ-DP,

and any other TAP controllers that might be connected to SWDIOTMS.

SWD to JTAG switching

To switch SWJ-DP from SWD to JTAG operation:

Send more than 50 SWCLKTCK cycles with SWDIOTMS=1.

This ensures that both SWD and JTAG are in their reset states.Send the 16-bit SWD-to-JTAG select sequence on SWDIOTMS.

Send at least five SWCLKTCK cycles with SWDIOTMS=1.

This ensures that if SWJ-DP was already in JTAG mode

before sending the select sequence, it goes into the TLR state.Set the JTAG-DP IR to READID and shift out the DR to read the ID.

The 16-bit JTAG-to-SWD select sequence is defined to be 0b0011110011100111, MSB first.

This can be represented as 16'h3CE7 if transmitted MSB first or 16'hE73C if transmitted LSB first.

This sequence has been chosen to ensure that the SWJ-DP switches to using JTAG

whether it was previously expecting JTAG or SWD.

If theSWDIOTMS=1 sequence is sent first, the SWD-to-JTAG select sequence is benign to SW-DP,

and is also benign to SWD and JTAG protocols used in the SWJ-DP,

and any other TAP controllers that might be connected to SWDIOTMS.

Restriction on switching

It is recommended that when a system is powered up, a debug connection is made, and the mode is selected,

either SWD or JTAG, that the system remains in this mode throughout the debug session.

Switching between modes must not be attempted while any component of the DAP is active.

If you attempt to switch between modes while any component of the DAP is active,

there can be unpredictable results.

A power-on reset cycle might be required to reset the DAP before switching can be retried.

SWD and JTAG selection mechanism的更多相关文章

- 浅论各种调试接口(SWD、JTAG、Jlink、Ulink、STlink)的区别

JTAG协议 JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试.现在多数的高级器件都支持JTAG协 ...

- jlink的SWD与JTAG下载模式的对应接线方法

参考博客:http://blog.csdn.net/qq_26093511/article/details/59484249 (1)如果用jtag模式下载的话需要接线: jlink ...

- STM32的JTAG、SWD和串口下载的问题

最近有一个项目用到STM32,为了使PCB布线方便一些所以改了一些引脚,占用了JTAG接口的PA15和PB3,所以要禁用一下JTAG,下载采用SWD模式.这样在实际操作中做出一些总结(方法网上都有.这 ...

- SWD模式和JTAG模式

一.功能 SWD模式:仿真 下载 JTAG模式:仿真 下载 二.接口 1.J-link JTAG/SWD接口 2.开发板接口电路 ①SWD模式 4根线(包片机) ②JTAG模式 20脚JTAG(网络) ...

- STM32 ~ JTAG、SWD和串口下载的问题

最近有一个项目用到STM32,为了使PCB布线方便一些所以改了一些引脚,占用了JTAG接口的PA15和PB3,所以要禁用一下JTAG,下载采用SWD模式.这样在实际操作中做出一些总结(方法网上都有.这 ...

- Serial Wire Debug (SWD) Interface -- PSoc5

PSoC 5 supports programming through the serial wire debug (SWD) interface. There are two signals in ...

- SWD烧录/仿真方式

单片机在烧写/仿真的时候具有一种方式叫做SWD,这种方式只用到两根线SWDIO,SWCLK.一般SWD和JTAG中的JTMS和JTCK共用的.由于线少,所以使用非常方便,但是速率相对较低. 在接线时, ...

- Introduction to Cortex Serial Wire Debugging

Serial Wire Debug (SWD) provides a debug port for severely pin limited packages, often the case for ...

- ARM Cortex Design Considerations for Debug

JTAG was the traditional mechanism for debug connections for ARM7/9 parts, but with the Cortex-M fam ...

随机推荐

- kernel——make menuconfig的实现原理【转】

转自:https://blog.csdn.net/hpr1992/article/details/41048693 .系统移植可以分为配置系统和编译系统两大块,其中通过命令makemenuconfig ...

- 点击超链接打开本地QQ

2014年6月4日 10:20:18 张志斌 这个功能实际上是属于腾讯的推广项目"一键加群"功能: http://qun.qq.com/join.html 用户必须有自己的群,登录 ...

- node.js模块、包

创建模块 Node.js 提供了 exports 和 require 两个对象,其中 exports 是模块公开的接口,require 用于从外部获取一个模块的接口,即所获取模块的 exports 对 ...

- wpf 用户自定义事件传参

//自定义传参 ,对外联系的参数 public class ImageZoomChangedEventArgs : RoutedEventArgs { /// <summary> /// ...

- CSS font-family 字体介绍,\5b8b\4f53 表示“宋体”

font-family采用一种"回退"的形式来保存字体,可以写若干种字体.当第一种字体浏览器不支持的时候,会找第二种字体,一次类推. font-family字体分为两类: 特殊字体 ...

- 如何在CI中写工具类,在哪个目录写

在Libraries目录写工具类,可以参考项目中七牛的集成写法 而Helps目录写的是辅助函数(公共函数)这一类的

- 【BZOJ】4292: [PA2015]Równanie

题解 \(f(n)\)的取值范围最多\(9^2 * 18\) 直接枚举判断就好 代码 #include <bits/stdc++.h> #define fi first #define s ...

- SpringMVC框架02——SpringMVC的Controller详解

1.基于注解的控制器 1.1.@Controller 注解类型 在SpringMVC中使用org.springframework.stereotype.Controller注解类型声明某类的实例是一个 ...

- WebSocket In ASP.NET Core(一)

.NET-Core Series Server in ASP.NET-Core DI in ASP.NET-Core Routing in ASP.NET-Core Error Handling in ...

- View初探

View初探 学习自 <Android开发艺术探索> View漫谈 Activity构成了我们的界面但是知识一个空壳子,Activity与View相结合才构成了我们丰富多彩的界面,并且为了 ...