USB小白学习之路(11) Cy7c68013A驱动电路设计注意事项(转)

Cy7c68013A驱动电路设计注意事项

转自:http://group.chinaaet.com/116/79029#0-tsina-1-71467-397232819ff9a47a7b7e80a40613cfe1

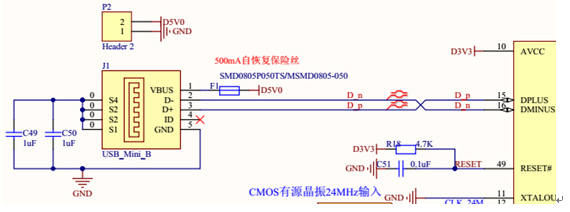

CY7C68013的驱动电路非常简单,除了提供24MHz时钟源,设计好USB差分接口,做好电源滤波,其他信号均可由数字控制。这里简单的对Bingo设计CV7C68013A-56PVXC驱动电路进行介绍,如下所示:

(1)首先,USB差分电路设计的好坏,决定了实际能运行的速率。

采用USB-Mini接口进行68013的通信,同时完成板卡的供电功能。USB理论上能提供500mA的电流,2.5W的功率足够支撑板卡的工作。同时500mA自恢复保险丝的设计,有效的保护了PC USB接口的安全。

在Layout D+、D- USB差分信号线的时候,一定要特别注意走线。

此外,外壳通过1uF接地,简单而有效的进行了电路的ESD保护。

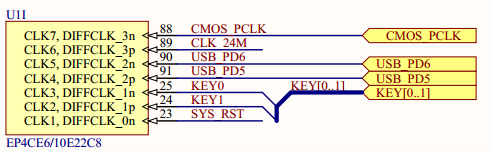

(2)通过FPGA输入24MHz有源时钟,如下:

实际上可以采用无源晶振,同时通过XTALOUT输出24MHz给FPGA作为全局时钟,进一步降低PCB设计的成本。

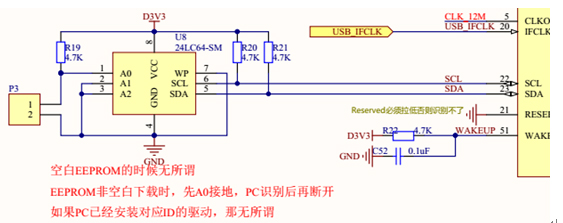

(3)CY7C68013A配置芯片24LC64 EEPROM,

注意上拉电阻!

另外:如果EEPROM非空,或者说当前固件本机未安装驱动,可以通过短接P3,来实现68013上电从内部启动。当然如果是全新的片子,一些无所谓了。

(4)复位引脚的配置

理论上68013的复位引脚直接高电平即可,但实际上经过多次的测试,发现RESET外接耦合电容,否则68013没有100%的成功率能完整正常启动,。这仅是经验总结,因此这一部分电路千万不要偷懒,如下所示:

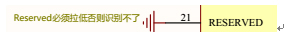

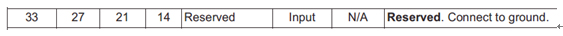

(5)坑爹的RESERVED设置

此外,最坑爹的RESERVED虽说是预留引脚,但是却不能NC。手册明文规定必须拉低,否则PC无法识别68013!

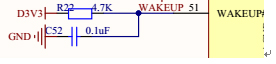

(6)WAKEUP功能时钟上啦,我们不做产品,不许睡觉!

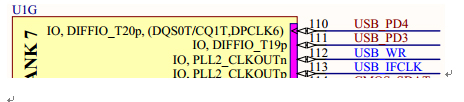

(7)同步时钟IFCLK由外部FPGA输入,如下(12MHz输出可用与验证IC是否正常工作):

(8)选择FIFO0,不允许数据输出,屏蔽数据读取,不进行包传输,EmptyY与Full功能暂时不用,片选始终有效,WR使能信号由外部FPGA输入,配置如下:

这样做完全是由于TQFP144的FPGA引脚资源有限,通过固定的配置,换来了功能的实现。如果FPGA有足够的IO,可以讲这些68013这些固定引脚较直接通过FPGA进行灵活的配置。

这里USB_WR作为同步FIFO数据写入使能信号,由FPGA控制。

此外,设计中没有引出FLAGB(FULL)、FLAGC(EMPTY)引脚,不仅仅由于FPGA引脚的有限,设计中可以直接忽略FLAGB、FLAGC的技巧,在于降低数据的写入速率。实际上经验告诉我们,写入30FPS的640*480的视频,即12MHz的速率进行写入,可以完全忽略FULL、EMPTY信号。因为68013完全有这个能力在这段时间处理好数据的缓存、发送,我们可以接受这个风险!!!

(当然这是迫不得已的……)

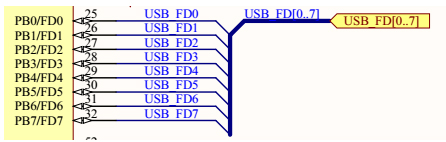

(9)这里FIFO选择了8Bit输出,如下所示:

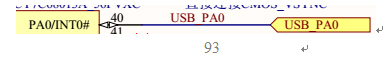

(10)PA0中断输入CMOS帧信号,用来同步数据,如下:

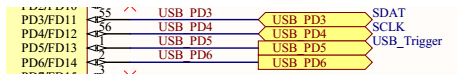

(11)PD5作为触发写入的信号,连接至FPGA作为输出使能,如下所示:

这里PD3、PD4、PD6实际上没有使用到。PD3、PD4用于用户采用68013实现CMOS Sensor的初始化接口,此设计中这两个IO没有使用到,PD6为预留。

(12)PD5、PD6从FPGA全局时钟数据,这里主要使用了PD5-USB_Trigger写入触发使能信号,如下:

(13)PD3、PD4预留(暂时没用到)初始化接口直接输入FPGA;68013 同步时钟信号IFCLK、写入使能信号WR直接从FPGA IO输出,如下所示:

USB小白学习之路(11) Cy7c68013A驱动电路设计注意事项(转)的更多相关文章

- USB小白学习之路(10) CY7C68013A Slave FIFO模式下的标志位(转)

转自良子:http://www.eefocus.com/liangziusb/blog/12-11/288618_bdaf9.html CY7C68013含有4个大端点,可以用来处理数据量较大的传输, ...

- USB小白学习之路(12) Cy7c68013A固件之Slave FIFO(转)

Cy7c68013固件之Slave FIFO 转自:http://blog.csdn.net/zengshaoqing/article/details/53053539 选择SlaveFIFO传输方式 ...

- USB小白学习之路(8)FX2LP cy7c68013A——Slave FIFO 与FPGA通信(转)

此博客转自CSDN:http://blog.csdn.net/xx116213/article/details/50535682 这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY ...

- USB小白学习之路(1) Cypress固件架构解析

Cypress固件架构彻底解析及USB枚举 1. RAM的区别 56pin或者100pin的cy7c68013A,只有内部RAM,不支持外部RAM 128pin的cy7c68013A在pin脚EA=0 ...

- USB小白学习之路(6) IIC EEPROM读取解析

IIC EEPROM读取解析 1. 编译错误处理(这里可以忽略) 在解压包解压了程序后,直接编译,出现如下错误. *** WARNING L14: INCOMPATIBLE MEMORY MODEL ...

- USB小白学习之路(3) 通过自定义请求存取外部RAM

通过自定义请求存取外部RAM 1. 实验简述 此实验是对自定义的供应商特殊命令(vendor specific command bRequest = 0xA3)进行解析,程序中的read me说明如下 ...

- USB小白学习之路(5) HID鼠标程序

HID鼠标程序 1. 特别注意 需要特别注意,各个例程中的设备描述符,配置描述符等各种描述符都是已经配置好了的,我们需要做的只是在例程中将代码修改为自己需要的部分即可,一般情况下是不可以串搭配的. 2 ...

- USB小白学习之路(4)HID键盘程序

HID键盘程序 1. 特别注意 需要特别注意,各个例程中的设备描述符,配置描述符等各种描述符都是已经配置好了的,我们需要做的只是在例程中将代码修改为自己需要的部分即可,一般情况下是不可以串搭配的. 2 ...

- USB小白学习之路(2)端点IN/OUT互换

端点2(out)和端点6(in)的out_in互换 注:这里的out和in都是以host为标准说的,out是host的out,在设备(Cy7c68013)这里其实是输入端口:in是host的in,在设 ...

随机推荐

- docker里修改时间

在docker容器里,你会发现,你根本无法通过命令修改时间.这时我们就可以通过/etc/localtime这个配置文件修改时间了.但这个配置文件是一个二进制的文件,里面根本就是一堆乱码.所以我只好拷贝 ...

- Web Service概述 及 应用案例

Web Service的定义 W3C组织对其的定义如下,它是一个软件系统,为了支持跨网络的机器间相互操作交互而设计.Web Service服务通常被定义为一组模块化的API,它们可以通过网络进行调用 ...

- Windows_Management_Instrumentation

WMI是管理系统中的核心 使用本工具的前提是:系统的服务列表中,Windows_Management_Instrumentation(winmgmts)这个服务处于运行状态.如果处于关闭状态,请在运行 ...

- 多对多表创建、forms组件、cookie与session

多对多表的三种创建方式 1.全自动(较为推荐) 优势:不需要你手动创建第三张表 不足:由于第三张表不是你手动创建的,所以表字段是固定的无法扩展 class Book(models.Model): ti ...

- [LC] 15. 3Sum

Given an array nums of n integers, are there elements a, b, c in nums such that a + b + c = 0? Find ...

- Hypothesis Tests for One Population Mean When σ Is Known

9.5 Hypothesis Tests for One Population Mean When σ Is Known 使用z-test前提(同使用mean distribution之前的考虑) 在 ...

- [LC] 71. Simplify Path

Given an absolute path for a file (Unix-style), simplify it. Or in other words, convert it to the ca ...

- cashier|gasoline|reservoir

N-COUNT 出纳(员);收银员A cashier is a person who customers pay money to or get money from in places such a ...

- 《Java 面试问题 一 Spring 、SpringMVC 、Mybatis》

自己理解SSM框架可能问到的面试问题 一.需要知道的SSM基础知识 1.什么是Spring? Spring 是一款轻量级的 IOC (依赖反转) 和 APO (面向切面) 容器框架.(个人理解: 就 ...

- BZOJ 1~10 精简题解

从这星期起,我开始了怒刷BZOJ的旅程.这几天刷了10道题(由于"档期"的原因,所以有几道题没打完-..捂脸--..) 精简题解: 1000 A+B Problem --.. [B ...