zedboard通过BRAM实现PS和PL的简单通信

使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。

本文所使用的开发板是zedboard

PC 开发环境版本:Vivado 2016.2 Xilinx SDK 2016.2

---------------------

作者:wangdaling

来源:CSDN

原文:https://blog.csdn.net/rzjmpb/article/details/50365915 https://blog.csdn.net/rzjmpb/article/details/50365915

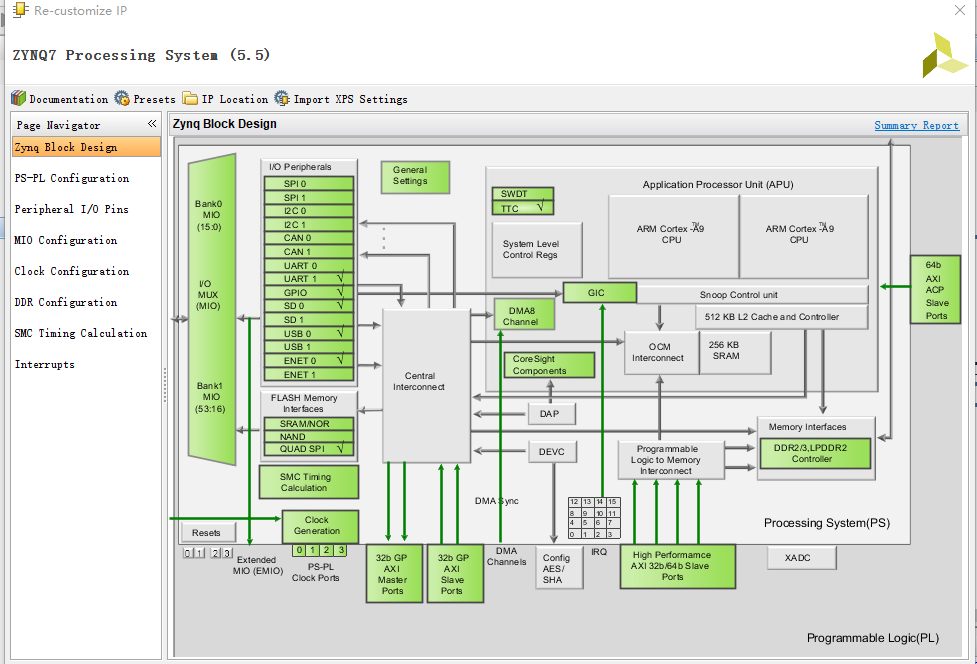

一、实现的结构原理图

1、PL端硬件架构搭建

新建工程后在Create Block Design中添加IP,点击添加IP的按钮后在弹出的搜索框中搜索ZYNQ时添加PS,搜索BRAM时添加AXI BRAM Controller 和Block Memory Generator,然后对PS中的相应接口做参数设置

2、软件SDK中的代码如下:

#include <stdio.h>

#include "platform.h"

#include "xparameters.h"

#include"xparameters_ps.h"

#include"xil_printf.h"

#include"xil_io.h"

//#define DDR_BASEARDDR XPAR_DDR_MEM_BASEADDR+0x10000000

int main()

{

init_platform();

int i;

int rev;

xil_printf("-----The test is start...\n\r");

for(i=0;i<15;i++)

{

Xil_Out32(XPAR_BRAM_0_BASEADDR+i*4,0x10000000+i);

}

for(i=0;i<15;i++)

{

rev=Xil_In32(XPAR_BRAM_0_BASEADDR+i*4);

xil_printf("the address at %x data is: %x \n\r",XPAR_BRAM_0_BASEADDR+i*4,rev);

}

xil_printf("-----The test is end!-------\n\r");

cleanup_platform();

return 0;

}

3、编译软件部分的代码,

4、将zedboard 板子的JTAG和PROG的端口与PC电脑端相连

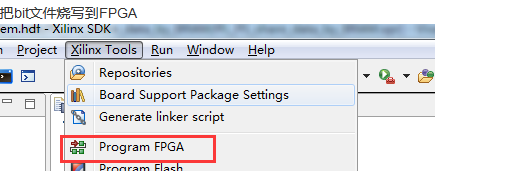

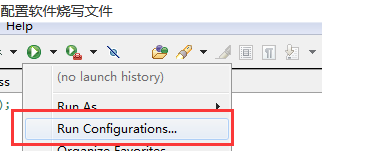

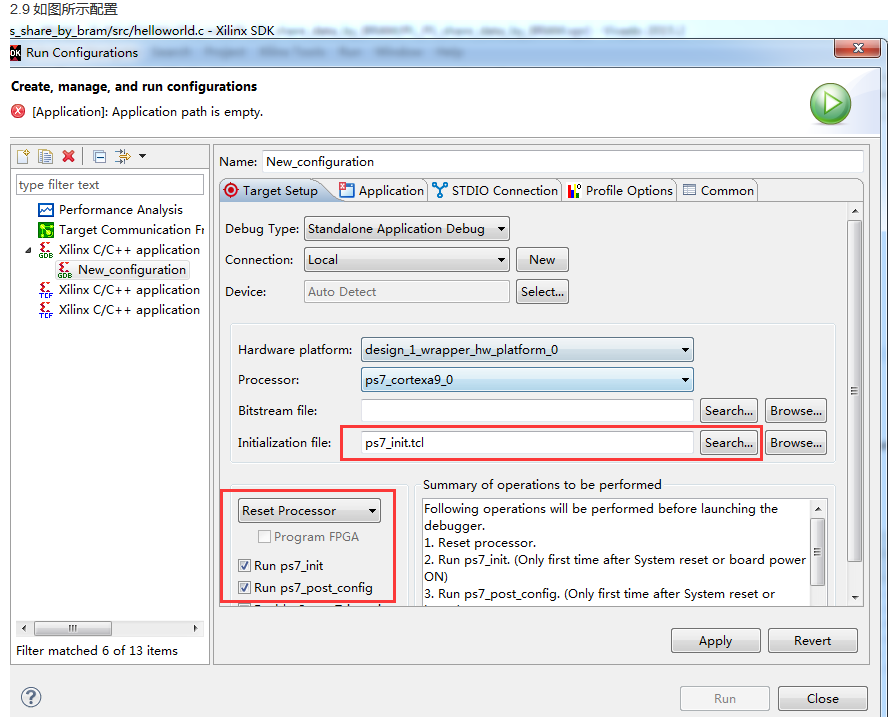

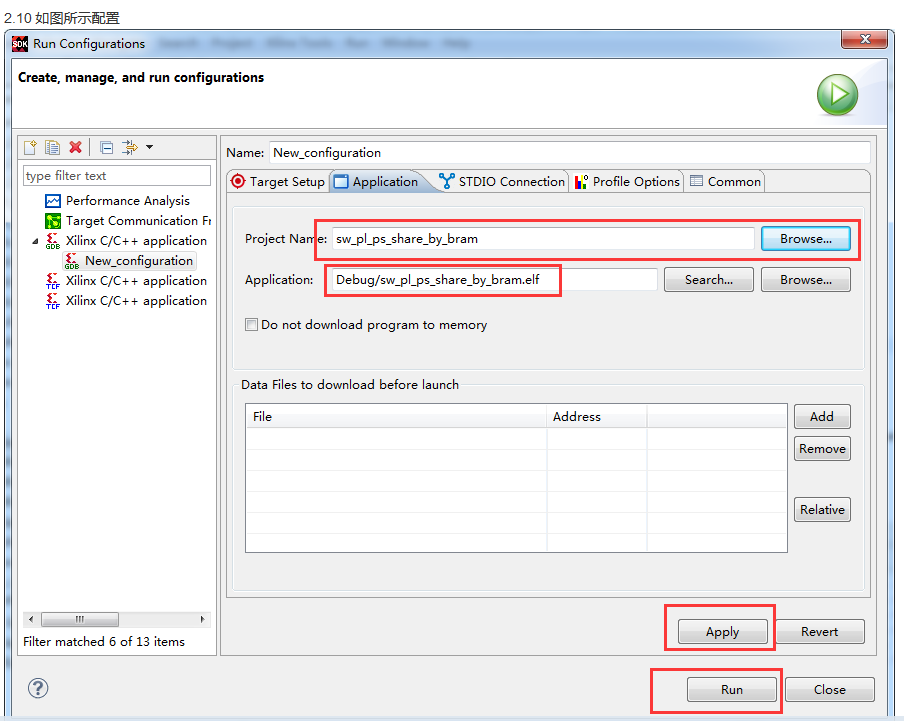

5、然后program FPGA(从硬件部分生成的bitstream),run configuration,run

zedboard通过BRAM实现PS和PL的简单通信的更多相关文章

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- Zedboard学习(三):PL下流水灯实验 标签: fpgazynqPL 2017-07-05 11:09 21人阅读 评论(0)

zynq系列FPGA分为PS部分和PL部分. PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分. PS: 处理系统 (Processing System) , 就是与F ...

- 使用axi_datamover完成ZYNQ片内PS与PL间的数据传输

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1.传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送: 2.PL端接口为FIFO接口: PS到PL的数据传输流程: PS到 ...

- [原创]基于Zynq PS与PL之间寄存器映射 Standalone & Linux 例程

基于Zynq PS与PL之间寄存器映射 Standalone & Linux 例程 待添加完善中

- Zynq PS和PL间的连接

跨越PS和PL的信号 AXI总线.EMIO.其他(看门狗.重启信号.中断信号.DMA接口信号) AXI标准 AXI(高级可扩展接口)是ARM AMBA的一部分.AMBA总线主要用于片上系统.AXI总线 ...

- PS与PL协同设计

https://blog.csdn.net/Fei_Yang_YF/article/details/79676172 什么是PS和PL ZYNQ-7000是Xilinx推出的一款全可编程片上系统(Al ...

- zedboard学习记录.2.PS+PL 流水灯与uart

1.建立一个工程. 硬件设计 2.IP integrator -> create block desgin;Run Block Automation. 3.add IP -> AXI GP ...

- Vivado设计二:zynq的PS访问PL中的自带IP核(基于zybo)

1.建立工程 首先和Vivado设计一中一样,先建立工程(这部分就忽略了) 2.create block design 同样,Add IP 同样,也添加配置文件,这些都和设计一是一样的,没什么区别. ...

随机推荐

- lwip的内存管理

lwip可以不用malloc,而完全用pool,全用全局变量,没看明白怎么实现的. #if LWIP_NETCONN || LWIP_SOCKET LWIP_MEMPOOL(NETBUF, MEMP_ ...

- mysql 启动,停止,重启

启动mysql: 方式一:sudo /etc/init.d/mysql start 方式二:sudo start mysql 方式三:sudo service mysql start sudo ./ ...

- 解决shiro自定义filter后,ajax登录无法登录,并且无法显示静态资源的问题

这个问题困扰了我一天,看了下面两个文章,豁然开朗: https://www.cnblogs.com/gj1990/p/8057348.html https://412887952-qq-com.ite ...

- vue-cli搭建vue项目(单页面应用)

1.全局安装vue-cli 2.创建项目: vue init webpack test test是项目名称,会在当前工作目录下新建一个test文件夹 接下来会手动选择一些配置 除了Setup unit ...

- HTTP 1.1状态代码及其含义

HTTP 1.1状态代码及其含义 100 Continue 初始的请求已经接受,客户应当继续发送请求的其余部分.(HTTP 1.1新) 101 Switching Protocols 服务器将 ...

- 加密算法极先锋之MD5算法

在开发过程中,避免不了要涉及到数据加密,比如用户账号密码的加密,用户敏感数据的加密,涉及到的加密算法种类繁多,作为拿来主义的开发者时间精力有限,能够清楚其中主流的加密算法和用途,就已经足够了. 主要的 ...

- 基于SSM开发自行车在线租赁管理系统源码

开发环境: Windows操作系统开发工具: Myeclipse+Jdk+Tomcat+MYSQL数据库注意:此项目分管理员与普通用户两种角色运行效果图 源码及原文链接:https://javadao ...

- npm下载文件临时目录、实际存放目录路劲

npm 下载文件临时存放目录 路劲:C:\Users\xxxxxx\AppData\Roaming\npm\node_modules ( C:\Users\dihongwanyan\AppData\R ...

- 使用ffmpeg为影片添加字幕

ffmpeg -i infile.mp4 -i infile.srt -c copy -c:s mov_text outfile.mp4 The order of -c copy -c:s mov_t ...

- 伟大的悲剧——记CSP2019

伟大的悲剧——记CSP2019 就算伟大,依然悲剧…… 现在我好恨自己 我……差一点……就是省一了…… 这一点是多少呢? 2分! 1名! 省一65人,我第66! 唉……太悲催了…… jx的分数线居然还 ...