FPGA上外挂DDR2&DDR3&MIG IP的使用记录

前言

当需要大容量数据存储及处理的时候,FPGA内部自带的存储资源是远远不够的,所以问题来了,怎么使用外带的DDR3?

首要问题在于DDR3是什么?有没有协议?当然只是需要用Xilinx MIG IP去配置使用的话,DDR3内部信号变化关系不需要太明了,当然明了会更佳,有时间可以看看底层内部架构,只是使用MIG IP去配置DDR3的话不需要像写一个DDR3控制器那么明白。

所需要预先储备的知识:

(1)阅读JEDEC DDR3 SDRAM STANDARD (标准协议)(有空的童鞋可以阅读);

(2)阅读ug586_7Series_MIS.pdf (XIlinx MIG核配置文档)(必须的);

(3)百度文库中的高富帅教程,百度一下就可以知道(推荐阅读);

Xiinx MIG IP为开发者提供了用户接口,极大的降低了开发者控制DDR3的难度,提升开发效率(然并卵)。

///////////////////////

1.看完上述文章后,你就想着怎么在vivado中生成MIG IP呢?

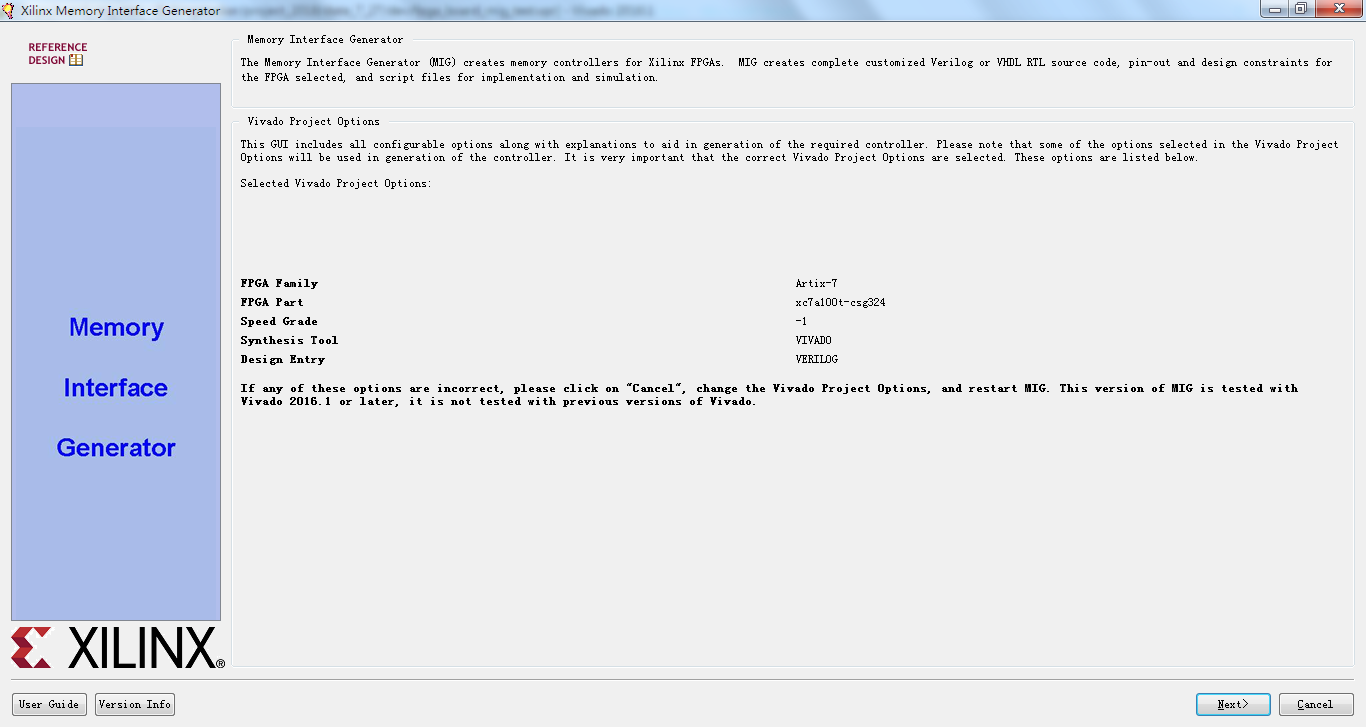

本次配置以NEXYS4开发板作为配置平台;Xilinx vivado 2016.1

NEXY4开发板上自带的DDR为DDR2 型号为MT47H64M16HR-25;

配置DDR3和DDR2基本上是类似的;

(1)打开IP配置界面,搜索MIG:

(2)配置,next:

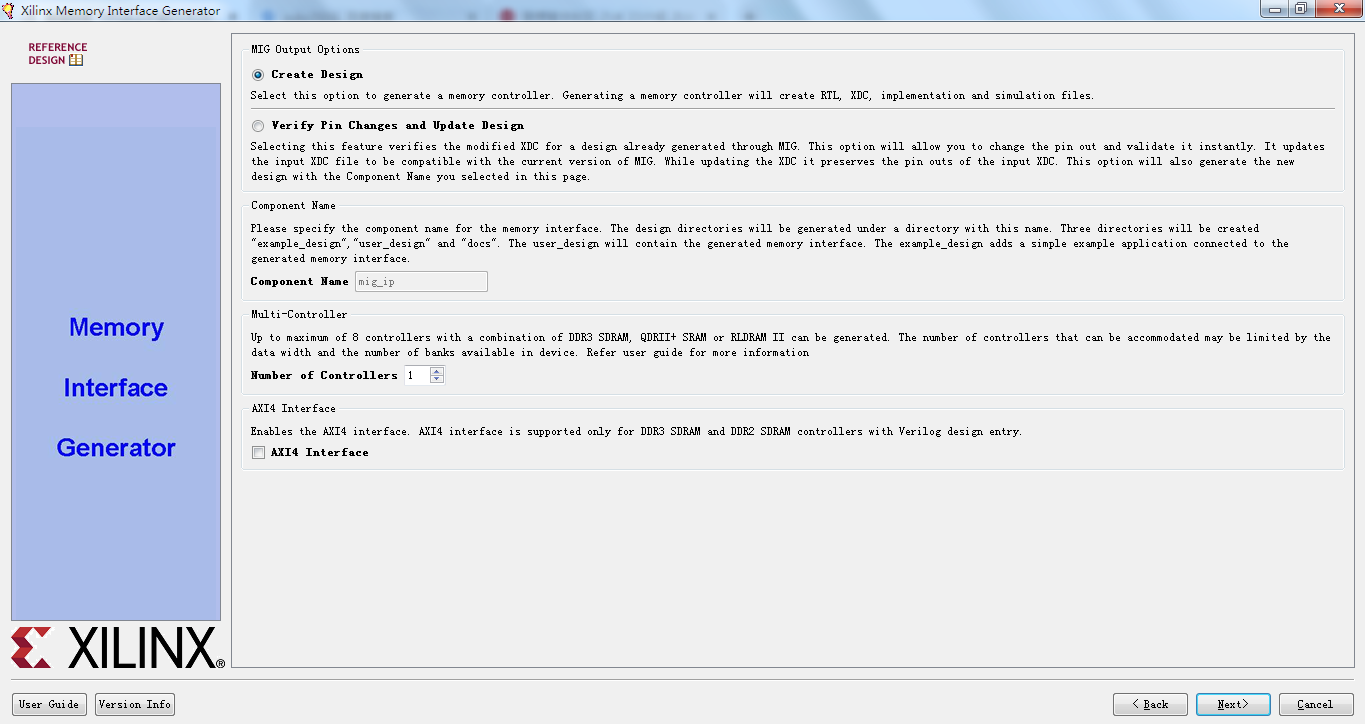

(3)当然是创建新设计,例化IP的名字修改,由于已经生成好的,所以显示为灰色。

然后选择一个控制器。。。next:

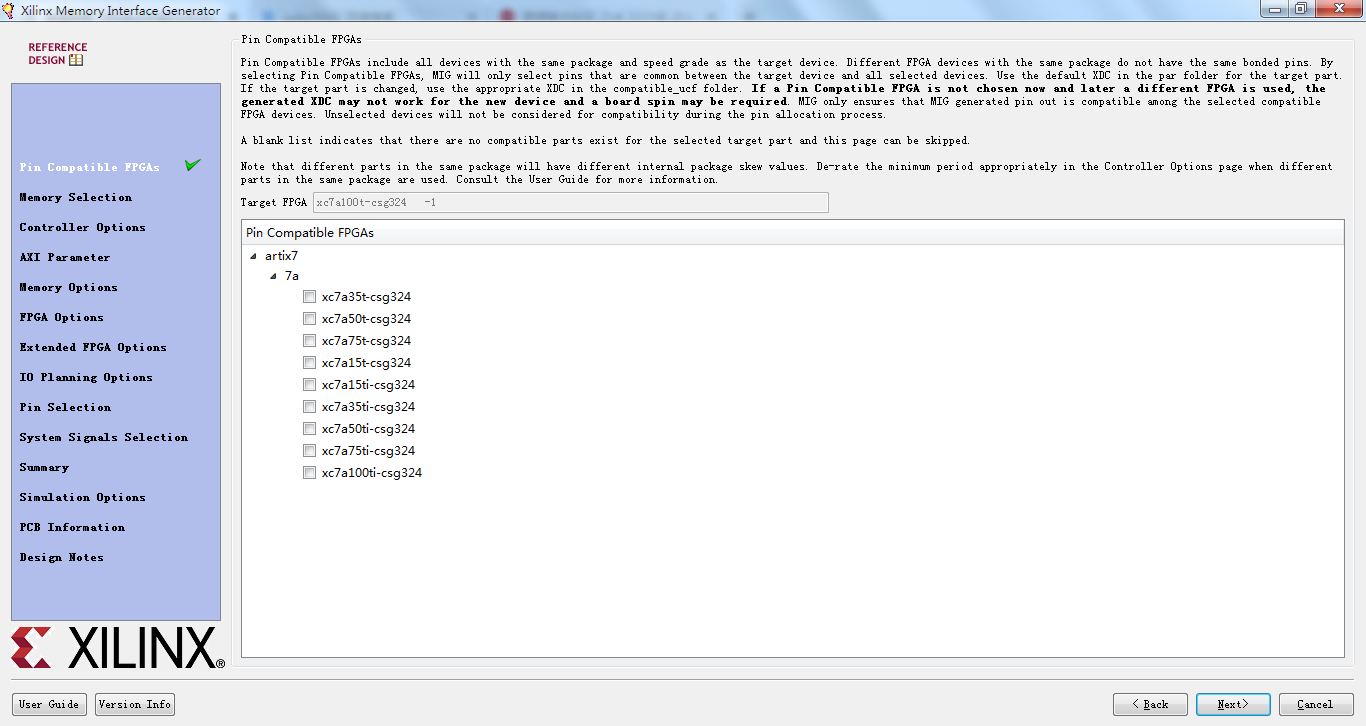

(4)器件引脚适配性选择,目前不需要,next:

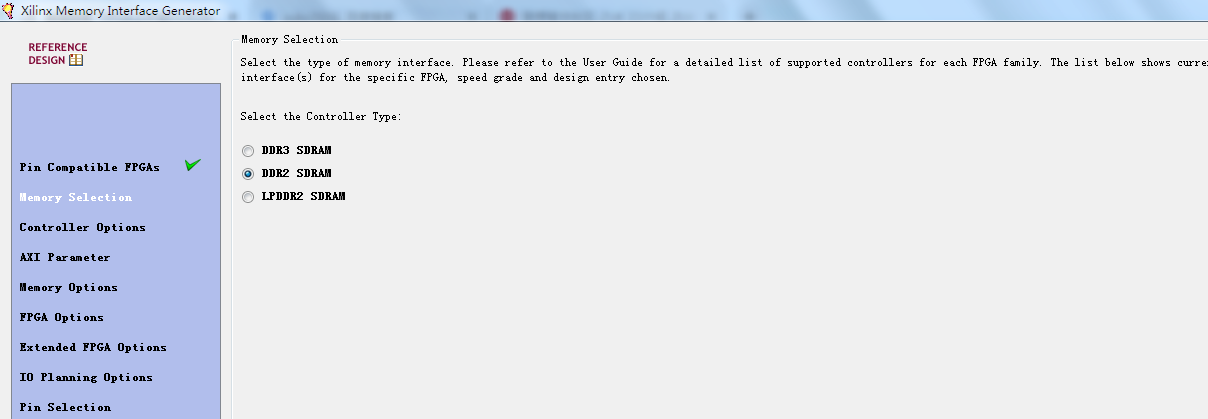

(5)选择DDR2类型,next:

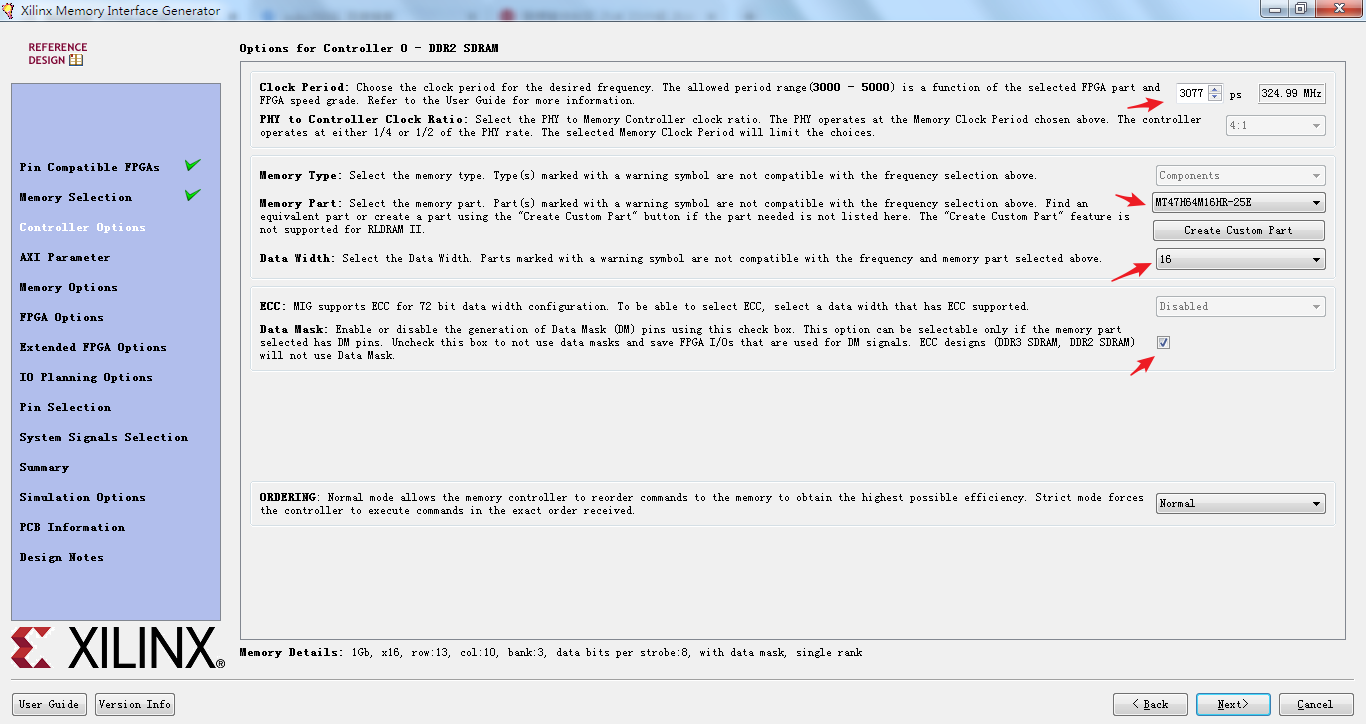

(6)clock period表示的是MIG IP的工作时钟,而DDR是双倍率,则对外接口部分的接口速率为X2,不同的器件可选择的范围是不一致的,如果选择为400M,那么接口速率为800M。

PHY to controller clock ratio:工作时钟和用户接口部分的时钟比,本质体现为ui_clk时钟。可能2:1是不可选的,下图中的4:1就表示clock period :ui_clk = 4:1;

然后选择数据位宽,本次选择为16bit则每次打出的数据为16bit,突发8的话,则rd和wr的data宽度为16*8=128bit。

本DDR2有数据掩模,选上,虽然目前没用到,next:

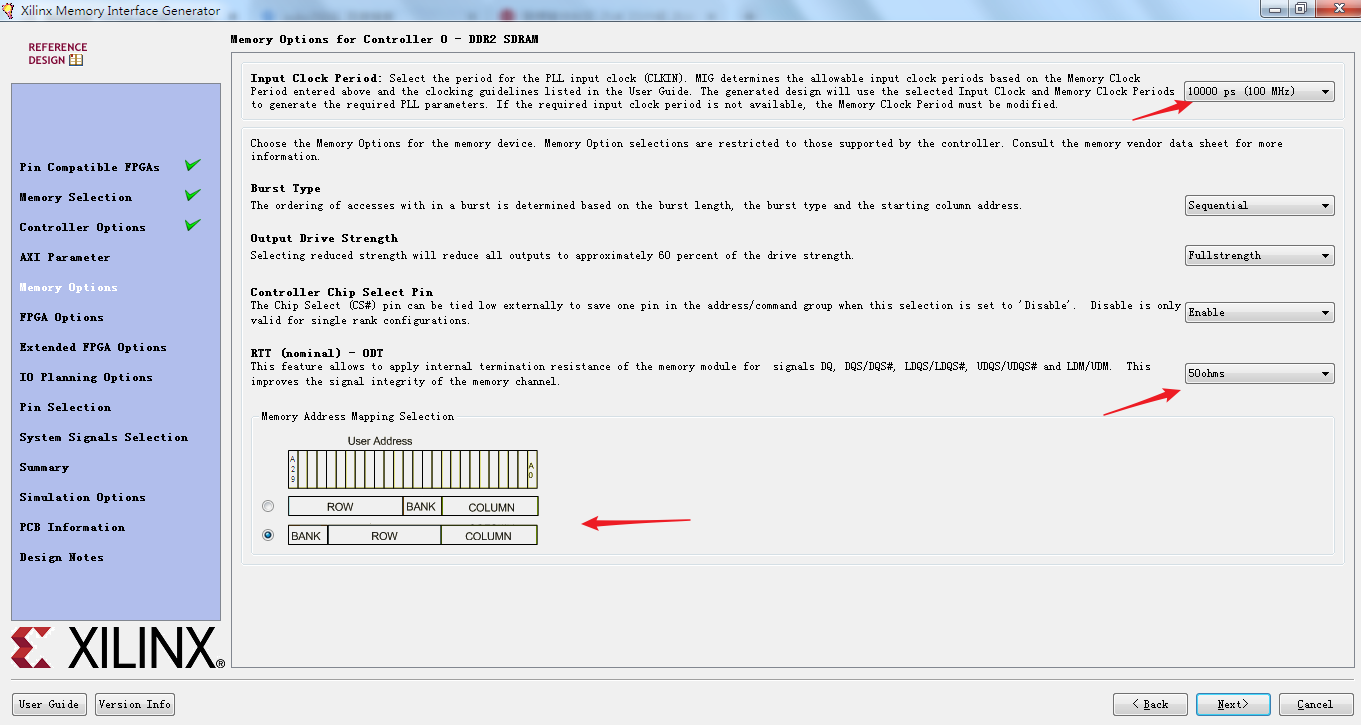

(7)选择input clock period,这是什么意思呢,如果简单起见,选择为200M,后面会有惊喜,推荐200M。你可以使用晶振的时钟或者内部时钟,后面得相关配置才能用。

选择ODT,板子文档说是50ohms,则选择此项。然后是地址映射,选择bank+row+column的方式,next:

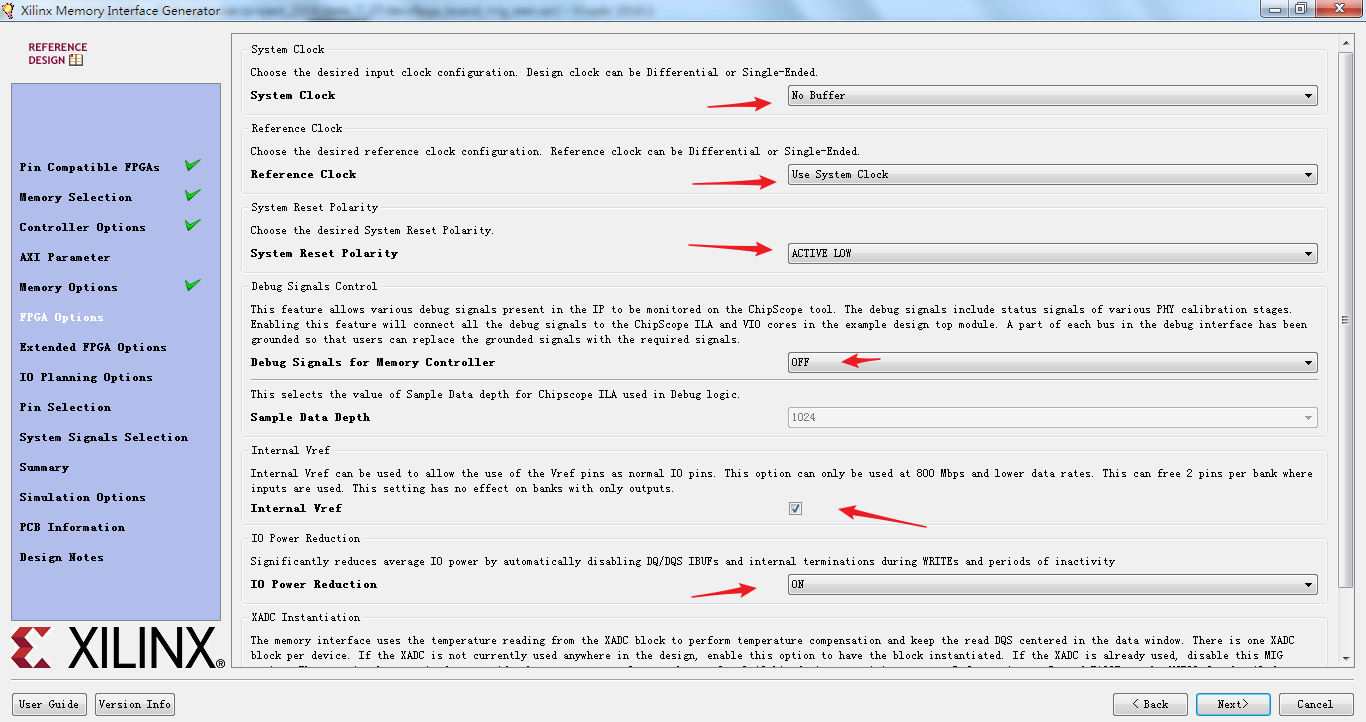

(8)系统时钟与参考时钟的极性选择,如果想用内部的时钟作为系统时钟和参考时钟,那么就选择no buffer选项,如果前面选择了200M系统时钟输入,那么参考时钟会多一个use system clock 的选项,也就是少给一个时钟,不然前面选择的不是200M时钟的话,参考时钟就会贴心的问你要200M时钟。想用PLL的输出作为system clk输入,那么选择no buffer项。参考时钟用use system clock。毕竟对于只有一个外部晶振的话,单独给mig ip就完犊子了,别的时钟不能再使用这个晶振时钟,为了多几个时钟使用,还是用PLL。况且有的板子晶振只有20M的话,你就没得选了,必须用PLL倍频灌入时钟。

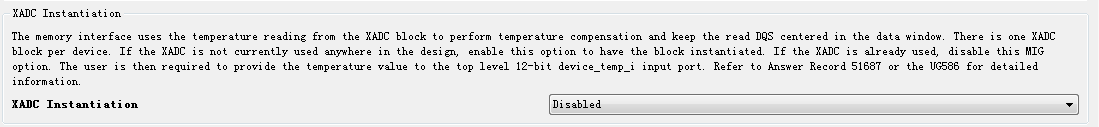

debug信号不使用,内部参考引脚做普通输入脚使用,xdc啥的关掉。

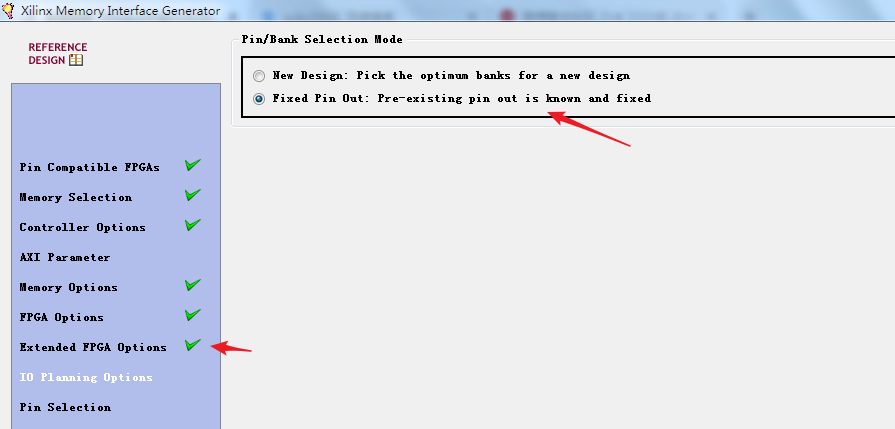

(9)如果有DDR2的引脚分配的,就选择Fixed Pin Out,开发板之类的一般带,自己画的板子就得照着原理图一个个分了,可能会瞎眼。

(10)选择你的引脚约束文件,导入并检查合理性,通过则next:

然后一路next,就可以生成MIG IP了。

/////////////////////////

2.怎么用IP自带的仿真呢?

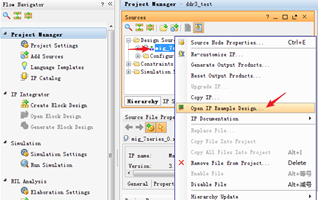

(1)现在我们就有了如下图所示的IP文件架构,右键IP选择打开IP example design,为了仿真使用。

在你的example设计中会有仿真顶层,在哪呢,我的在这,下面是ddr3举例:

E:\kingstacker\project_2018\date_7_23\dev\mig_7series_0_example\mig_7series_0_example.srcs\sim_1\imports\sim

这个目录下有什么文件呢:

ddr3_model.sv:DDR3的总线功能模型,相当于个ddr3芯片。

ddr3_model_parameters.vh:一堆模型的相关参数。

sim.do:modalism可用的do文件,不过不能直接使用得修改。

sim_tb_top.v:仿真顶层文件。

wiredly.v:仿真需要用的文件。

其他就没啥卵用了。

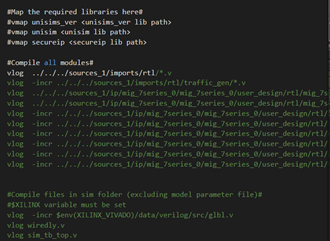

打开sim.do文件应该是下面这个样子,这放到modelsim仿真绝对是会出错的,所以需要修改相关路径。

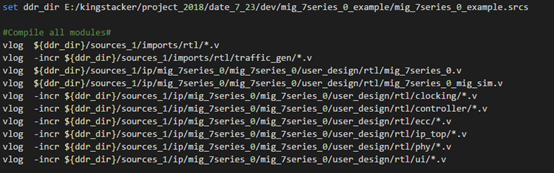

设置一下相关v文件的绝对路径:

修正glbl.v文件的路径,我这里用ISE的glbl文件也没问题。然后修正wiredly.v、sim_tb_top.v、ddr3_model.sv路径。

修改仿真精度fs为ps,加快仿真速度。修改相关库挂载,根据编译的名字修改。

然后就可以切换到sim.do文件所在的路径,do sim.do即可。

3.怎么自己用激励进行仿真呢?

FPGA上外挂DDR2&DDR3&MIG IP的使用记录的更多相关文章

- MIG IP控制DDR3读写测试

本文设计思想采用明德扬至简设计法.在高速信号处理场合下,很短时间内就要缓存大量的数据,这时片内存储资源已经远远不够了.DDR SDRAM因其极高的性价比几乎是每一款中高档FPGA开发板的首选外部存储芯 ...

- Xilinx 7系列例化MIG IP core DDR3读写

昨晚找了一下,发现DDR3读写在工程上多是通过例化MIG,调用生成IPcore的HDL Functional Model.我说嘛,自己哪能写出那么繁琐的,不过DDR读写数据可以用到状态机,后期再添砖加 ...

- 基于MIG IP核的DDR3控制器(一)

最近学习了DDR3控制器的使用,也用着DDR完成了一些简单工作,想着以后一段可能只用封装过后的IP核,可能会忘记DDR3控制器的一些内容,想着把这个DDR控制器的编写过程记录下来,便于我自己以后查看吧 ...

- 基于MIG IP核的DDR3控制器(二)

上一节中,记录到了ddr控制器的整体架构,在本节中,准备把ddr控制器的各个模块完善一下. 可以看到上一节中介绍了DDR控制器的整体架构,因为这几周事情多,又要课设什么的麻烦,今天抽点时间把这个记录完 ...

- 如何区分DDR1 DDR2 DDR3内存条

DDR1,DDR2,DDR3内存条(DDR是Double Data Rate双倍速率同步动态随机存储器的英文缩写)就是俗称的一二三代内存条.这三种内存条工艺不同,接口不同,性能不同,互不兼容.要区分它 ...

- PCIE_DMA实例四:xapp1052在Xilinx 7系列(KC705/VC709)FPGA上的移植

PCIE_DMA实例四:xapp1052在Xilinx 7系列(KC705/VC709)FPGA上的移植 一:前言 这段时间有个朋友加微信请求帮忙调试一块PCIe采集卡.该采集卡使用xilinx xc ...

- 【小梅哥FPGA进阶教程】MC8051软核在FPGA上的使用

十.MC8051软核在FPGA上的使用 本教程内容力求以详细的步骤和讲解让读者以最快的方式学会 MC8051 IP core 的应用以及相关设计软件的使用,并激起读者对 SOPC 技术的兴趣.本实验重 ...

- 基于dsp_builder的算法在FPGA上的实现

基于dsp_builder的算法在FPGA上的实现 一.摘要 结合dsp_builder.matlab.modelsim和quartus ii等软件完成算法的FPGA实现. 二.实验平台 硬件平台 ...

- 在Linux系统上限制远程登录的IP

在Linux系统上限制远程登录的IP,使用系统自带的配置文件. /etc/hosts.allow /etc/hosts.deny 匹配原则 先allow 后deny.

随机推荐

- 起步 - 安装 Git

安装 Git 是时候动手尝试下 Git 了,不过得先安装好它.有许多种安装方式,主要分为两种,一种是通过编译源代码来安装:另一种是使用为特定平台预编译好的安装包. 从源代码安装 若是条件允许,从源代码 ...

- window.open()详解及浏览器兼容性问题示例探讨

这篇文章主要介绍了window.open()的使用及浏览器兼容性问题方面的知识,感兴趣的朋友可以参考下 一.基本语法: window.open(pageURL,name,parameters) 其 ...

- linux禁止特定ip访问某个端口

linux禁止特定ip访问某个端口 解决方法: 禁止特定ip访问8501端口的命令0:iptables -I INPUT -s 192.168.0.232 -ptcp --dport 8501 - ...

- (十)java虚拟机性能监控工具

一. jps(Java Virtual Machine Process Status Tool) jps主要用来输出JVM中运行的进程状态信息.语法格式如下: 命令行参数选项说明如下: 1.1 案例 ...

- Eclipse导入Spring Boot项目后pom.xml出现红叉的解决办法

胸怀难的问题是:程序能正常运行,但是pom.xml下面有一个红叉. 解决办法: 右键项目 --> Update project...

- HttpRequest Get和Post调用其他页面的方法

HttpRequest Get和Post调用其他页面的方法,需要的朋友可以参考一下 //Get请求方式 private string RequestGet(string Url) { ...

- list自定义排序工具类

工具类 package sort; import java.lang.reflect.Method; import java.text.Collator; import java.util.Compa ...

- 白嫖百度 Tesla V100 笔记(在 AI Studio 上使用 tensorflow 和 pytorch 的方法)

登陆百度 AI Studio 并按照教程创建新项目 启动项目并进入控制台 下载 Anaconda3/Miniconda3 安装脚本 安装在 ~/work/*conda3 目录 输入命令 source ...

- vue中的.passive修饰符

一.passive作用 详情请参考MDN(https://developer.mozilla.org/zh-CN/docs/Web/API/EventTarget/addEventListener)中 ...

- C#中使用HttpClient来Post数据的内容HttpContent的各种格式

平时使用各种网络传输的时候基本上是以Json格式进行的, 所以对其他几种格式也是一知半解, 今天静下心对其好好梳理一番. 首先我借鉴了一篇文章(https://segmentfault.com/a/1 ...