DE1-GHRD

新建工程socs_system

进入菜单选择Tools---Qsys

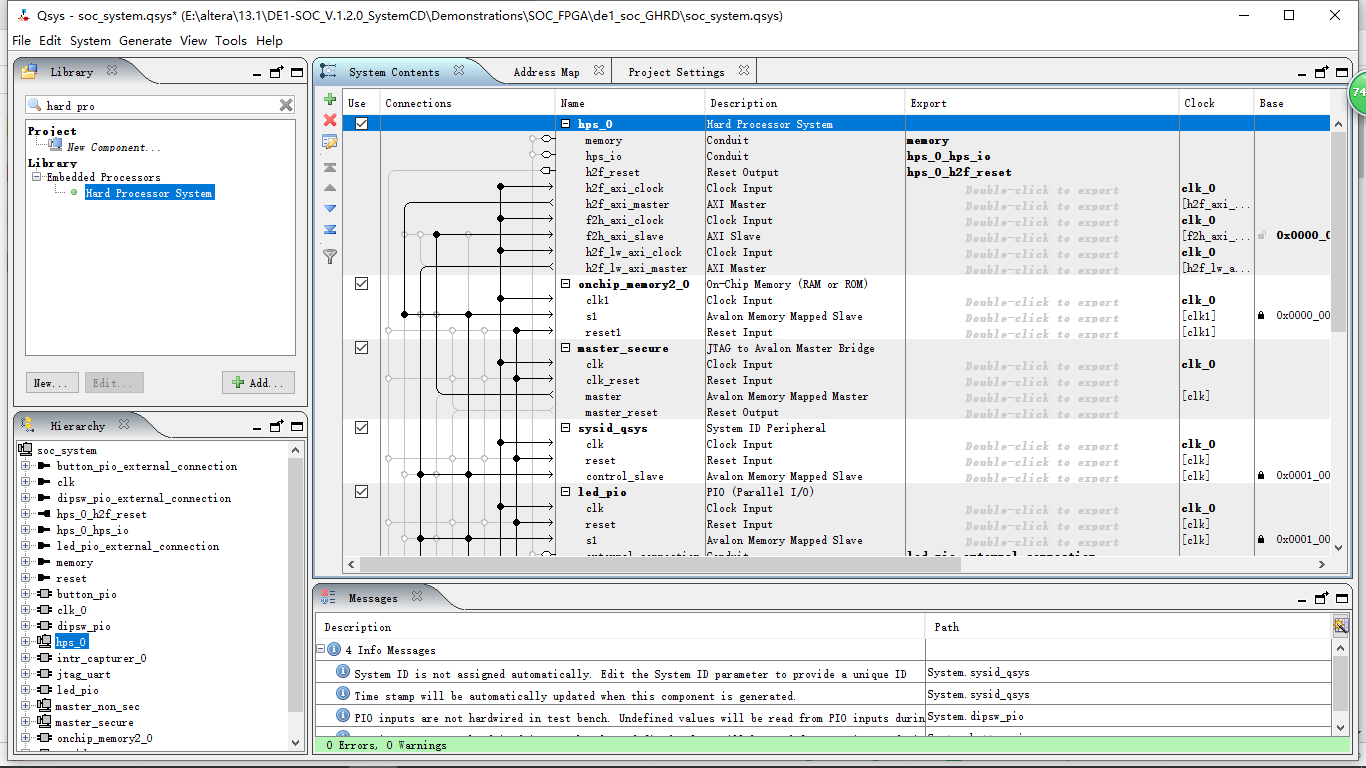

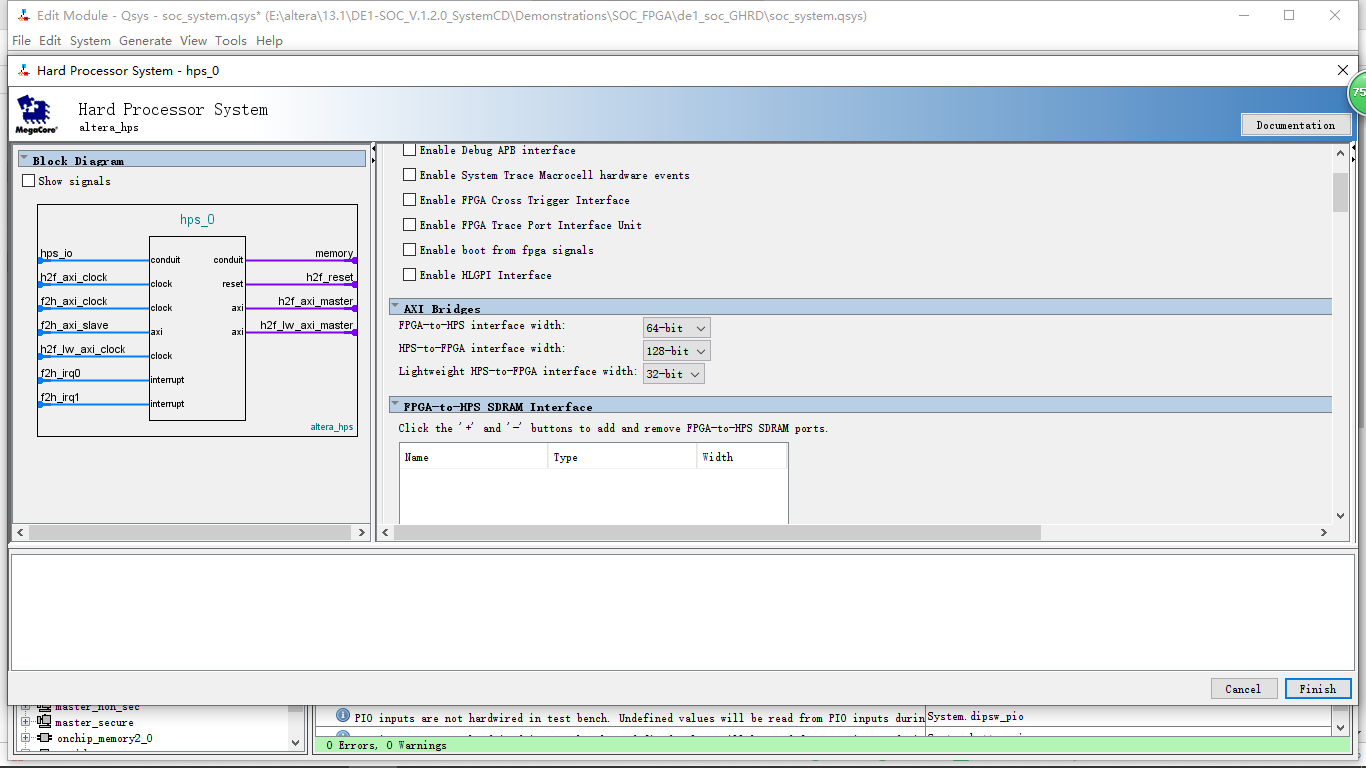

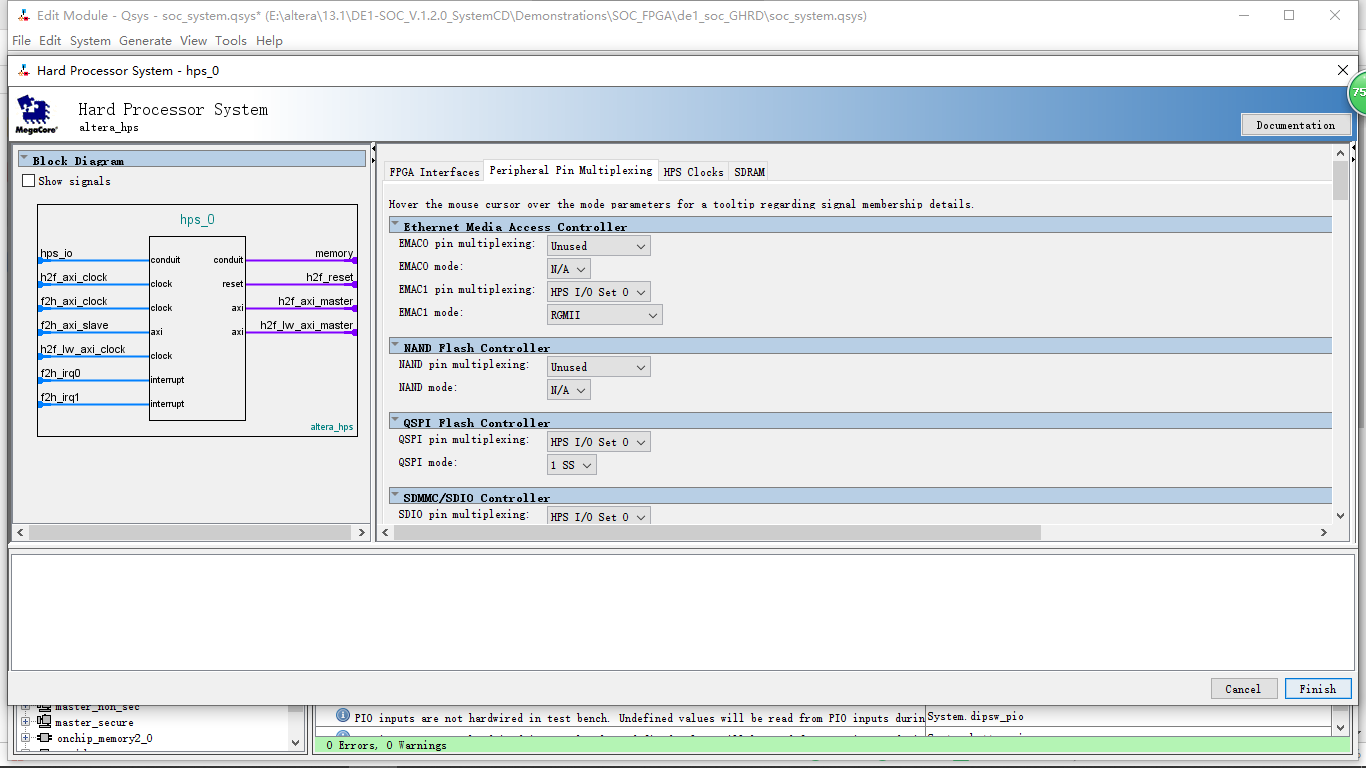

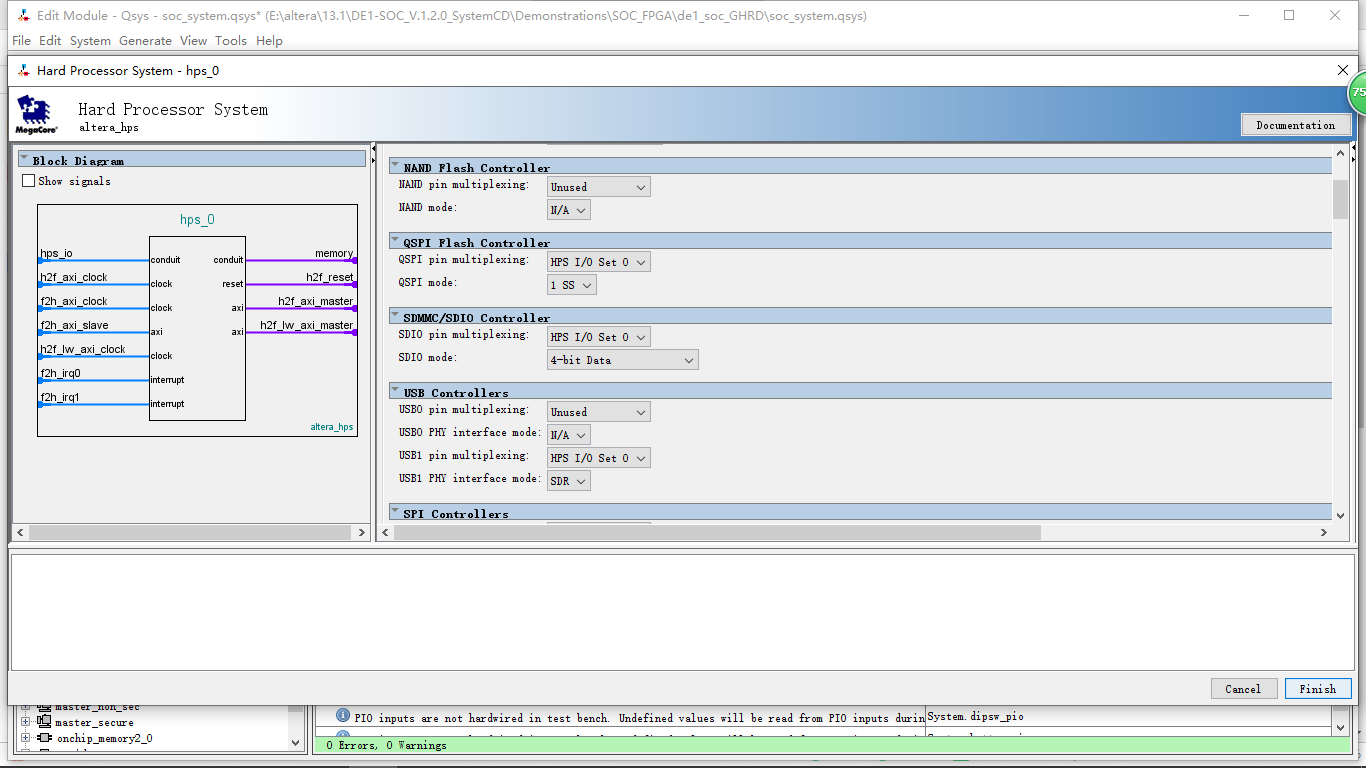

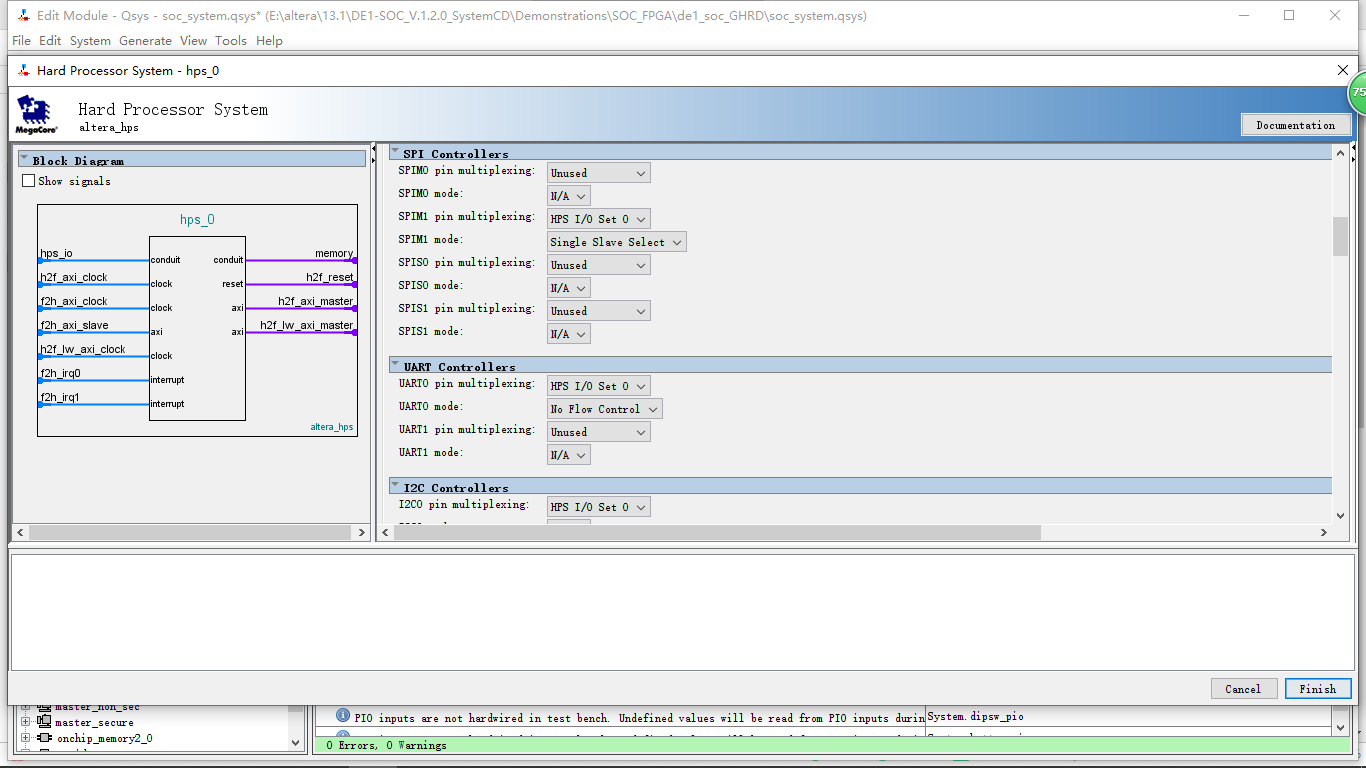

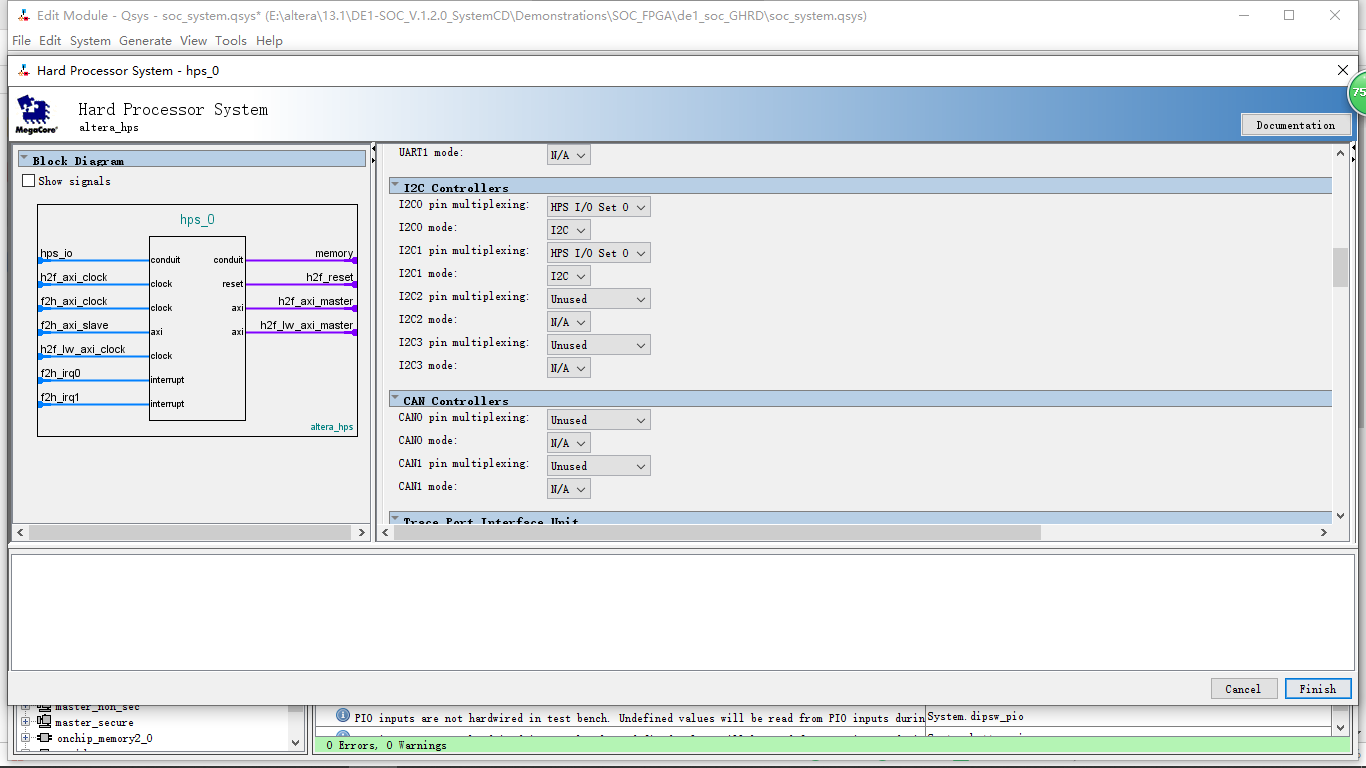

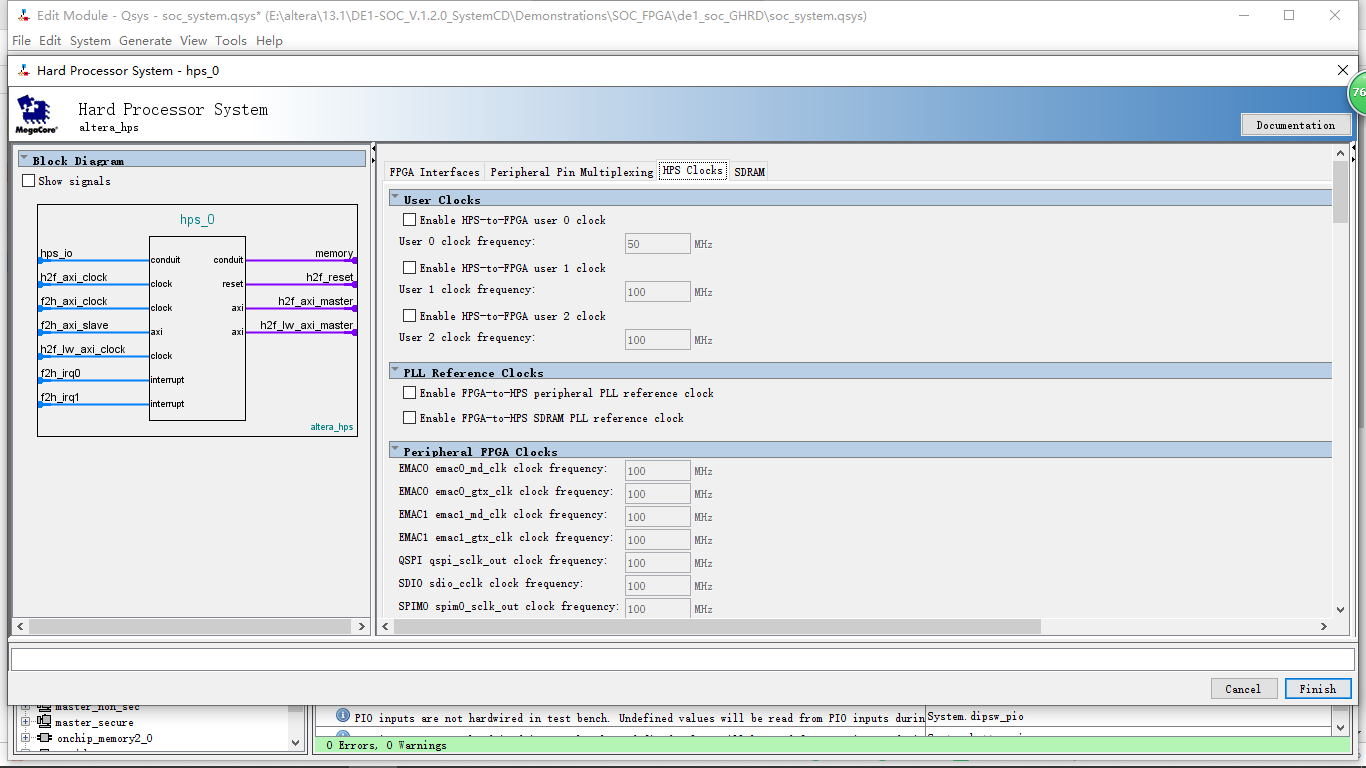

配置hps系统

首先选择

在更改参数

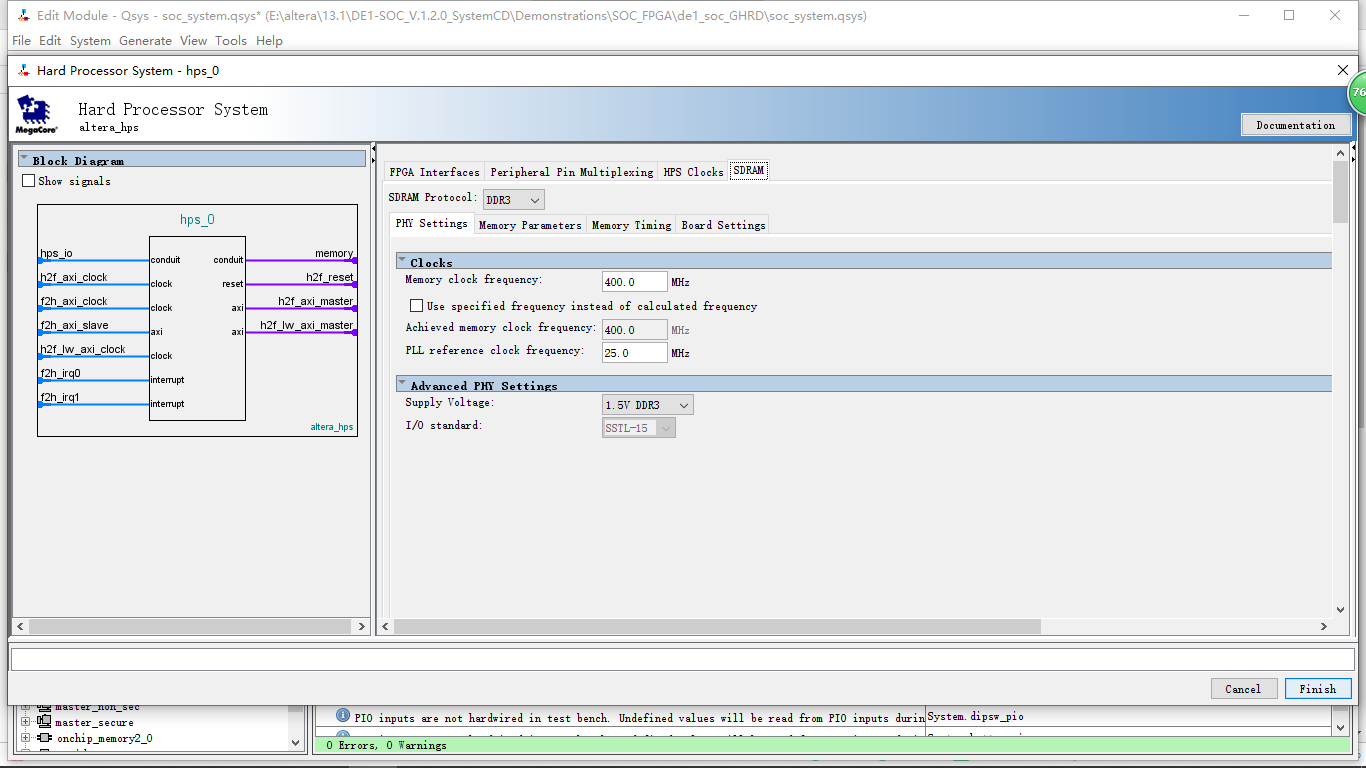

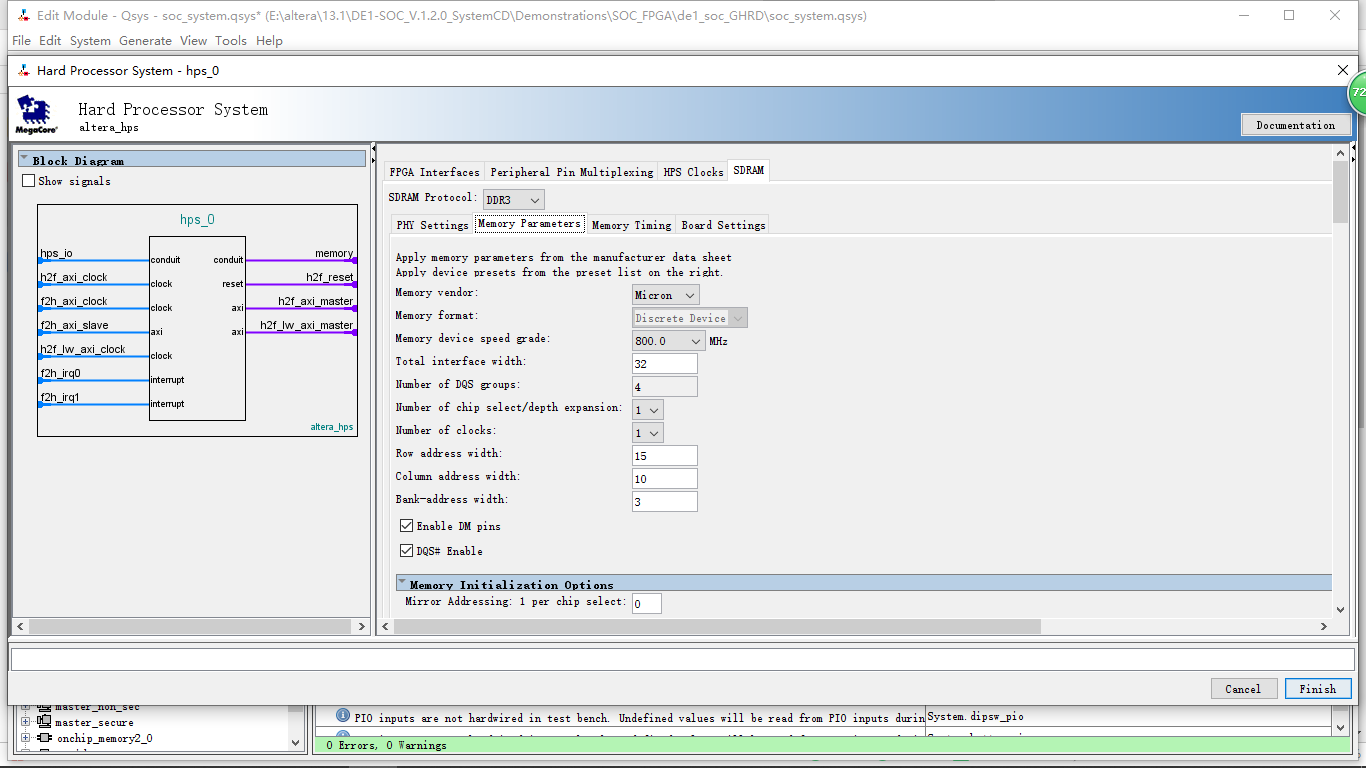

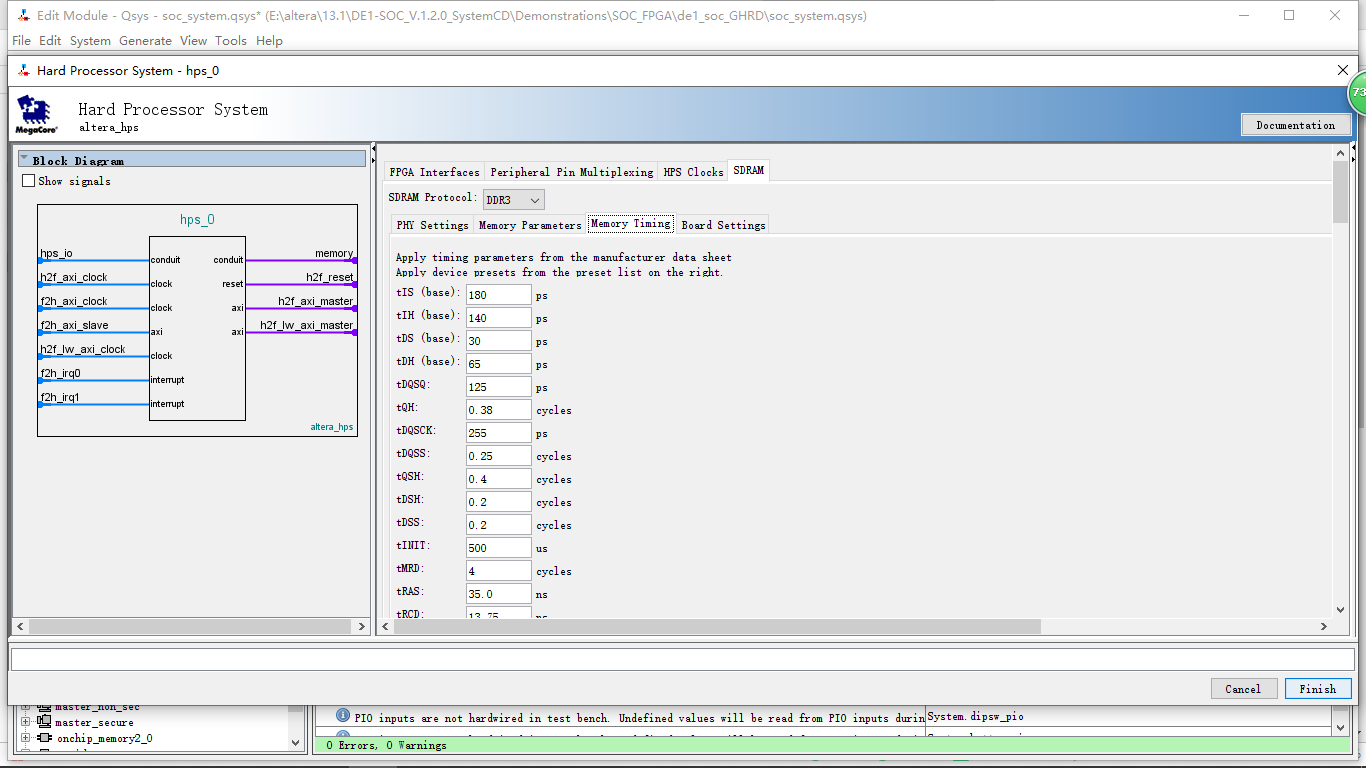

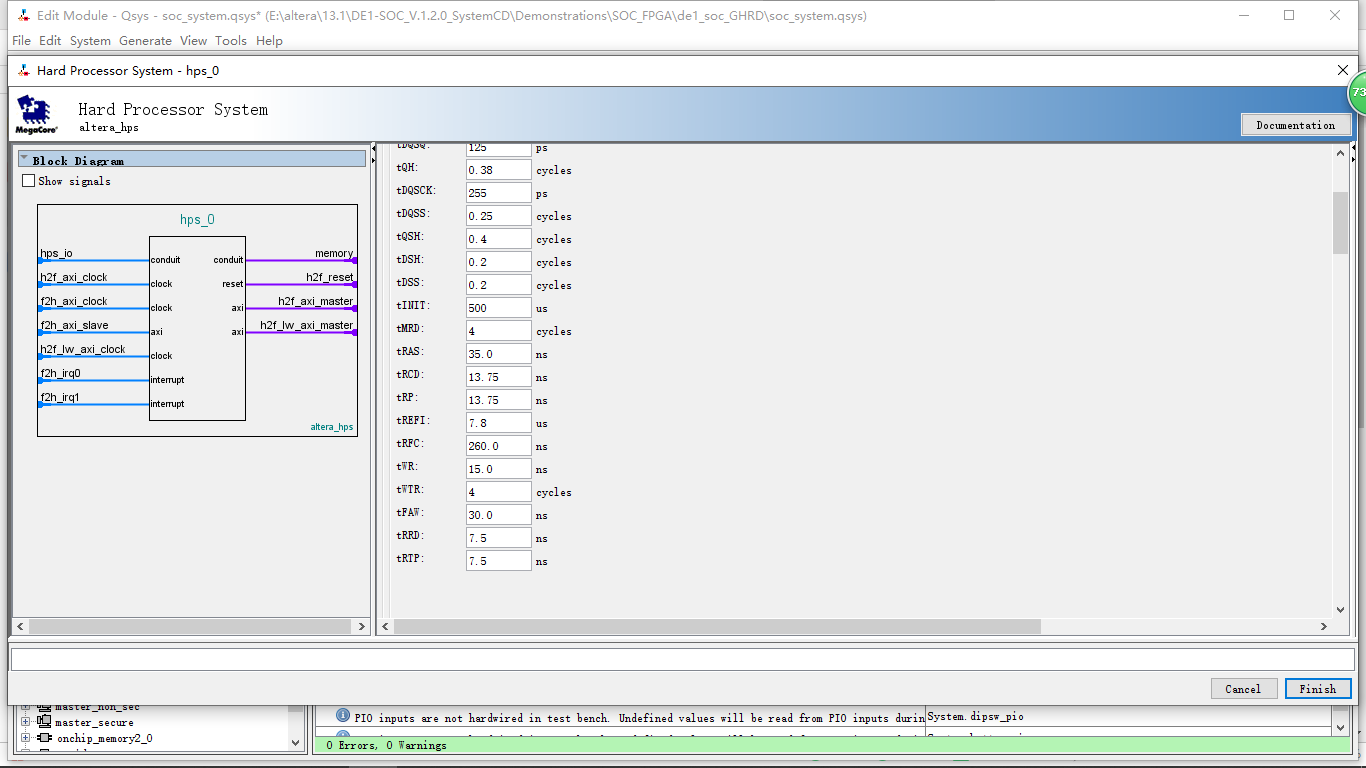

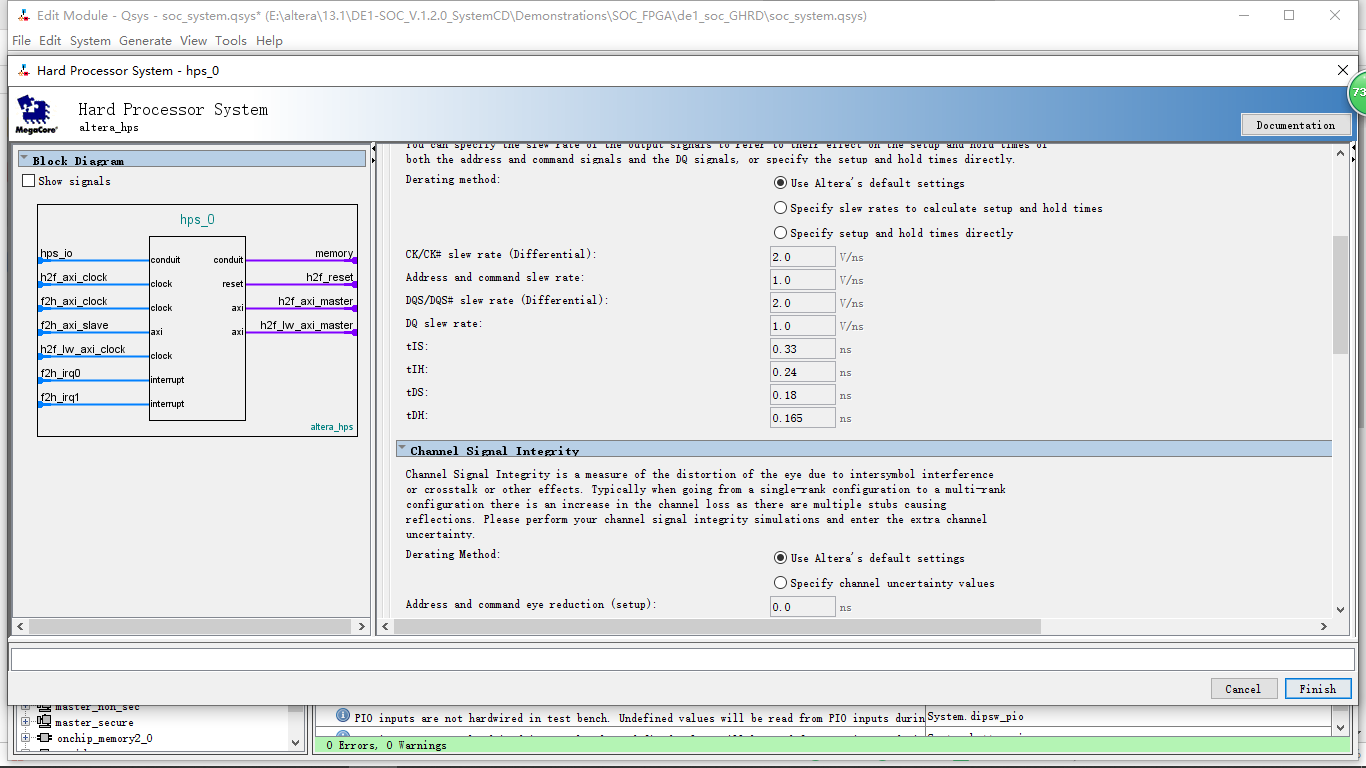

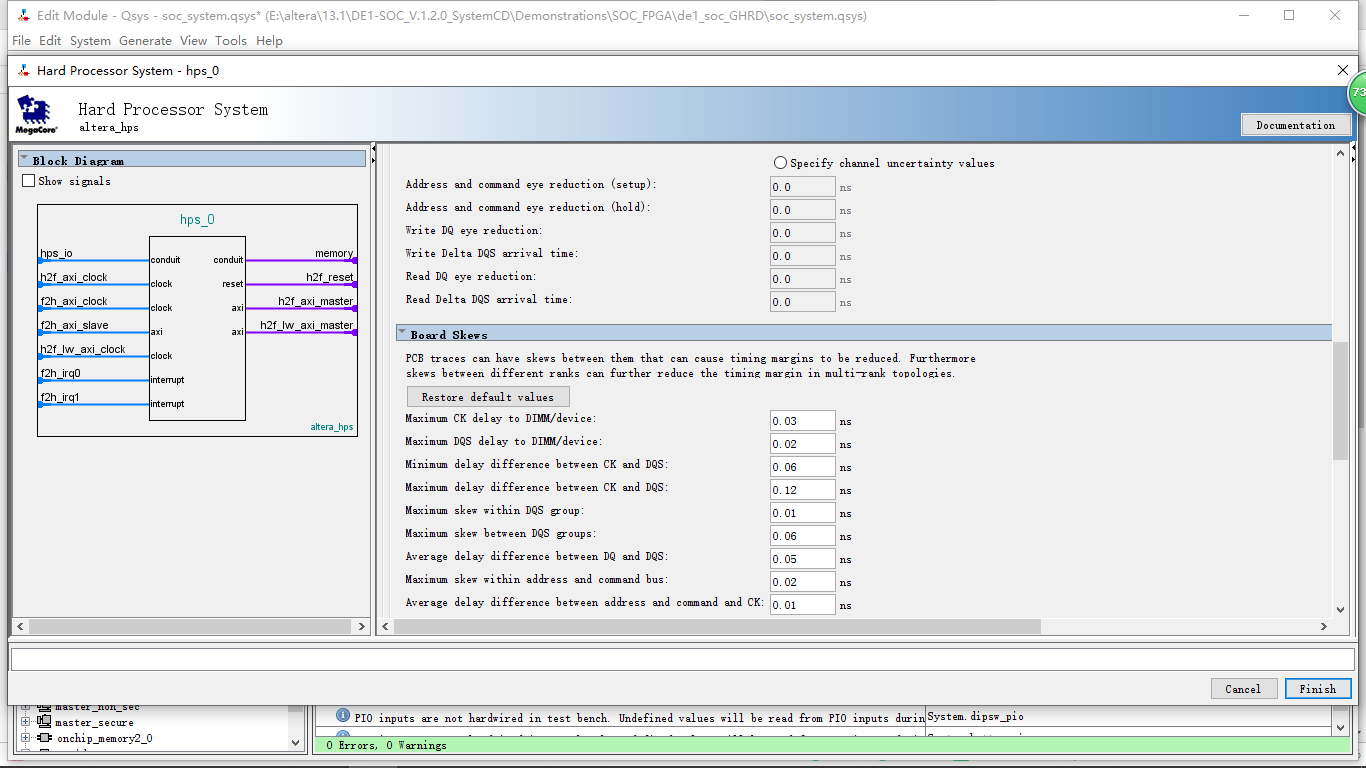

配置hps的sdram各项参数

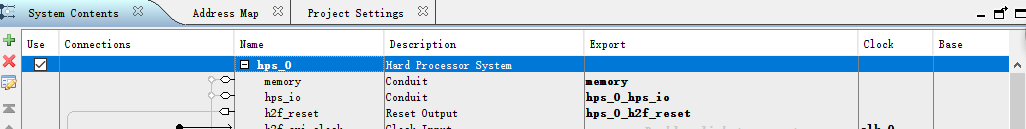

将名字改为hps_0

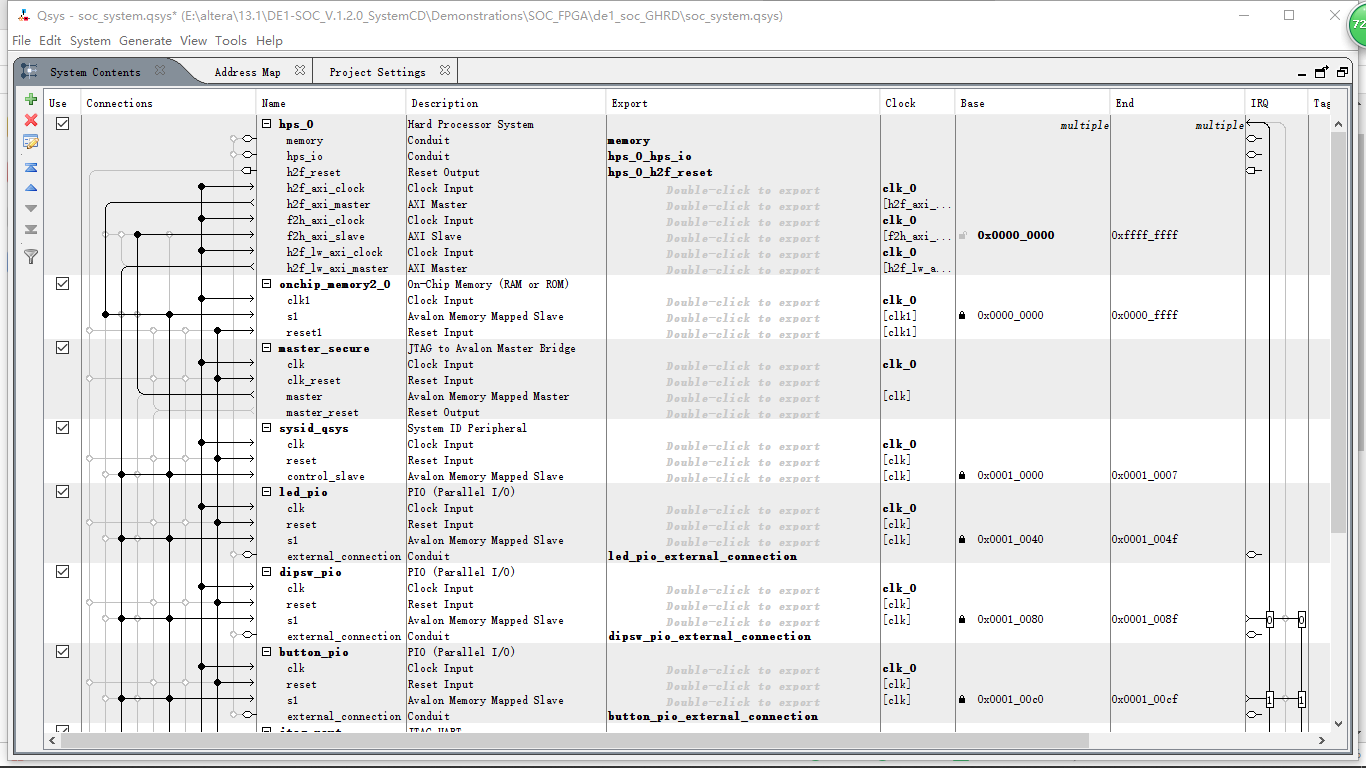

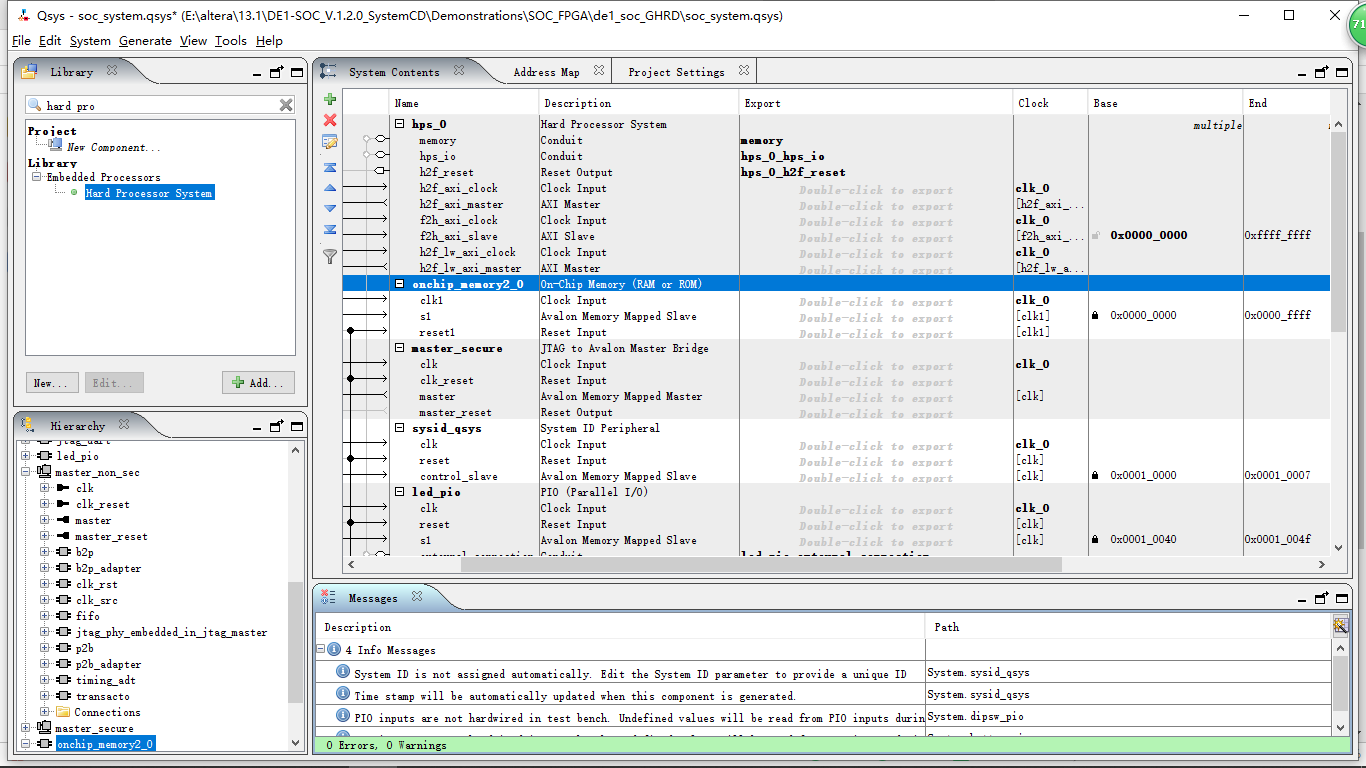

这样hps配置完成;在配置存储器和其他外设

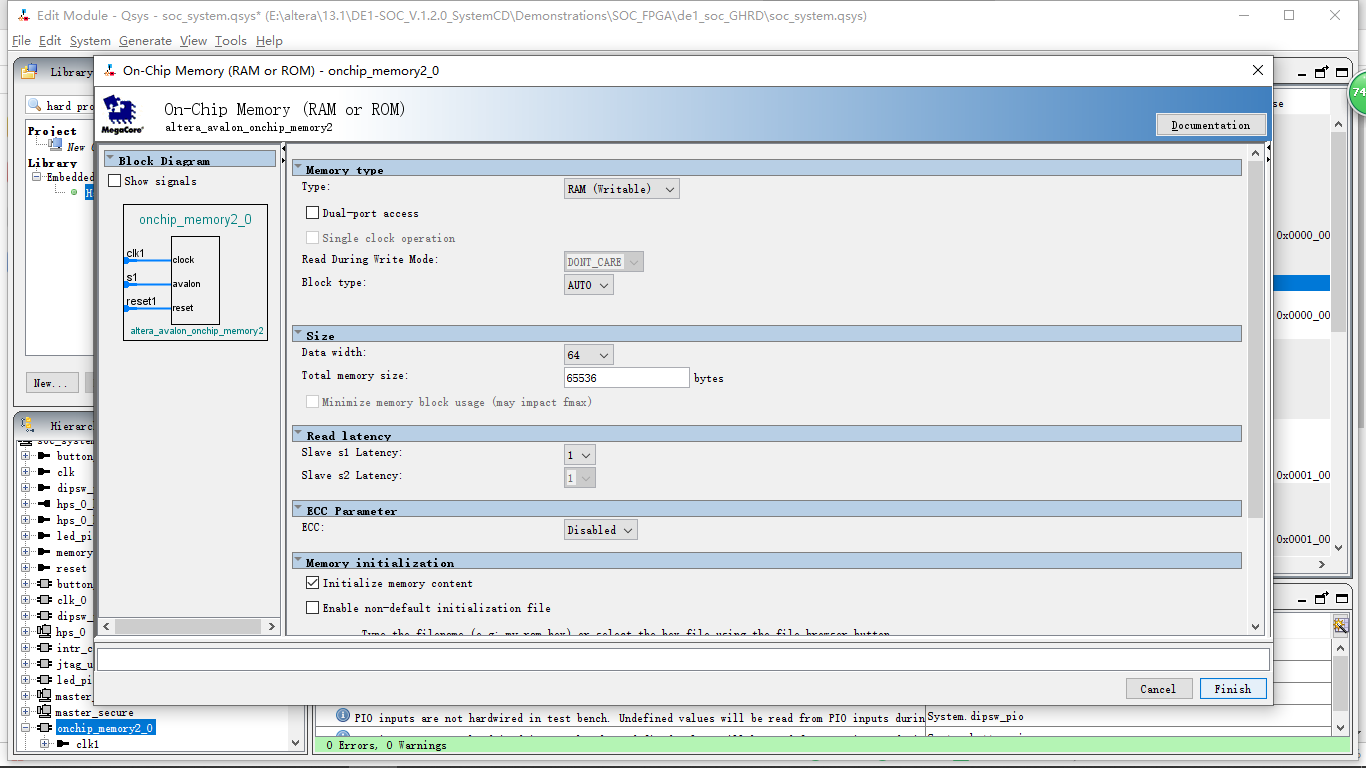

on-chip-memory

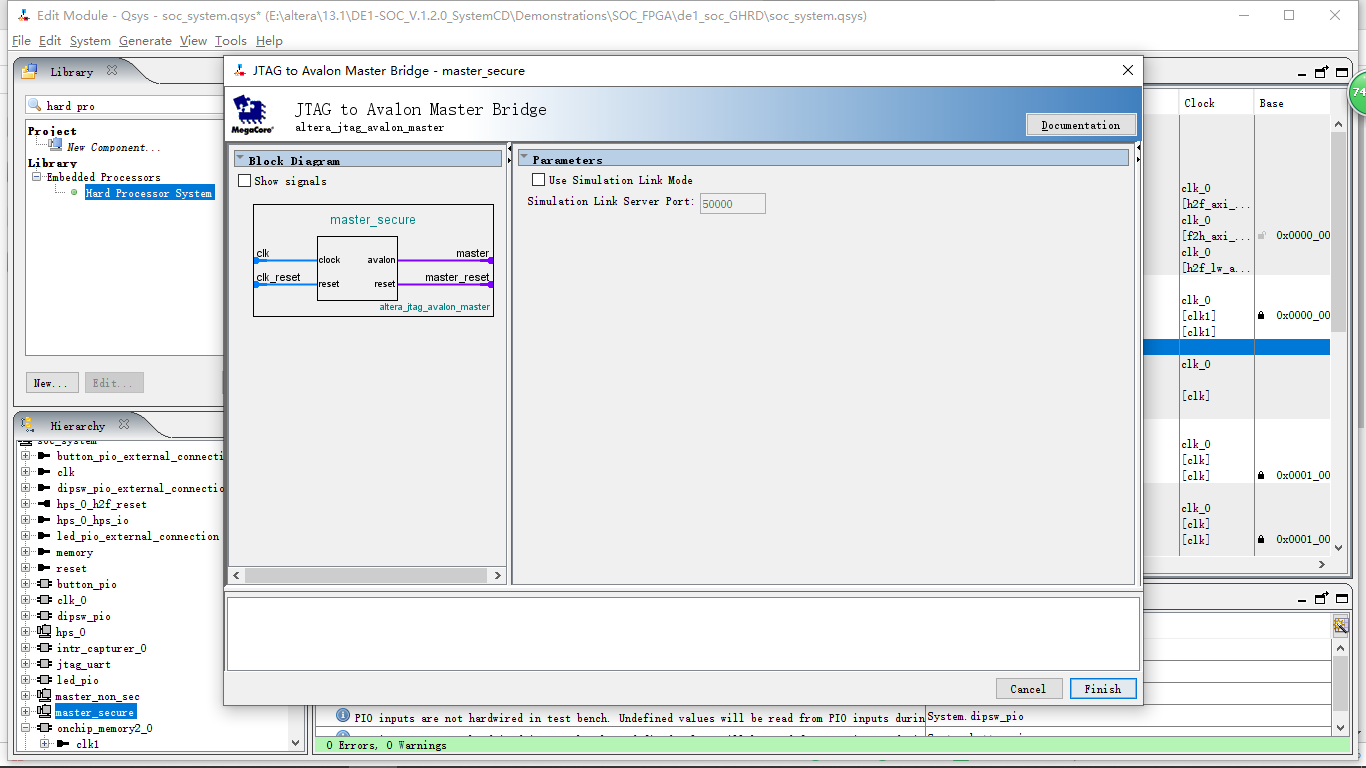

JTAG to avaion bridge(改名为mster_secure)

system ID(名字为syssid_qsys)

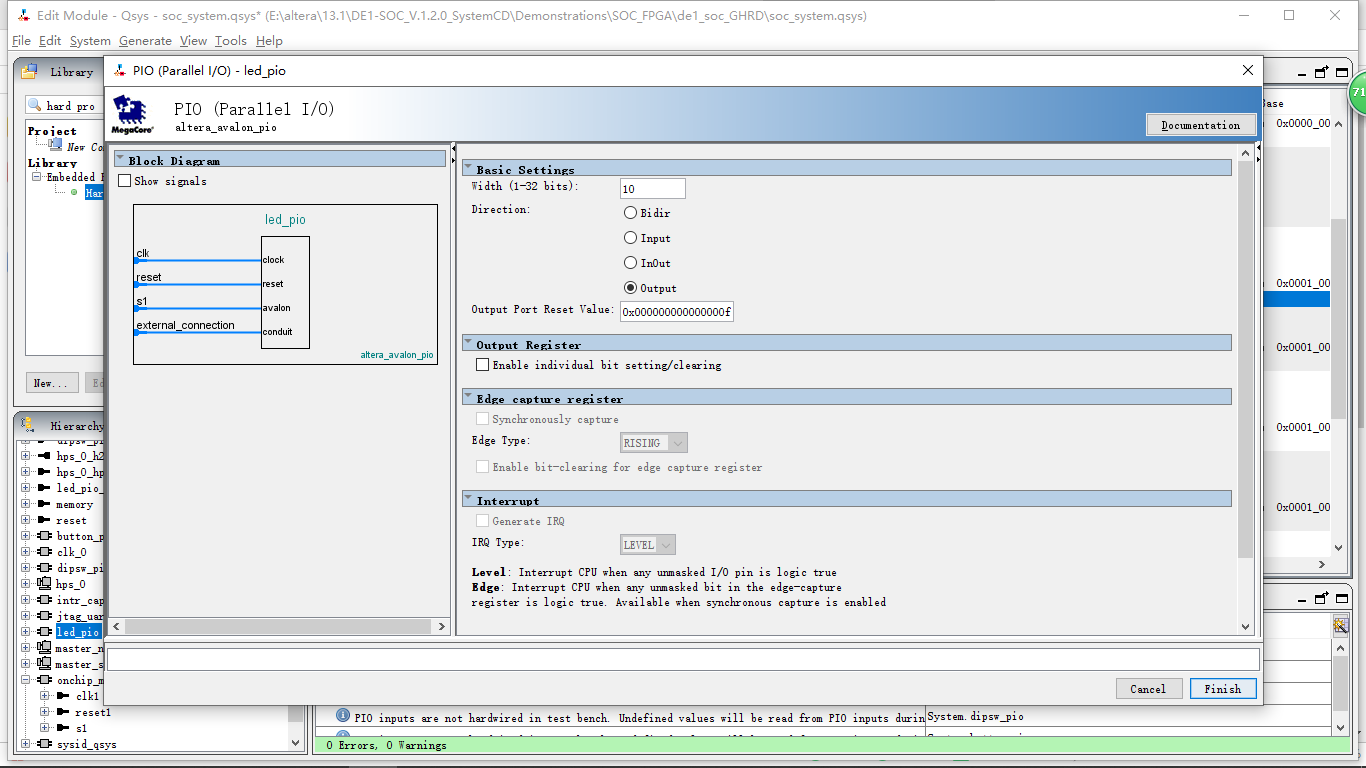

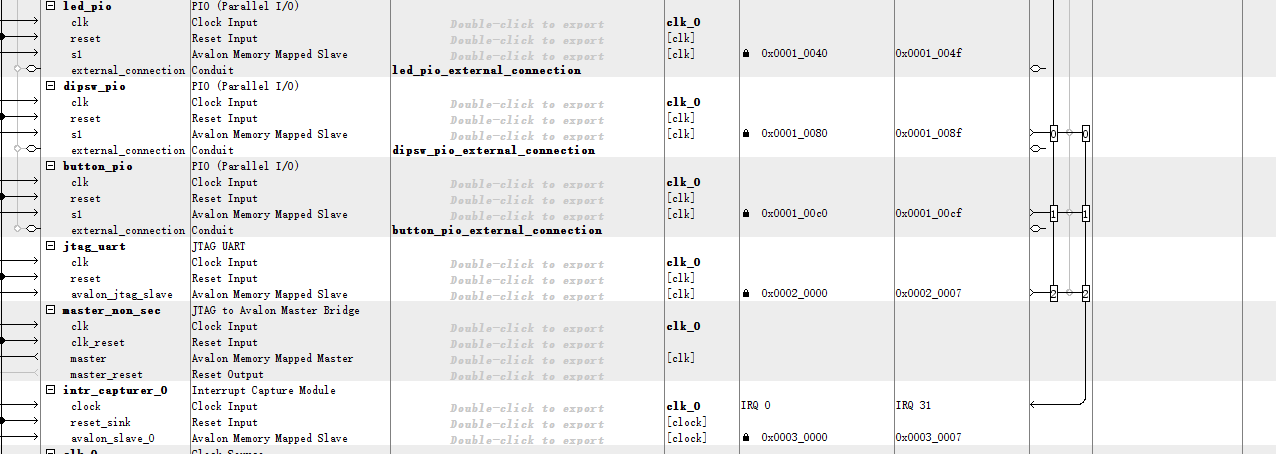

led_pio

dipsw_pio

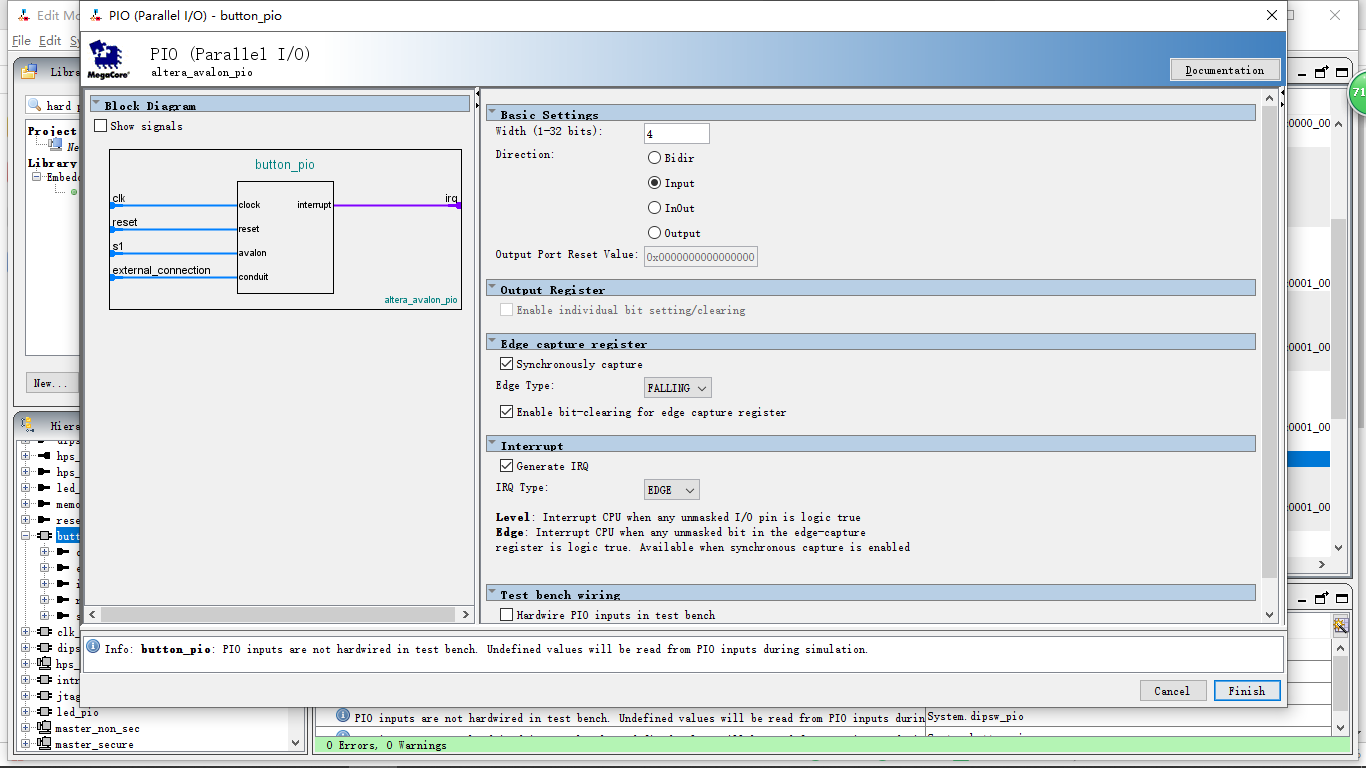

button_pio

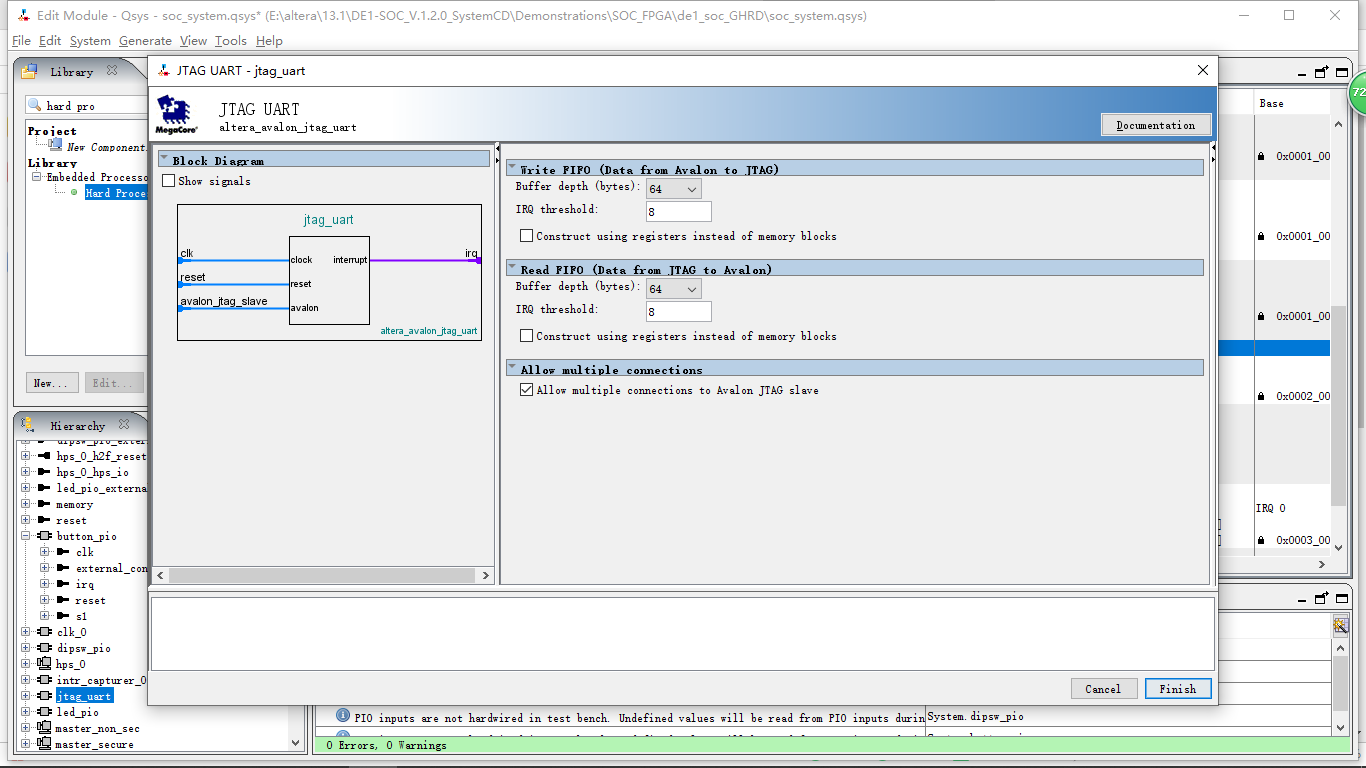

JTAG_UART

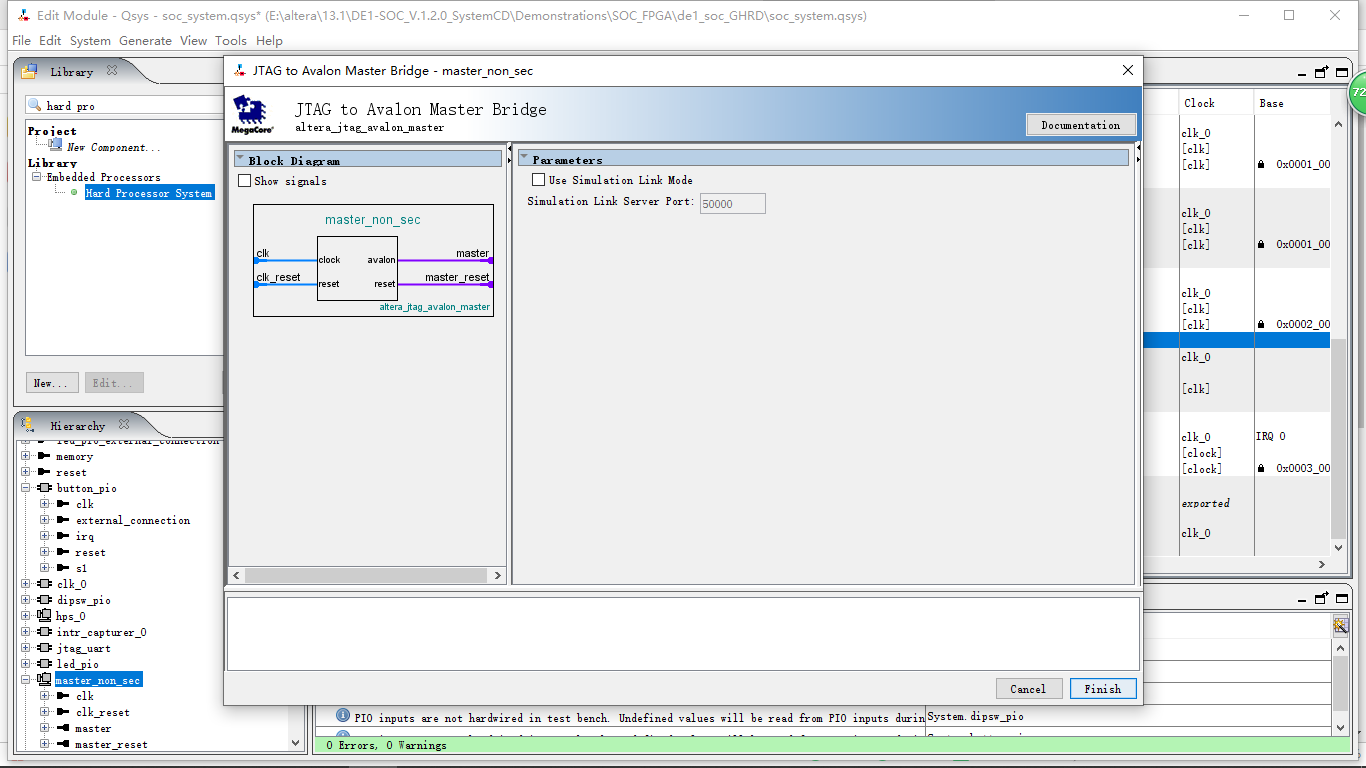

JTAG to Avation master bridhe(改名为master_non_sec)

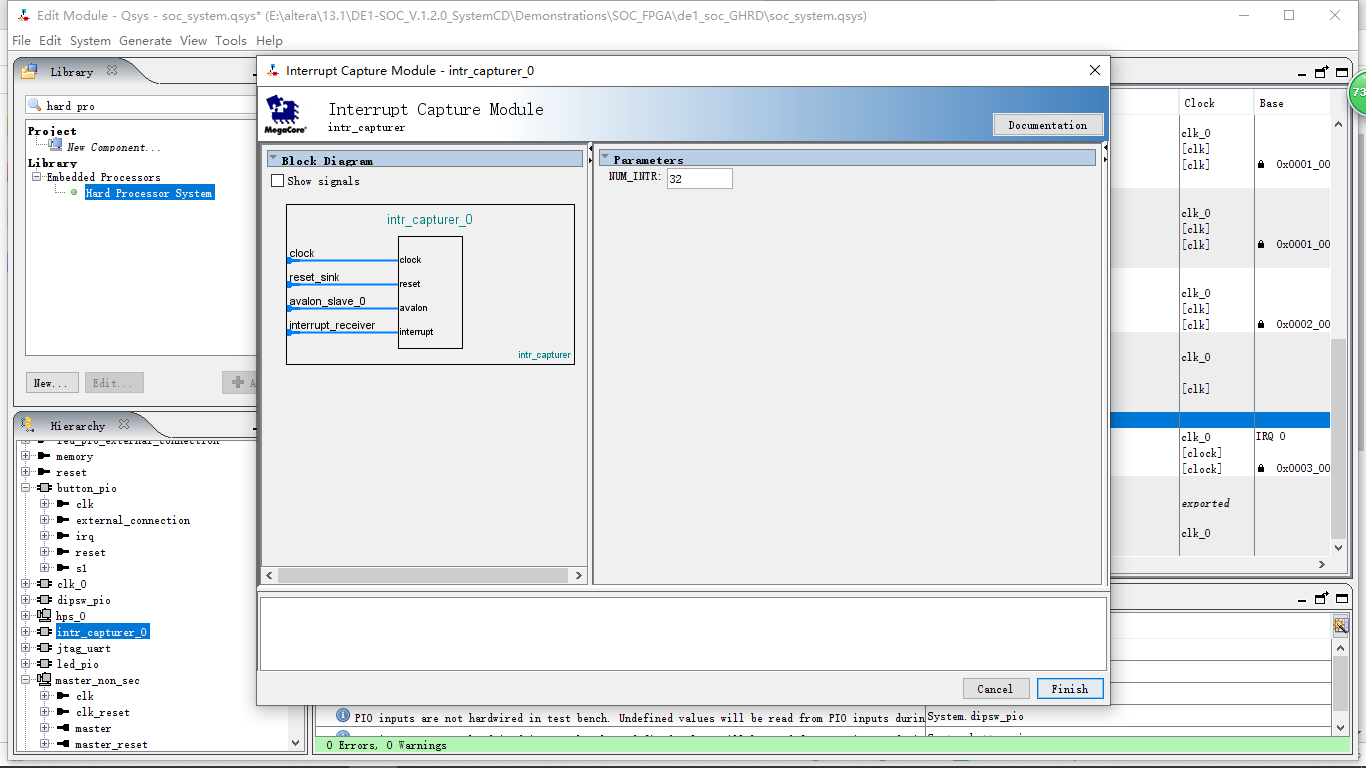

Interrupt capture module(名字为intr_capturer_0)

clock

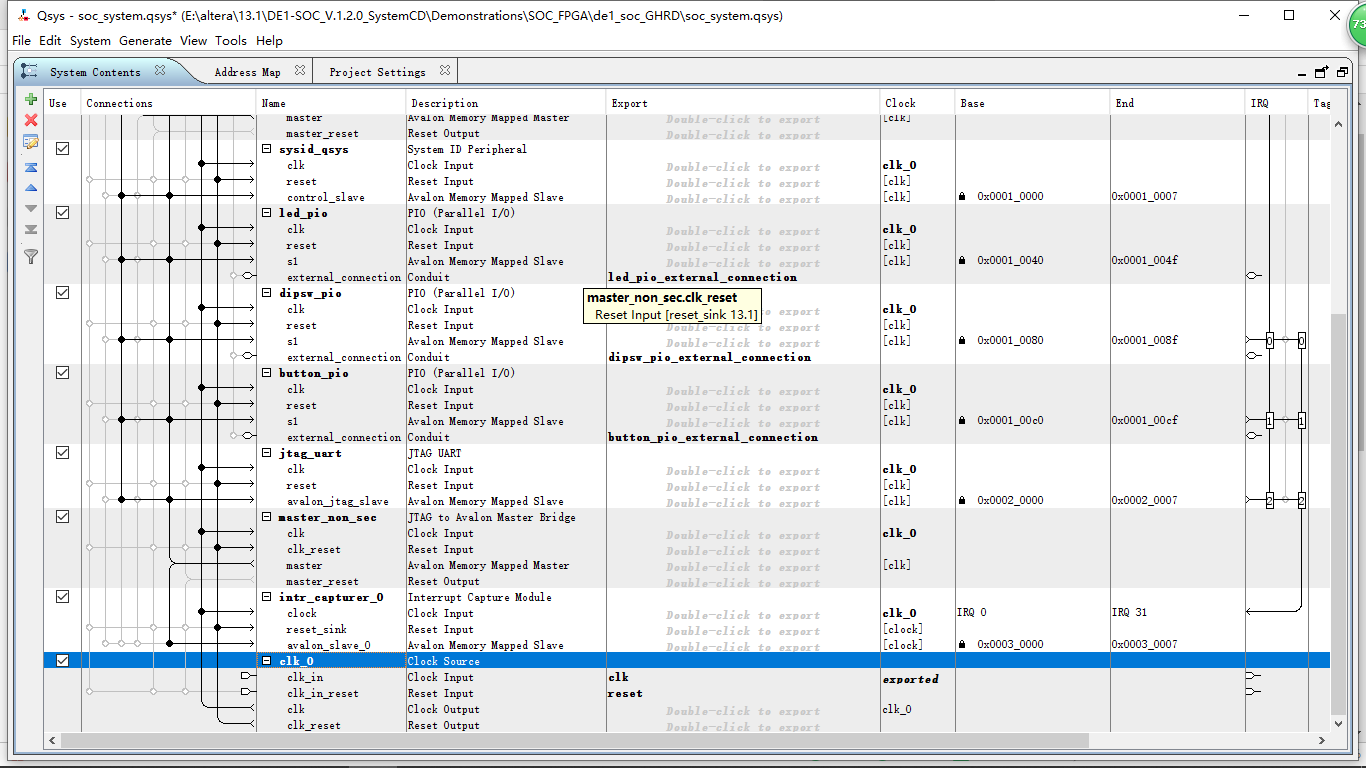

系统组件添加完成,现在开始连接

将onchip_memory2_o的的地址设为0x0000_0000。锁定为基地址,并选择自动分配地址

在设定中断优先级

在0错误下编译生成Qsys系统

选择generate---generate

save保存生成;(Generate complete)

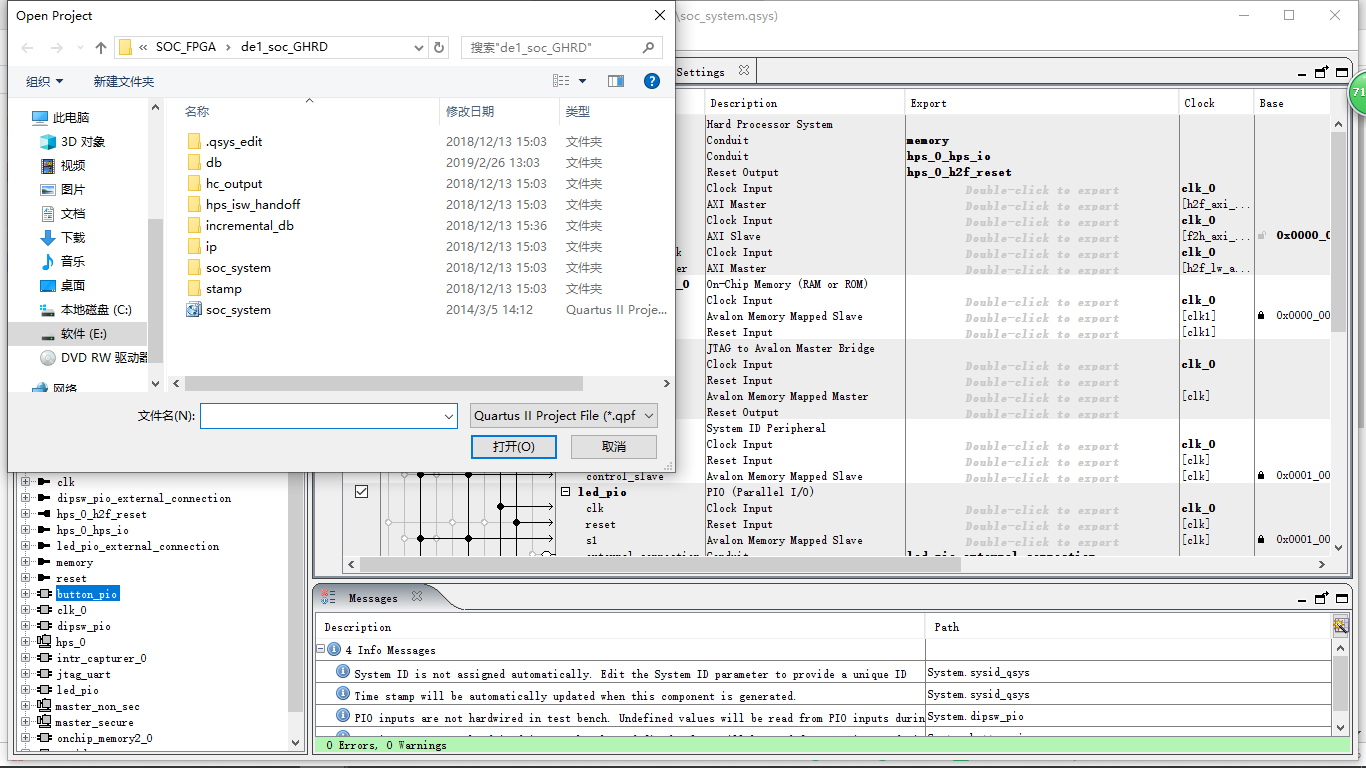

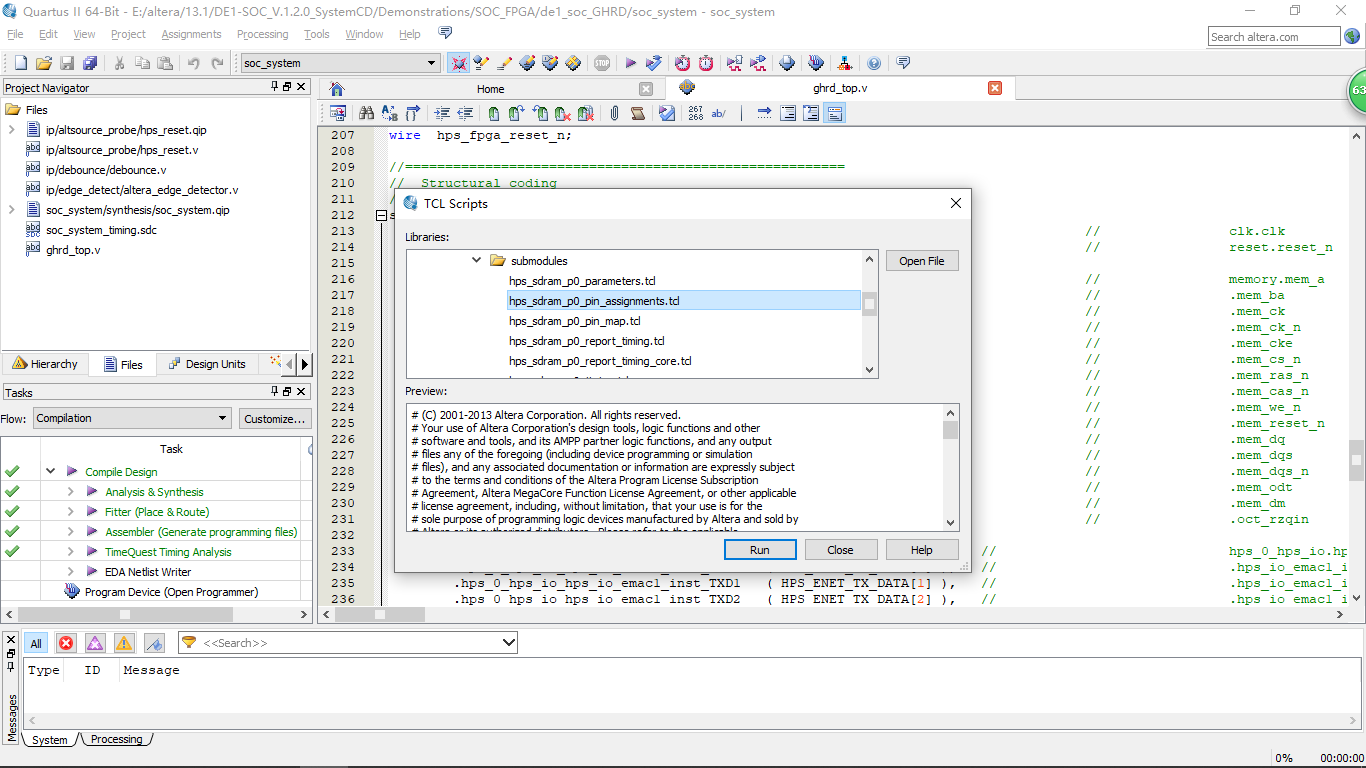

在工程中添加生成的Qsys文件

添加sos_system.qip和sos_system_timing.sdc文件

新建ghrd_top.v文件

文件代码如下

`define ENABLE_HPS

module ghrd_top(

///////// ADC /////////

output ADC_CS_n,

output ADC_DIN,

input ADC_DOUT,

output ADC_SCLK,

///////// AUD /////////

input AUD_ADCDAT,

inout AUD_ADCLRCK,

inout AUD_BCLK,

output AUD_DACDAT,

inout AUD_DACLRCK,

output AUD_XCK,

///////// CLOCK2 /////////

input CLOCK2_50,

///////// CLOCK3 /////////

input CLOCK3_50,

///////// CLOCK4 /////////

input CLOCK4_50,

///////// CLOCK /////////

input CLOCK_50,

///////// DRAM /////////

output [:] DRAM_ADDR,

output [:] DRAM_BA,

output DRAM_CAS_n,

output DRAM_CKE,

output DRAM_CLK,

output DRAM_CS_N,

inout [:] DRAM_DQ,

output DRAM_LDQM,

output DRAM_RAS_N,

output DRAM_UDQM,

output DRAM_WE_N,

///////// FAN /////////

output FAN_CTRL,

///////// FPGA /////////

output FPGA_I2C_SCLK,

inout FPGA_I2C_SDAT,

///////// GPIO /////////

inout [:] GPIO_A,

inout [:] GPIO_B,

///////// HEX0 /////////

output [:] HEX0,

///////// HEX1 /////////

output [:] HEX1,

///////// HEX2 /////////

output [:] HEX2,

///////// HEX3 /////////

output [:] HEX3,

///////// HEX4 /////////

output [:] HEX4,

///////// HEX5 /////////

output [:] HEX5,

`ifdef ENABLE_HPS

///////// HPS /////////

// input HPS_CLOCK1_25,

// input HPS_CLOCK2_25,

inout HPS_CONV_USB_N,

output [:] HPS_DDR3_ADDR,

output [:] HPS_DDR3_BA,

output HPS_DDR3_CAS_N,

output HPS_DDR3_CKE,

output HPS_DDR3_CK_N,

output HPS_DDR3_CK_P,

output HPS_DDR3_CS_N,

output [:] HPS_DDR3_DM,

inout [:] HPS_DDR3_DQ,

inout [:] HPS_DDR3_DQS_N,

inout [:] HPS_DDR3_DQS_P,

output HPS_DDR3_ODT,

output HPS_DDR3_RAS_N,

output HPS_DDR3_RESET_N,

input HPS_DDR3_RZQ,

output HPS_DDR3_WE_N,

output HPS_ENET_GTX_CLK,

inout HPS_ENET_INT_N,

output HPS_ENET_MDC,

inout HPS_ENET_MDIO,

input HPS_ENET_RX_CLK,

input [:] HPS_ENET_RX_DATA,

input HPS_ENET_RX_DV,

output [:] HPS_ENET_TX_DATA,

output HPS_ENET_TX_EN,

inout [:] HPS_FLASH_DATA,

output HPS_FLASH_DCLK,

output HPS_FLASH_NCSO,

inout [:] HPS_GPIO,

inout HPS_GSENSOR_INT,

inout HPS_I2C1_SCLK,

inout HPS_I2C1_SDAT,

inout HPS_I2C2_SCLK,

inout HPS_I2C2_SDAT,

inout HPS_I2C_CONTROL,

inout HPS_KEY,

inout HPS_LED,

// input HPS_RESET_N,

output HPS_SD_CLK,

inout HPS_SD_CMD,

inout [:] HPS_SD_DATA,

output HPS_SPIM_CLK,

input HPS_SPIM_MISO,

output HPS_SPIM_MOSI,

inout HPS_SPIM_SS,

input HPS_UART_RX,

output HPS_UART_TX,

input HPS_USB_CLKOUT,

inout [:] HPS_USB_DATA,

input HPS_USB_DIR,

input HPS_USB_NXT,

output HPS_USB_STP,

// output HPS_WARM_RST_N,

`endif /*ENABLE_HPS*/

///////// IRDA /////////

input IRDA_RXD,

output IRDA_TXD,

///////// KEY /////////

input [:] KEY,

///////// LEDR /////////

output [:] LEDR,

///////// PS2 /////////

inout PS2_CLK,

inout PS2_CLK2,

inout PS2_DAT,

inout PS2_DAT2,

///////// SW /////////

input [:] SW,

///////// TD /////////

inout TD_CLK27,

output [:] TD_DATA,

output TD_HS,

output TD_RESET_N,

output TD_VS,

///////// VGA /////////

output VGA_BLANK_N,

output [:] VGA_B,

output VGA_CLK,

output [:] VGA_G,

output VGA_HS,

output [:] VGA_R,

output VGA_SYNC_N,

output VGA_VS

);

//=======================================================

// REG/WIRE declarations

//=======================================================

wire hps_fpga_reset_n;

//=======================================================

// Structural coding

//=======================================================

soc_system u0 (

.clk_clk (CLOCK_50), // clk.clk

.reset_reset_n ('b1), // reset.reset_n

//HPS ddr3

.memory_mem_a ( HPS_DDR3_ADDR), // memory.mem_a

.memory_mem_ba ( HPS_DDR3_BA), // .mem_ba

.memory_mem_ck ( HPS_DDR3_CK_P), // .mem_ck

.memory_mem_ck_n ( HPS_DDR3_CK_N), // .mem_ck_n

.memory_mem_cke ( HPS_DDR3_CKE), // .mem_cke

.memory_mem_cs_n ( HPS_DDR3_CS_N), // .mem_cs_n

.memory_mem_ras_n ( HPS_DDR3_RAS_N), // .mem_ras_n

.memory_mem_cas_n ( HPS_DDR3_CAS_N), // .mem_cas_n

.memory_mem_we_n ( HPS_DDR3_WE_N), // .mem_we_n

.memory_mem_reset_n ( HPS_DDR3_RESET_N), // .mem_reset_n

.memory_mem_dq ( HPS_DDR3_DQ), // .mem_dq

.memory_mem_dqs ( HPS_DDR3_DQS_P), // .mem_dqs

.memory_mem_dqs_n ( HPS_DDR3_DQS_N), // .mem_dqs_n

.memory_mem_odt ( HPS_DDR3_ODT), // .mem_odt

.memory_mem_dm ( HPS_DDR3_DM), // .mem_dm

.memory_oct_rzqin ( HPS_DDR3_RZQ), // .oct_rzqin

//HPS ethernet

.hps_0_hps_io_hps_io_emac1_inst_TX_CLK ( HPS_ENET_GTX_CLK), // hps_0_hps_io.hps_io_emac1_inst_TX_CLK

.hps_0_hps_io_hps_io_emac1_inst_TXD0 ( HPS_ENET_TX_DATA[] ), // .hps_io_emac1_inst_TXD0

.hps_0_hps_io_hps_io_emac1_inst_TXD1 ( HPS_ENET_TX_DATA[] ), // .hps_io_emac1_inst_TXD1

.hps_0_hps_io_hps_io_emac1_inst_TXD2 ( HPS_ENET_TX_DATA[] ), // .hps_io_emac1_inst_TXD2

.hps_0_hps_io_hps_io_emac1_inst_TXD3 ( HPS_ENET_TX_DATA[] ), // .hps_io_emac1_inst_TXD3

.hps_0_hps_io_hps_io_emac1_inst_RXD0 ( HPS_ENET_RX_DATA[] ), // .hps_io_emac1_inst_RXD0

.hps_0_hps_io_hps_io_emac1_inst_MDIO ( HPS_ENET_MDIO ), // .hps_io_emac1_inst_MDIO

.hps_0_hps_io_hps_io_emac1_inst_MDC ( HPS_ENET_MDC ), // .hps_io_emac1_inst_MDC

.hps_0_hps_io_hps_io_emac1_inst_RX_CTL ( HPS_ENET_RX_DV), // .hps_io_emac1_inst_RX_CTL

.hps_0_hps_io_hps_io_emac1_inst_TX_CTL ( HPS_ENET_TX_EN), // .hps_io_emac1_inst_TX_CTL

.hps_0_hps_io_hps_io_emac1_inst_RX_CLK ( HPS_ENET_RX_CLK), // .hps_io_emac1_inst_RX_CLK

.hps_0_hps_io_hps_io_emac1_inst_RXD1 ( HPS_ENET_RX_DATA[] ), // .hps_io_emac1_inst_RXD1

.hps_0_hps_io_hps_io_emac1_inst_RXD2 ( HPS_ENET_RX_DATA[] ), // .hps_io_emac1_inst_RXD2

.hps_0_hps_io_hps_io_emac1_inst_RXD3 ( HPS_ENET_RX_DATA[] ), // .hps_io_emac1_inst_RXD3

//HPS QSPI

.hps_0_hps_io_hps_io_qspi_inst_IO0 ( HPS_FLASH_DATA[] ), // .hps_io_qspi_inst_IO0

.hps_0_hps_io_hps_io_qspi_inst_IO1 ( HPS_FLASH_DATA[] ), // .hps_io_qspi_inst_IO1

.hps_0_hps_io_hps_io_qspi_inst_IO2 ( HPS_FLASH_DATA[] ), // .hps_io_qspi_inst_IO2

.hps_0_hps_io_hps_io_qspi_inst_IO3 ( HPS_FLASH_DATA[] ), // .hps_io_qspi_inst_IO3

.hps_0_hps_io_hps_io_qspi_inst_SS0 ( HPS_FLASH_NCSO ), // .hps_io_qspi_inst_SS0

.hps_0_hps_io_hps_io_qspi_inst_CLK ( HPS_FLASH_DCLK ), // .hps_io_qspi_inst_CLK

//HPS SD card

.hps_0_hps_io_hps_io_sdio_inst_CMD ( HPS_SD_CMD ), // .hps_io_sdio_inst_CMD

.hps_0_hps_io_hps_io_sdio_inst_D0 ( HPS_SD_DATA[] ), // .hps_io_sdio_inst_D0

.hps_0_hps_io_hps_io_sdio_inst_D1 ( HPS_SD_DATA[] ), // .hps_io_sdio_inst_D1

.hps_0_hps_io_hps_io_sdio_inst_CLK ( HPS_SD_CLK ), // .hps_io_sdio_inst_CLK

.hps_0_hps_io_hps_io_sdio_inst_D2 ( HPS_SD_DATA[] ), // .hps_io_sdio_inst_D2

.hps_0_hps_io_hps_io_sdio_inst_D3 ( HPS_SD_DATA[] ), // .hps_io_sdio_inst_D3

//HPS USB

.hps_0_hps_io_hps_io_usb1_inst_D0 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D0

.hps_0_hps_io_hps_io_usb1_inst_D1 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D1

.hps_0_hps_io_hps_io_usb1_inst_D2 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D2

.hps_0_hps_io_hps_io_usb1_inst_D3 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D3

.hps_0_hps_io_hps_io_usb1_inst_D4 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D4

.hps_0_hps_io_hps_io_usb1_inst_D5 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D5

.hps_0_hps_io_hps_io_usb1_inst_D6 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D6

.hps_0_hps_io_hps_io_usb1_inst_D7 ( HPS_USB_DATA[] ), // .hps_io_usb1_inst_D7

.hps_0_hps_io_hps_io_usb1_inst_CLK ( HPS_USB_CLKOUT ), // .hps_io_usb1_inst_CLK

.hps_0_hps_io_hps_io_usb1_inst_STP ( HPS_USB_STP ), // .hps_io_usb1_inst_STP

.hps_0_hps_io_hps_io_usb1_inst_DIR ( HPS_USB_DIR ), // .hps_io_usb1_inst_DIR

.hps_0_hps_io_hps_io_usb1_inst_NXT ( HPS_USB_NXT ), // .hps_io_usb1_inst_NXT

//HPS SPI

.hps_0_hps_io_hps_io_spim1_inst_CLK ( HPS_SPIM_CLK ), // .hps_io_spim1_inst_CLK

.hps_0_hps_io_hps_io_spim1_inst_MOSI ( HPS_SPIM_MOSI ), // .hps_io_spim1_inst_MOSI

.hps_0_hps_io_hps_io_spim1_inst_MISO ( HPS_SPIM_MISO ), // .hps_io_spim1_inst_MISO

.hps_0_hps_io_hps_io_spim1_inst_SS0 ( HPS_SPIM_SS ), // .hps_io_spim1_inst_SS0

//HPS UART

.hps_0_hps_io_hps_io_uart0_inst_RX ( HPS_UART_RX ), // .hps_io_uart0_inst_RX

.hps_0_hps_io_hps_io_uart0_inst_TX ( HPS_UART_TX ), // .hps_io_uart0_inst_TX

//HPS I2C1

.hps_0_hps_io_hps_io_i2c0_inst_SDA ( HPS_I2C1_SDAT ), // .hps_io_i2c0_inst_SDA

.hps_0_hps_io_hps_io_i2c0_inst_SCL ( HPS_I2C1_SCLK ), // .hps_io_i2c0_inst_SCL

//HPS I2C2

.hps_0_hps_io_hps_io_i2c1_inst_SDA ( HPS_I2C2_SDAT ), // .hps_io_i2c1_inst_SDA

.hps_0_hps_io_hps_io_i2c1_inst_SCL ( HPS_I2C2_SCLK ), // .hps_io_i2c1_inst_SCL

//HPS GPIO

.hps_0_hps_io_hps_io_gpio_inst_GPIO09 ( HPS_CONV_USB_N), // .hps_io_gpio_inst_GPIO09

.hps_0_hps_io_hps_io_gpio_inst_GPIO35 ( HPS_ENET_INT_N), // .hps_io_gpio_inst_GPIO35

.hps_0_hps_io_hps_io_gpio_inst_GPIO40 ( HPS_GPIO[]), // .hps_io_gpio_inst_GPIO40

.hps_0_hps_io_hps_io_gpio_inst_GPIO41 ( HPS_GPIO[]), // .hps_io_gpio_inst_GPIO41

.hps_0_hps_io_hps_io_gpio_inst_GPIO48 ( HPS_I2C_CONTROL), // .hps_io_gpio_inst_GPIO48

.hps_0_hps_io_hps_io_gpio_inst_GPIO53 ( HPS_LED), // .hps_io_gpio_inst_GPIO53

.hps_0_hps_io_hps_io_gpio_inst_GPIO54 ( HPS_KEY), // .hps_io_gpio_inst_GPIO54

.hps_0_hps_io_hps_io_gpio_inst_GPIO61 ( HPS_GSENSOR_INT), // .hps_io_gpio_inst_GPIO61

//FPGA soft GPIO

.led_pio_external_connection_export ( LEDR ), // led_pio_external_connection.export

.dipsw_pio_external_connection_export ( SW ), // dipsw_pio_external_connection.export

.button_pio_external_connection_export ( KEY ), // button_pio_external_connection.export

//HPS reset output

.hps_0_h2f_reset_reset_n (hps_fpga_reset_n), // hps_0_h2f_reset.reset_n

);

endmodule

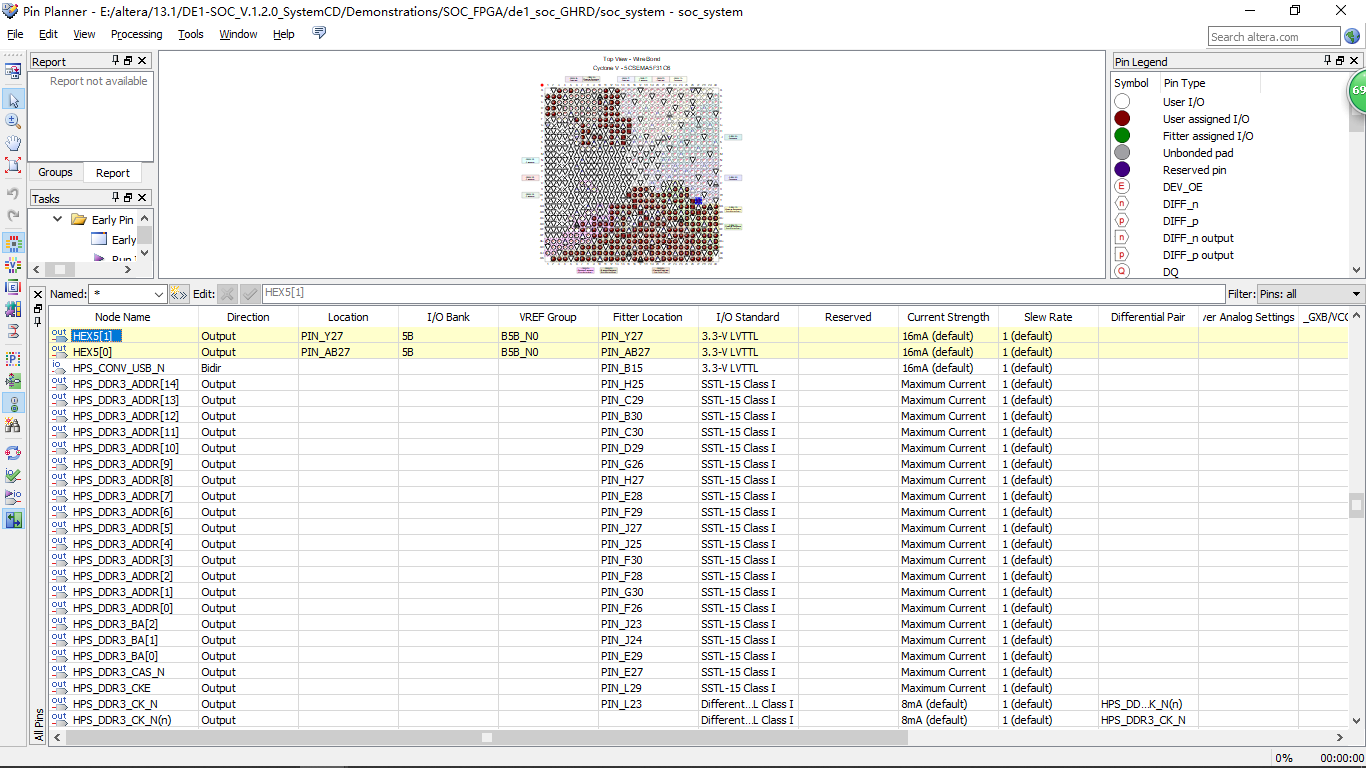

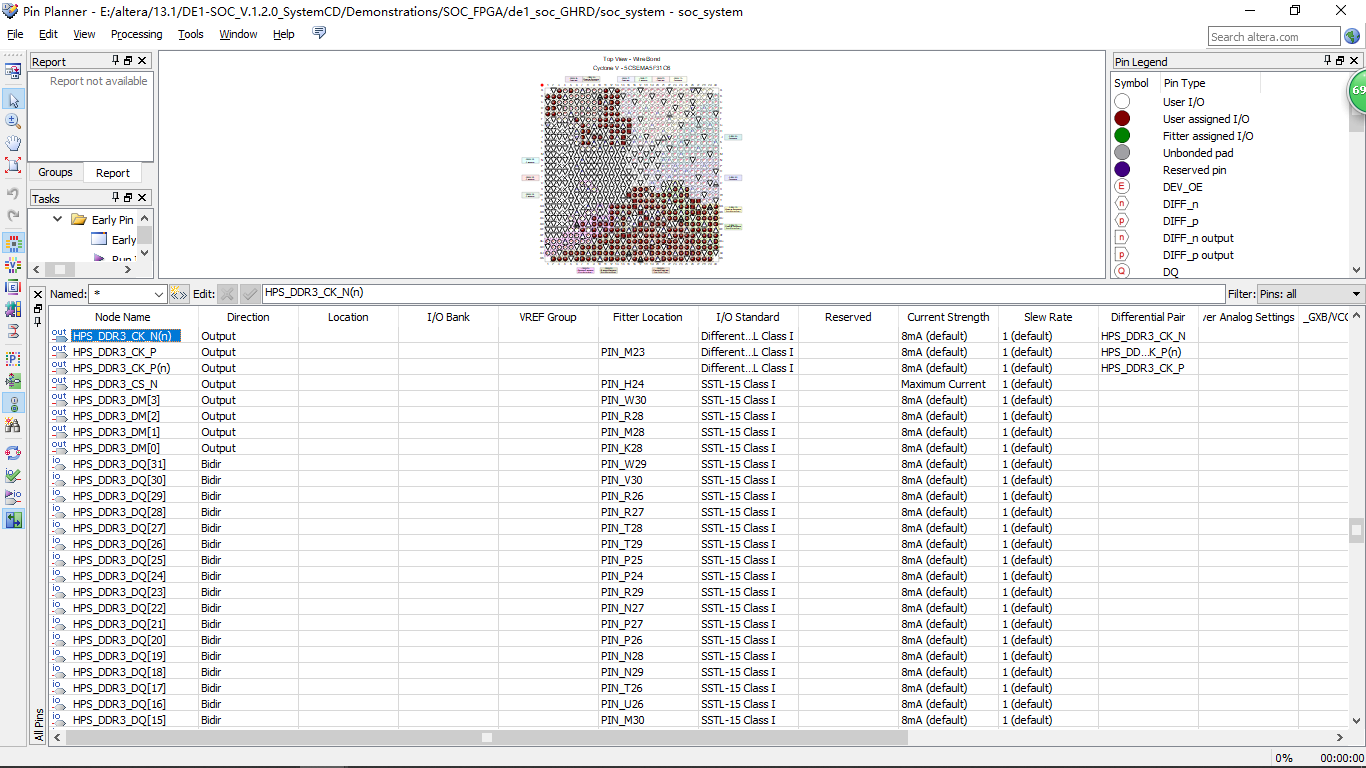

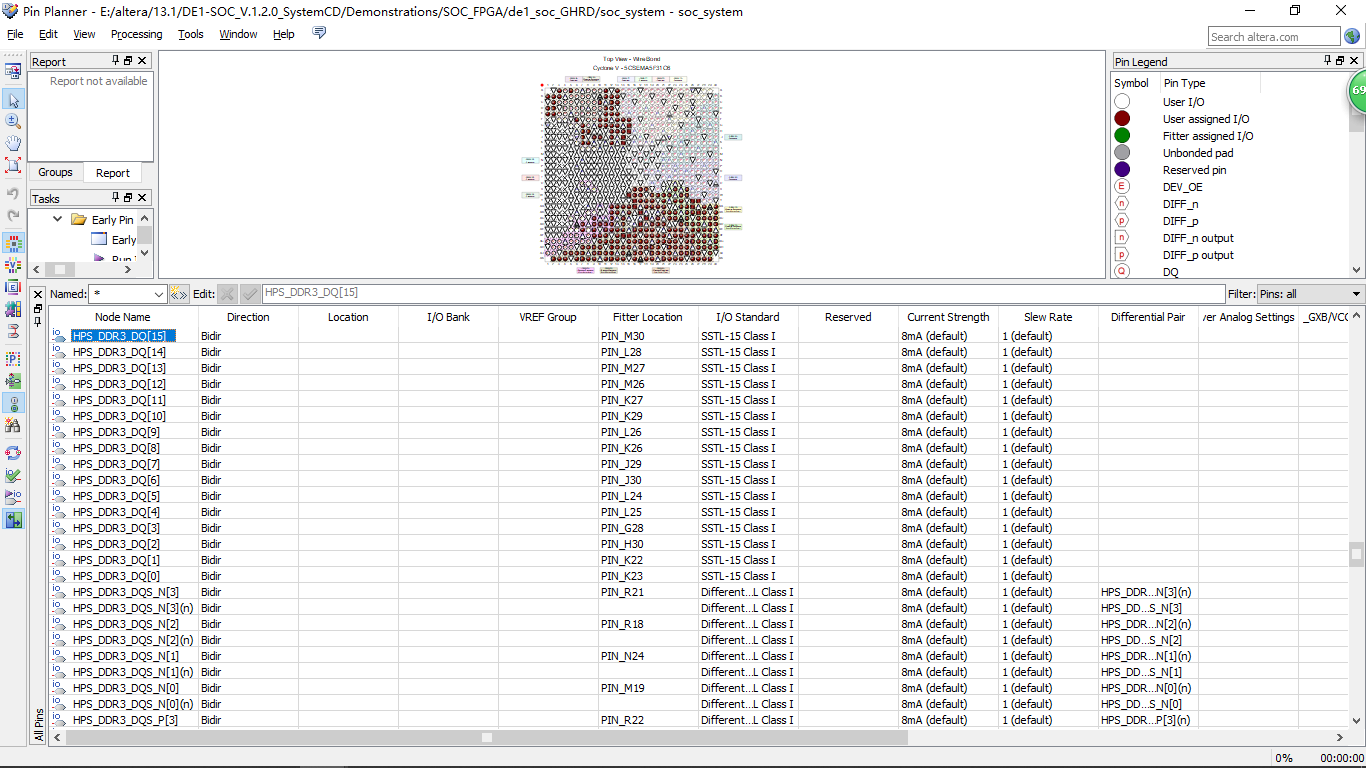

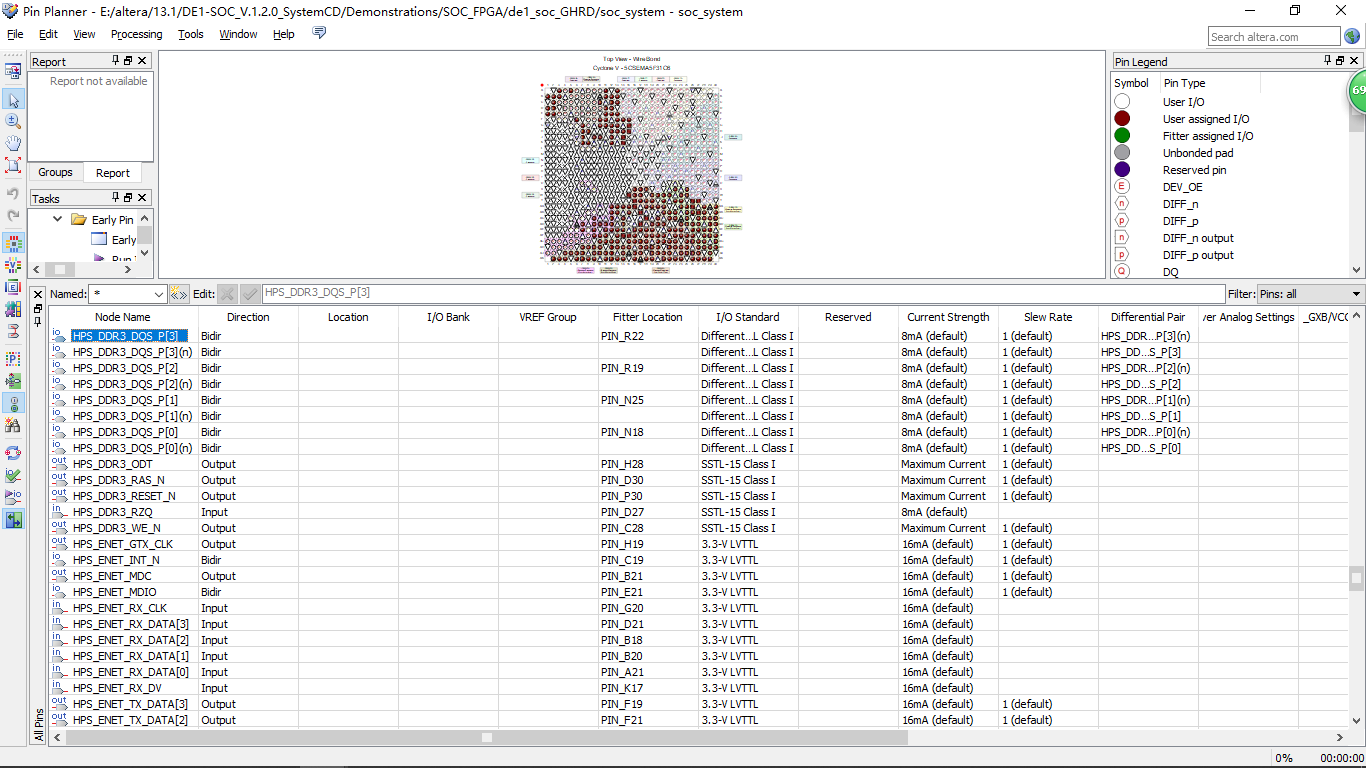

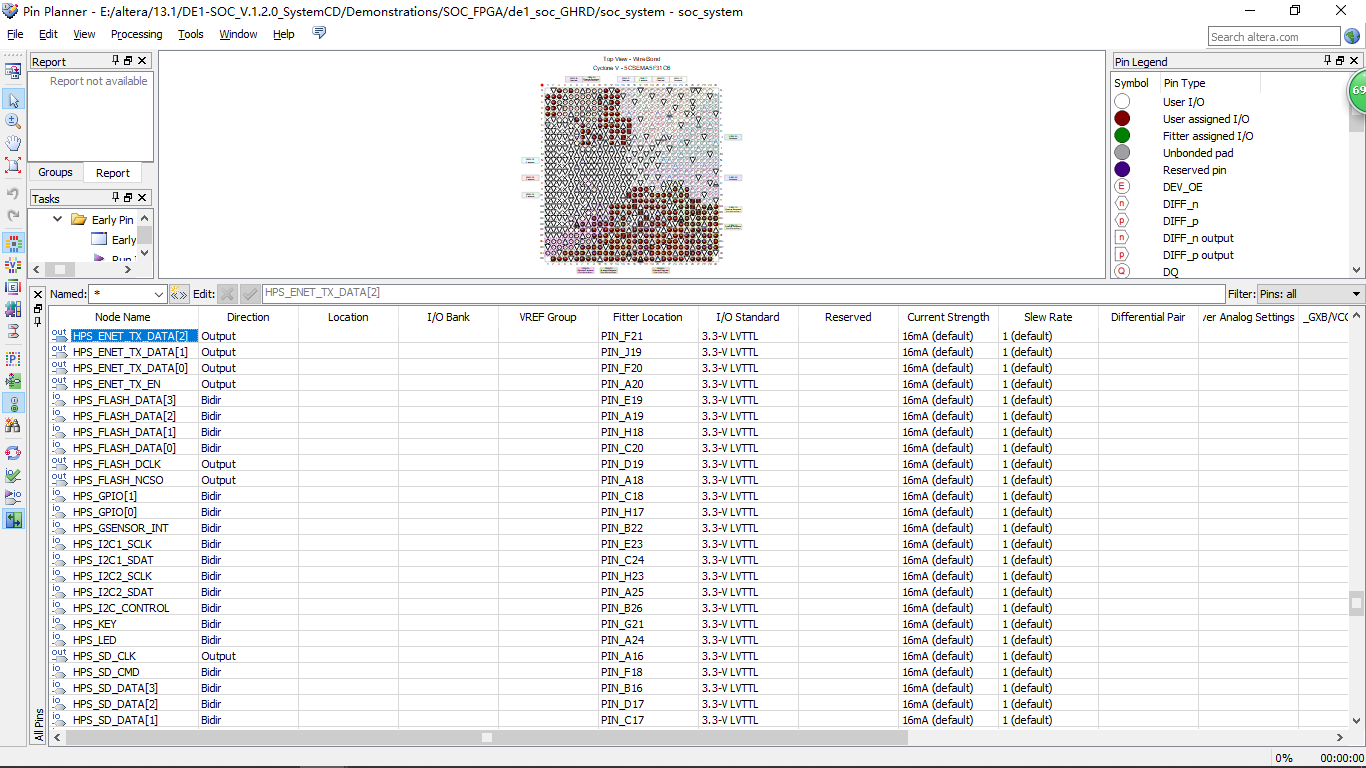

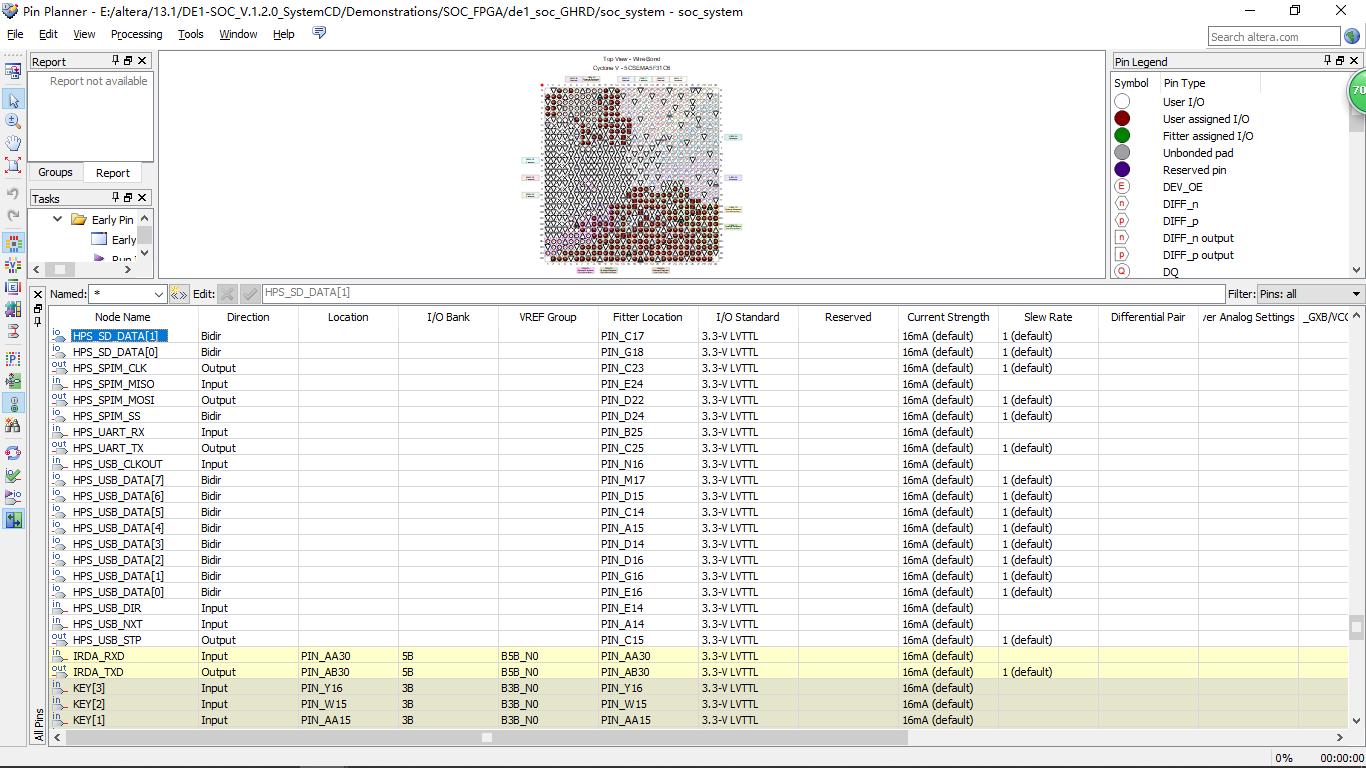

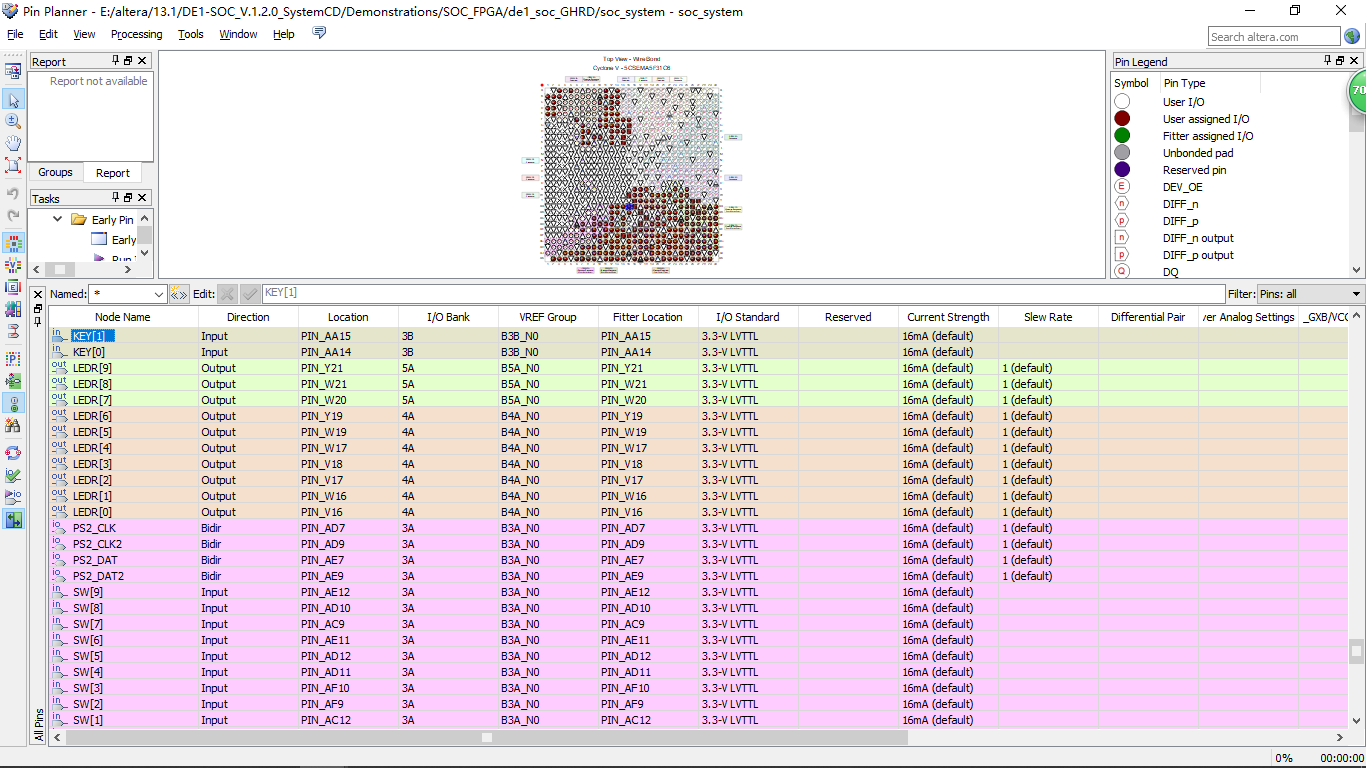

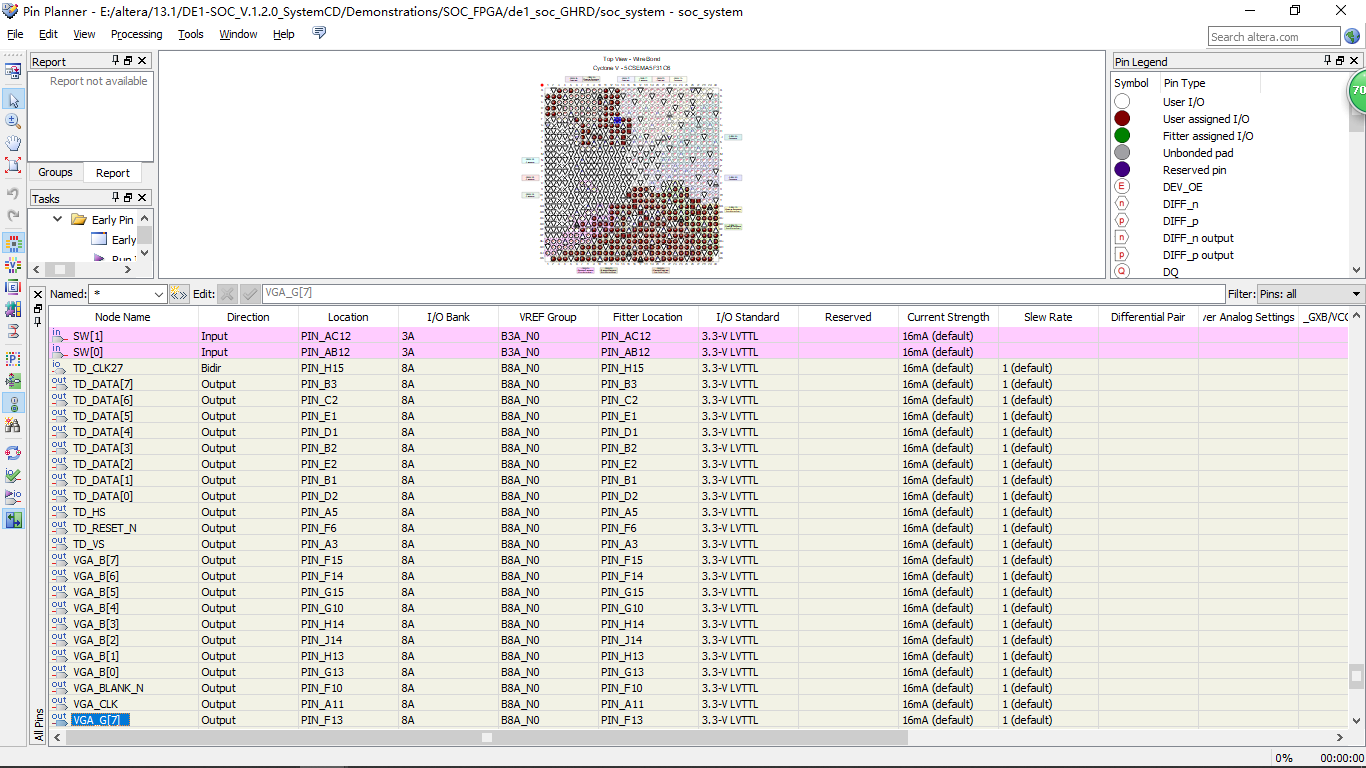

上述图片是例化引脚;

分析和综合后无错误;

选择Tools-TCL scrip;

选择RUN,运行完成点ok;

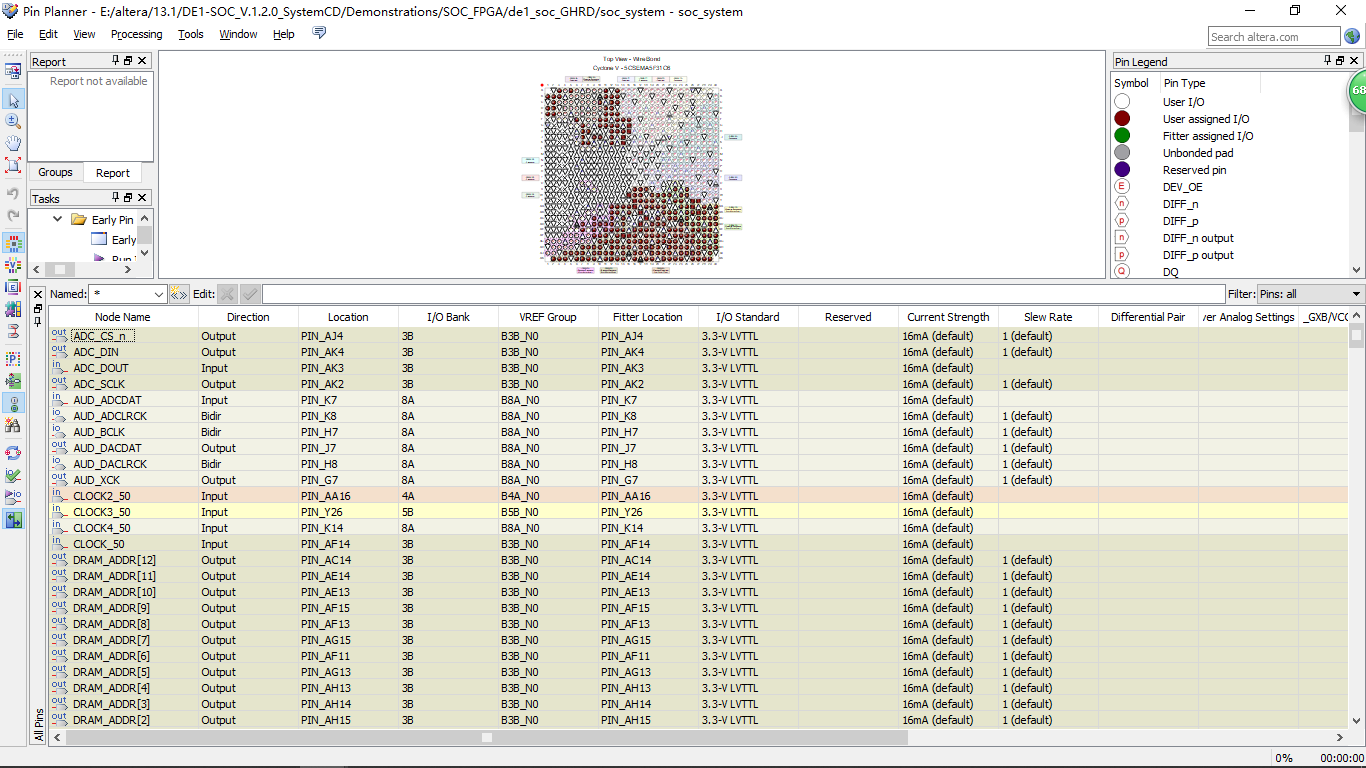

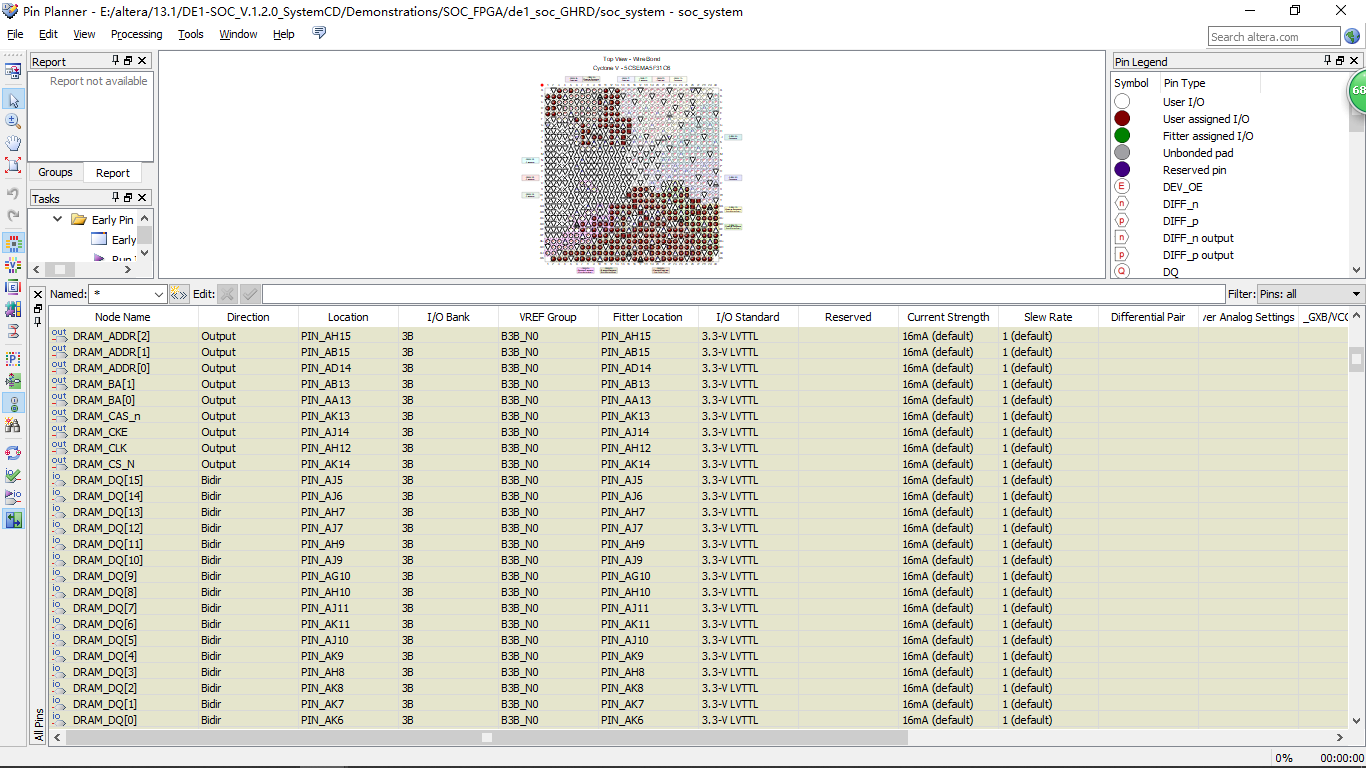

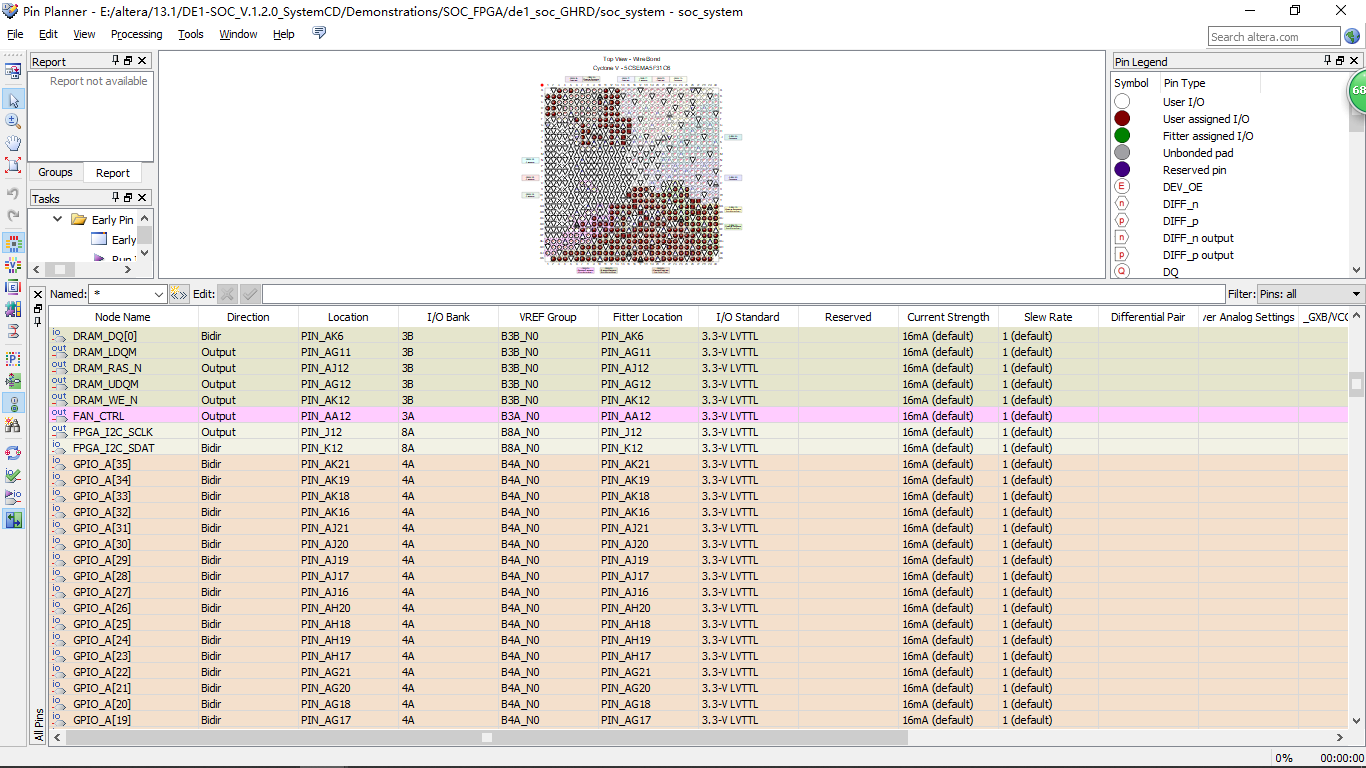

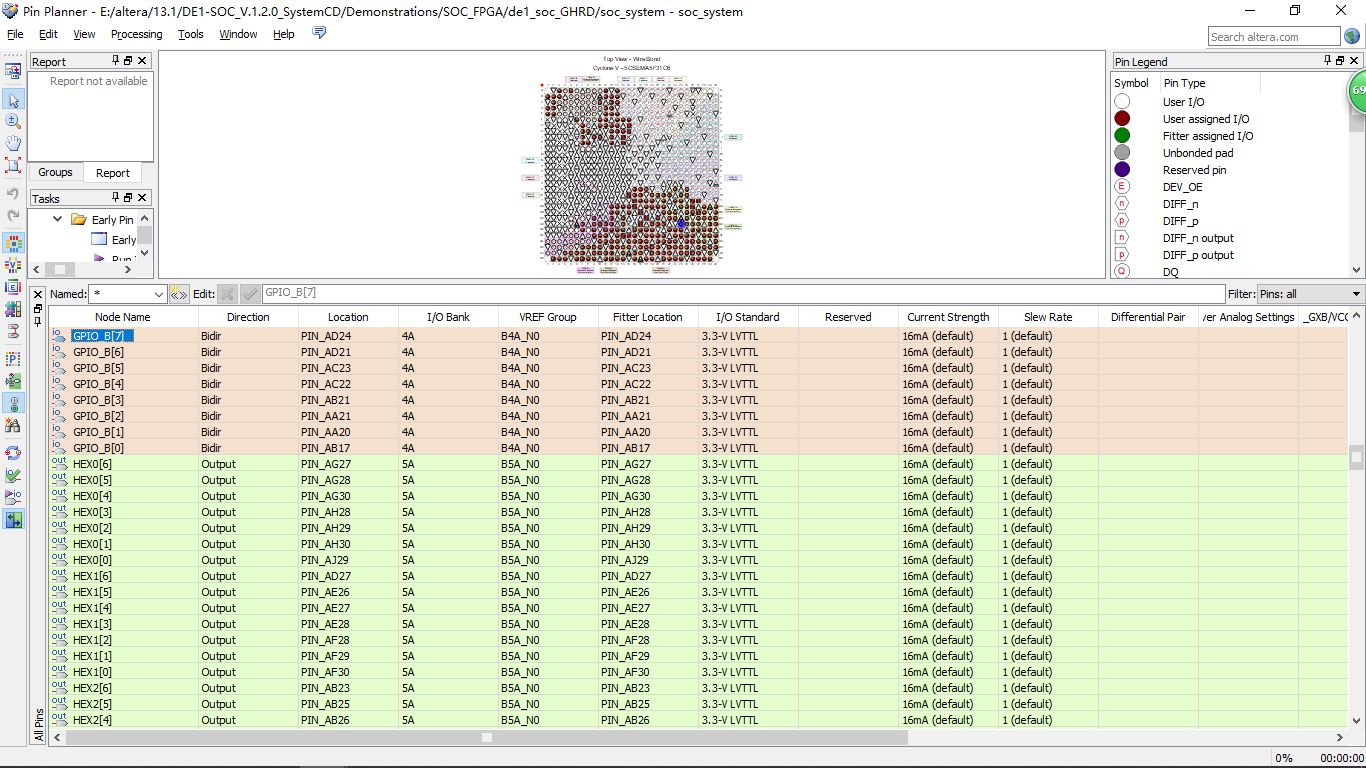

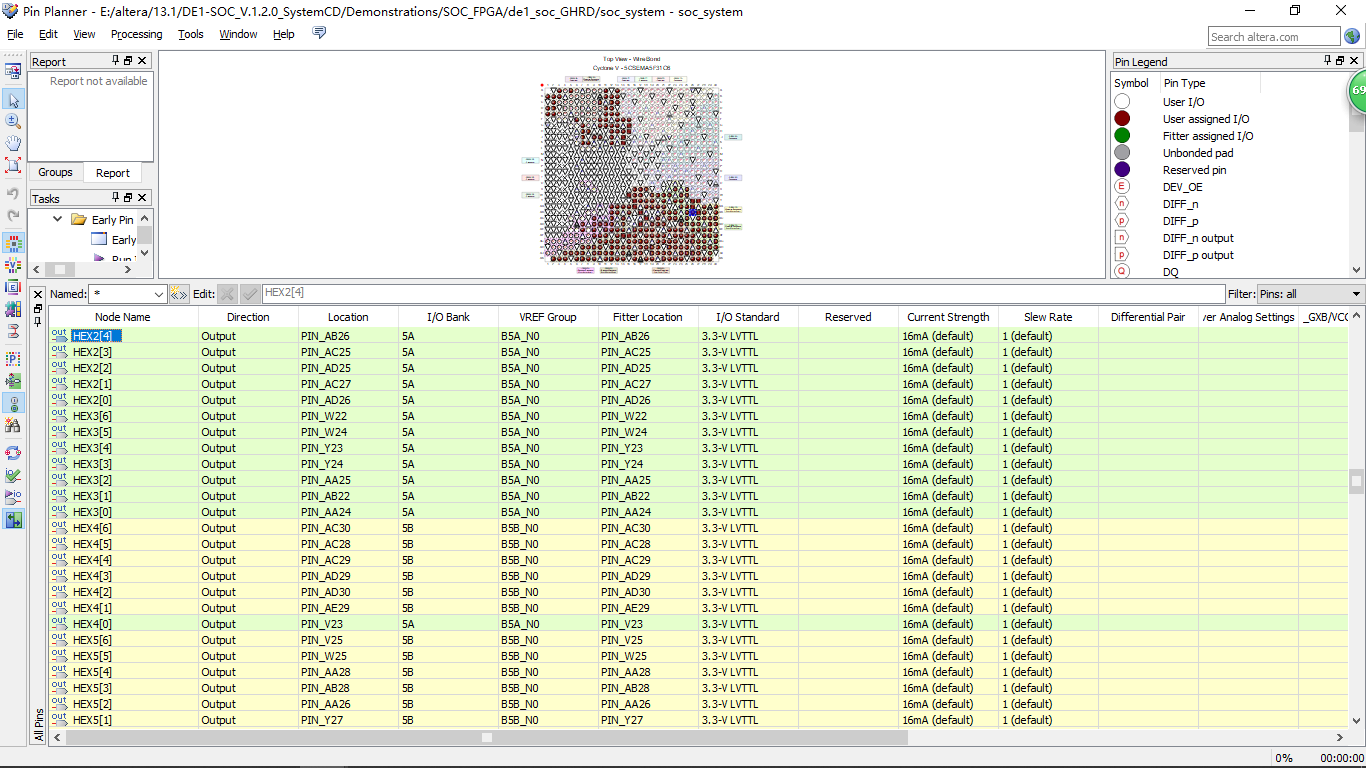

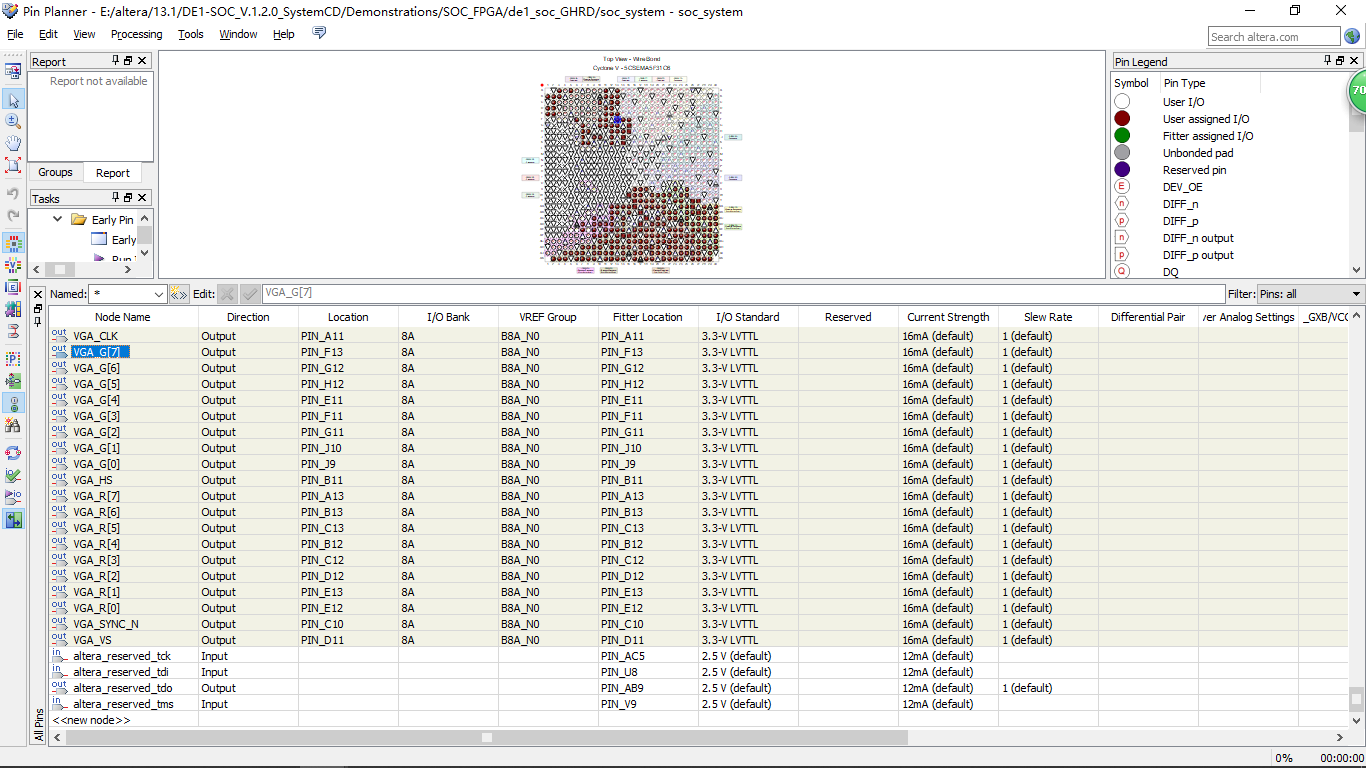

配置引脚选择PIN planner

在点击全编译;

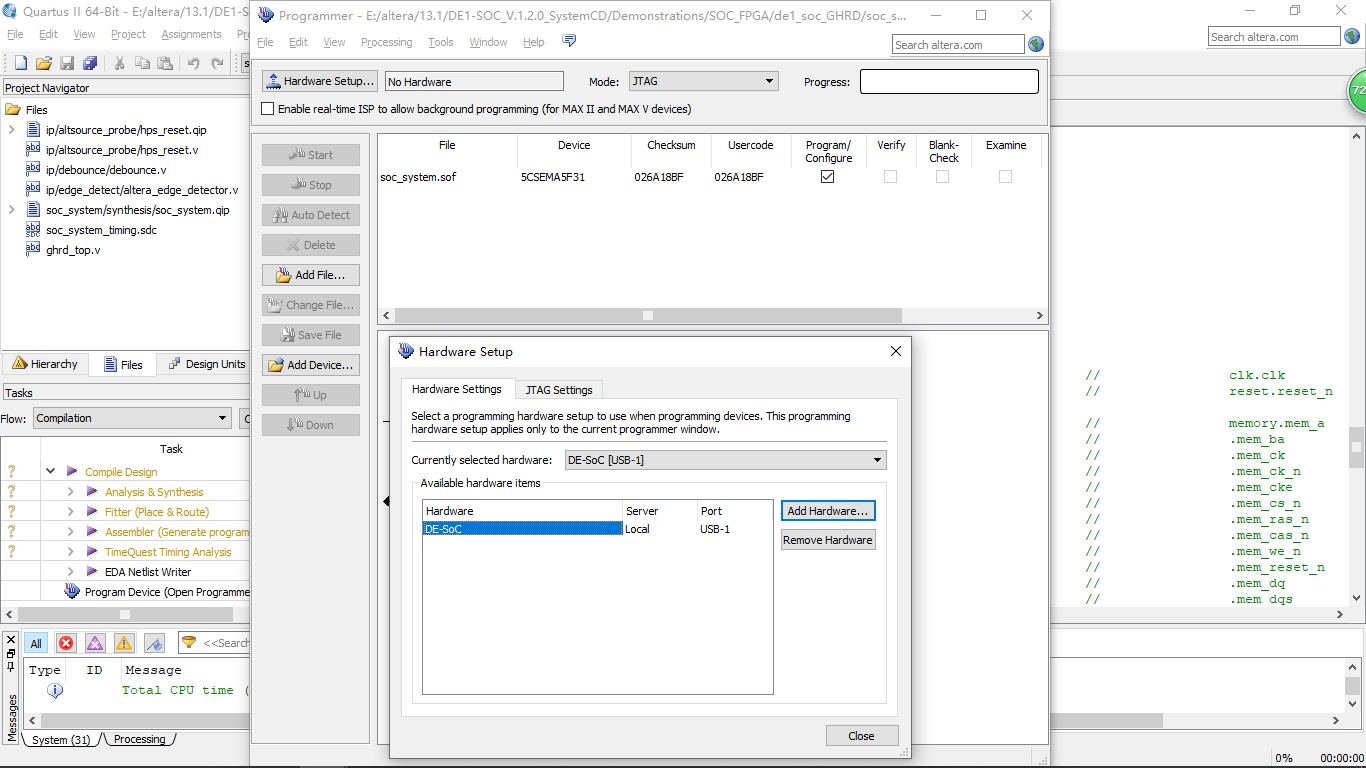

最后进行FPGA配置

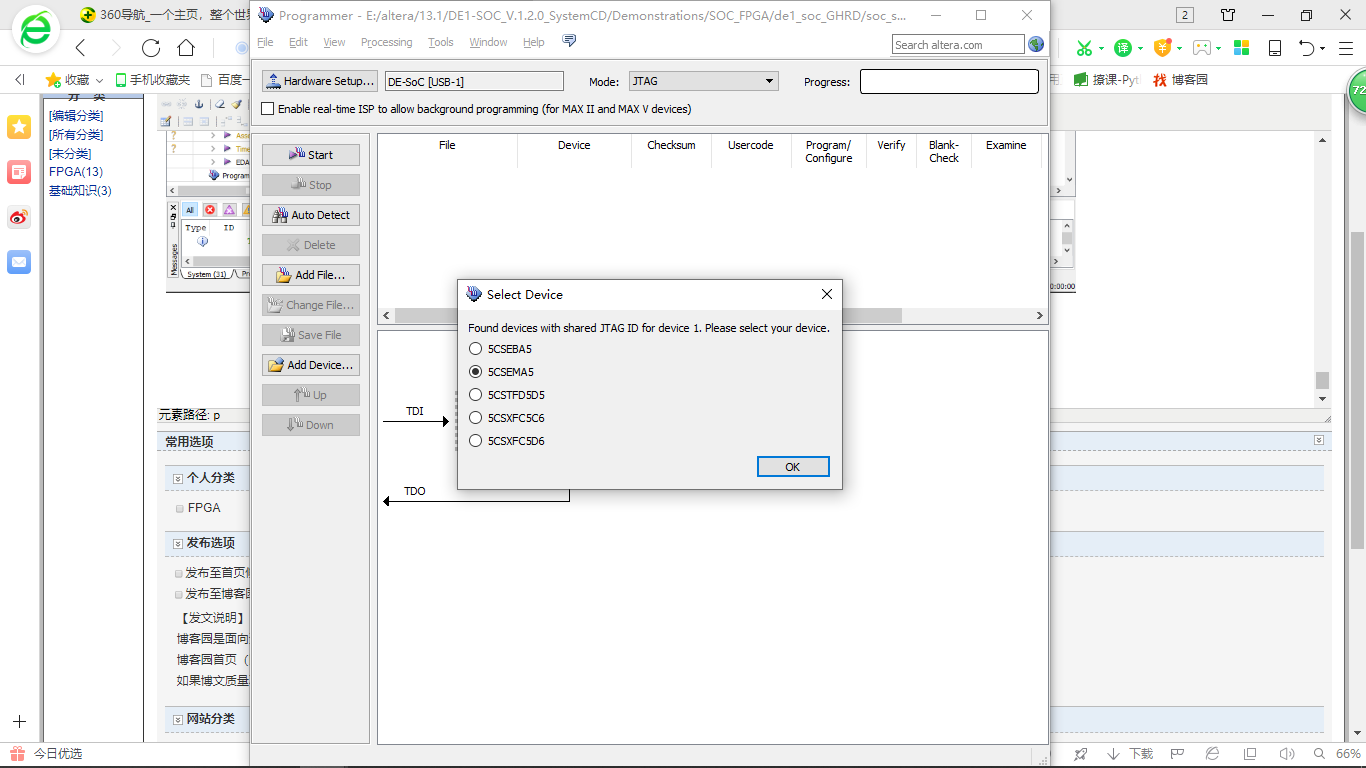

选择Auto Detect

这只是GHRD的常规操作步骤,详情请见下次

DE1-GHRD的更多相关文章

- arm-linux下qt + opencv开发环境的搭建(Altera DE1 Soc)

arm-linux-gnueabihf-gcc下载 qt下载 arm-linux下qt + opencv开发环境的搭建(Altera DE1 Soc) Ubuntu 16.04 安装QT arm嵌入式 ...

- DE1+回顾

本实验使用DE1器件,cyloneV,主要做的基础实验,目的是回顾前期的学习和巩固知识和熟悉操作流程. 视频主要学习的是小梅哥视频. 工程文件夹取名 prj ----- 工程文件存放目录(ip文件 ...

- (GHRD)HPS

DE1作为ARM+FPGA的组合,ARM和FPGA之间通信,两个区块间有三个通道可以让两部分实现传输数据,统称为 HPS-FPGA AXI Bridges. 分别为:FPGA-to-HPS Bridg ...

- (ghrd)pio设置

设置中是下降沿,边沿触发.

- 联网调试DE1

步骤:打开PUTTY,com3,串口,115200 重启开发板, 输入root, 输入 cd /mnt 输入 ifconfig 尝试一下自动分配网址:udhcpc 网络直连失败,原因占时不知 ...

- shell及脚本4——shell script

一.格式 1.1 开头 必须以 "# !/bin/bash" 开头,告诉系统这是一个bash shell脚本.注意#与!中间有空格. 二.语法 2.1 数值运算 可以用decla ...

- Android学习——windows下搭建Cygwin环境

在上一篇博文<Android学习——windows下搭建NDK_r9环境>中,我们详细的讲解了在windows下进行Android NDK开发环境的配置,我们也讲到了在NDk r7以后,我 ...

- Java学习笔记(04)

Java学习笔记(04) 如有不对或不足的地方,请给出建议,谢谢! 一.对象 面向对象的核心:找合适的对象做合适的事情 面向对象的编程思想:尽可能的用计算机语言来描述现实生活中的事物 面向对象:侧重于 ...

- html/css小练习1

aaarticlea/png;base64,iVBORw0KGgoAAAANSUhEUgAAAywAAAFgCAIAAADW6Wr0AAAgAElEQVR4nOzdd1xT5+L48bJlhUAGCY

- Psp个人软件开发软件需求分析和用例分析

Psp个人软件开发软件需求分析和用例分析 一.需求分析 1.业务需求 1.1 应用背景 开发项目进度计划总是那么不明确,延期经常出现,甚至无法给出一个相对比较明确的延迟时间.这样给市场的推广会带来很大 ...

随机推荐

- Callablestatement与JavaBean及其实例

一. Callablestatement:调用 数据库中的存储过程.存储函数 connection.prepareCall(参数:存储过程/存储函数名)参数格式:存储过程:(无返回值return,用O ...

- ClosedXML、DocumentFormat.OpenXml导出DataTable到Excel

在很多系统中都用到导出,使用过多种导出方式,觉得ClosedXML插件的导出简单又方便. 并且ClosedXML.DocumentFormat.OpenXml都是MIT开源. 首先通过 Nuget 安 ...

- 详解 CUDA By Example 中的 Julia Set 绘制GPU优化

笔者测试环境VS2019. 基本介绍 原书作者引入Julia Sets意在使用GPU加速图形的绘制.Julia Set 是指满足下式迭代收敛的复数集合 \[ Z_{n+1}=Z_{n}^2+C \] ...

- Spring 理解和开始

1.先看看Spring的历史吧 https://baijiahao.baidu.com/s?id=1620099105315862154&wfr=spider&for=pc 2.Spr ...

- laravel上传git如何忽略你不想提交的文件

1.在文件根目录下面有一个文件 .gitignore .gitignore文件用来忽略被指定的文件或文件夹的改动,被记录在.gitignore文件里的文件或文件夹,是无法被git跟踪到的,换句话说,被 ...

- babel 的简单使用

之前在项目中使用.balelrc文件,但是一直不知道具体怎么使用,就知道可以将es6语法转码为es5语法. 今天就简单的做个例子,也算是记录一下困扰了好久的问题. 转码步骤: 首先在项目的目录中安装B ...

- H3C RIP配置

一.RIP简介 RIP(Routing Information Protocol,路由信息协议)是一种较为简单的内部网关协议(Interior Gateway Protocol,IGP),主要用于规模 ...

- [JSOI2013] 快乐的 JYY - 回文自动机,DFS

#include <bits/stdc++.h> #define Sigma 30 #define MAXN 500010 #define int long long using name ...

- 【转】idea远程调试

适用于web服务,thrift服务 对于分布式系统的调试不知道大家有什么好的方法.对于我来说,在知道远程调试这个方法之前就是在代码中打各种log,然后重新部署,上线,调试,这样比较费时.今天咱们来了解 ...

- mybatis(五):源码分析 - mapper文件解析流程