ZYNQ Block Design中总线位宽的截取与合并操作

前言

在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作。

在verilog下,截位操作可如下所示:

wire [7:0] w_in;

wire [3:0] w_out;

assign w_out = win[3:0];合并操作可如下所示:

wire [3:0] w_in0;

wire [3:0] w_in1;

wire [7:0] w_out;

assign w_out = {w_in1,w_in0};所以问题就来了:如何在不写代码的情况下在block design设计中实现截取与合并的操作呢?

用到的IP

(1)constant IP。

此IP可以输出可配置位宽的常数,电平可配置0或者1。

(2)concat IP。

此IP可以使得分立的线拼接成单一线输出,相当于verilog描述的拼接操作。输入端口数和位宽均可配置。注意In1会放置在高位,[In1,In0]。

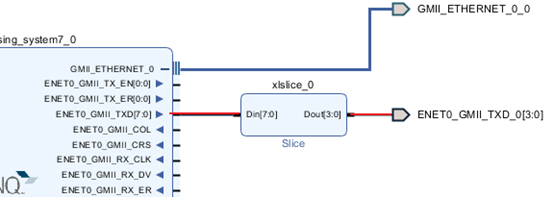

(3)slice IP。

此IP功能跟concat IP相反,会把输入截取想要的位宽输出。相当于verilog的位宽截取操作。输入位宽,输出位宽,截取msb和截取lsb都是可以配置的。

实例

100M网口使用MII接口。可以知道数据tx和rx都是4bit位宽的,但在MII IP接口中,数据位宽为8bit。则需截位与合并。

(1)总线位宽合并。

如下图所示,对于100M的网口使用,rx的高4bit需要接0。则需要使用到constant IP和concat IP。

(2)总线位宽截取。

对于100M网口的tx,高位是没用的,则通过slice IP截取低4bit作为输出。

重新生成wrapper,可以看到位宽符合预期,这么做的好处在于无需手动去修改生成的信号位宽,一劳永逸。

以上。

ZYNQ Block Design中总线位宽的截取与合并操作的更多相关文章

- ZYNQ block design警告:[BD 41-968] AXI interface port /axi_lite4 is not associated to any clock port. It may not work correctly.

前言 在Block design中引出AXI接口给外部,检查设计告警如下: [BD 41-968] AXI interface port /axi_lite4 is not associated to ...

- Verilog中变量位宽注意

Verilog中,变量定义方式可以为:reg[位宽-1:0] 数据名:reg[位宽:1] 数据名.其他变量也类似. 以reg变量cnt为例,当cnt位宽为4时,可定义为reg[3:0] cnt,或者定 ...

- C++中输出 位宽和小数点后位数 的控制

要用到这个头文件: <iomanip> setw(x) : 表示控制输出x的位宽 setprecision(x) :表示 控制输出小数点后 x 位 cout.precision(x): 表 ...

- 使用js方法将table表格中指定列指定行中相同内容的单元格进行合并操作。

前言 使用js方法对html中的table表格进行单元格的行列合并操作. 网上执行此操作的实例方法有很多,但根据实际业务的区别,大多不适用. 所以在网上各位大神写的方法的基础上进行了部分修改以适合自己 ...

- s3c2440裸机-内存控制器(二、不同位宽外设与CPU地址总线的连接)

不同位宽设备的连接 black 我们先看一下2440芯片手册上外设rom是如何与CPU地址总线连接的. 8bit rom与CPU地址线的连接 8bit*2 rom与CPU地址线的连接 8bit*4 r ...

- C语言-字、半字、内存位宽相关

1.32位系统:32位系统指的是32位数据线,但是一般地址线也是32位,这个地址线32位决定了内存地址只能有32位二进制,所以逻辑上的大小为2的32次方.内存限制就为4G.实际上32位系统中可用的内存 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 【设计经验】3、ISE中烧录QSPI Flash以及配置mcs文件的加载速度与传输位宽

一.软件与硬件平台 软件平台: 操作系统:Windows 7 64-bit 开发套件:ISE14.7 硬件平台: FPGA型号:XC6SLX45-CSG324 QSPI Flash型号:W25Q128 ...

- Vivado中备份设计好的block design

参考链接 https://blog.csdn.net/dimples_song/article/details/81391615 前言 为了不每次都重新生成block design,避免重复劳动. 可 ...

随机推荐

- java.sql.SQLException: Parameter index out of range (0 < 1 ).

向SQL中传入数据是从1开始的!!! 从ResultSet中取数据也是从1开始的!

- markdown常用方法

Markdown格式的普及流行要归功于Github和StackOverflow的流行,随着它们越来越流行,它们支持的Markdown格式也越来越流行. 1.优点 1.Markdown通过内容和样式相分 ...

- Linux系统管理----磁盘管理与文件系统

1.为主机新增两块30GB的SCSI硬盘 找到要添加的虚拟机,单击鼠标右键,点击设置 点击添加 选择硬件类型,然后点击下一步 选择要创建的磁盘类型,然后点击下一步 指定要创建磁盘的容量,然后点击下一步 ...

- poj 1205 :Water Treatment Plants (DP+高精度)

题意:有n个城市,它们由一个污水处理系统连接着,每个城市可以选择 1.将左边城市过来的污水和右边城市过来的污水连同本身的污水排到河里 >V< 2.将左边来的污水连同自己的污水排到右边 ...

- Guitar Pro如何更改五线谱的符杆方向

可能有的小伙伴不知道Guitar Pro是什么软件,我先稍微给大家介绍一下~ Guitar Pro是专为帮助所有吉他爱好者学习.绘谱.创作的多功能软件.它包含所有吉他的现有指法和音色,可以帮助我们了解 ...

- Selenium+java - 调用JavaScript操作

前言 在做web自动化时,有些情况selenium的api无法完成,需要通过第三方手段比如js来完成实现,比如去改变某些元素对象的属性或者进行一些特殊的操作,本文将来讲解怎样来调用JavaScript ...

- 9-1、大型项目的接口自动化实践记录----数据库结果、JSON对比

上一篇写了如何从DB获取预期.实际结果,这一篇分别对不同情况说下怎么进行对比. PS:这部分在JSON对比中也适用. 1.结果只有一张表,只有一条数据 数据格式:因为返回的是dicts_list的格式 ...

- 用html和css写一个头部header和左侧菜单栏menu-bar固定的的页面

这个页面header部分是100%的宽度,60px的高度,左侧是刚好一屏的高度,180的宽度,右侧的部分把剩余的空间占满,刚开始的时候还没怎么接触这样的页面,以为使用js读取浏览的可视化宽高,然后在做 ...

- react解析: render的FiberRoot(三)

react解析: render的FiberRoot(三) 感谢 yck: 剖析 React 源码解析,本篇文章是在读完他的文章的基础上,将他的文章进行拆解和加工,加入我自己的一下理解和例子,便于大家理 ...

- 新手的java学习建议

前言 进入IT领域,就像进入大海—浩瀚而广阔.然而,它又很容易让人迷茫,不知所措.所以,在IT的海洋中,找好一艘船特别重要,这艘船带你前进.减少迷失.这艘船或许是一个人,或一本书,又或许是一篇文章. ...