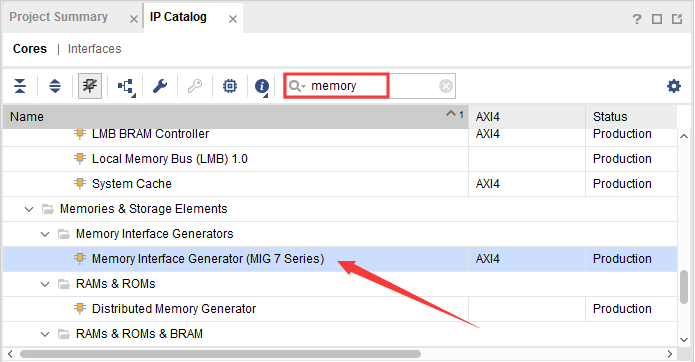

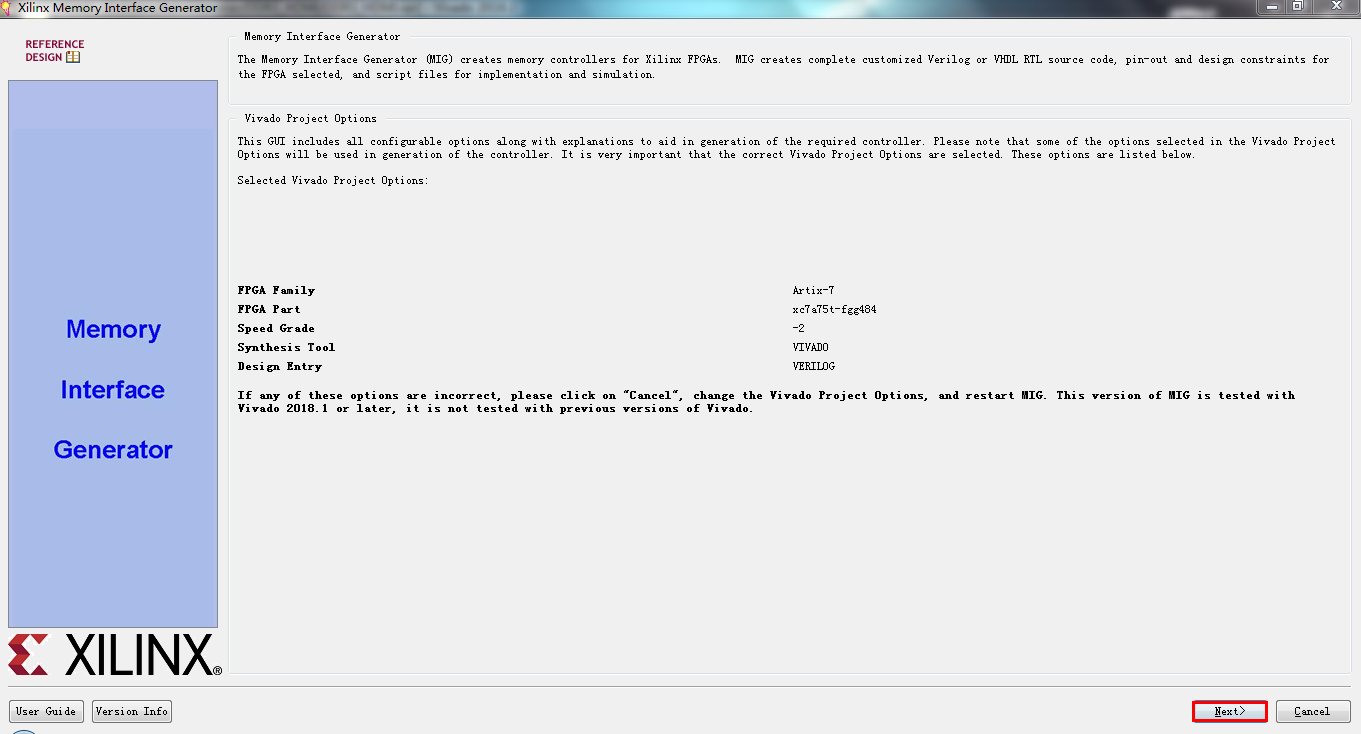

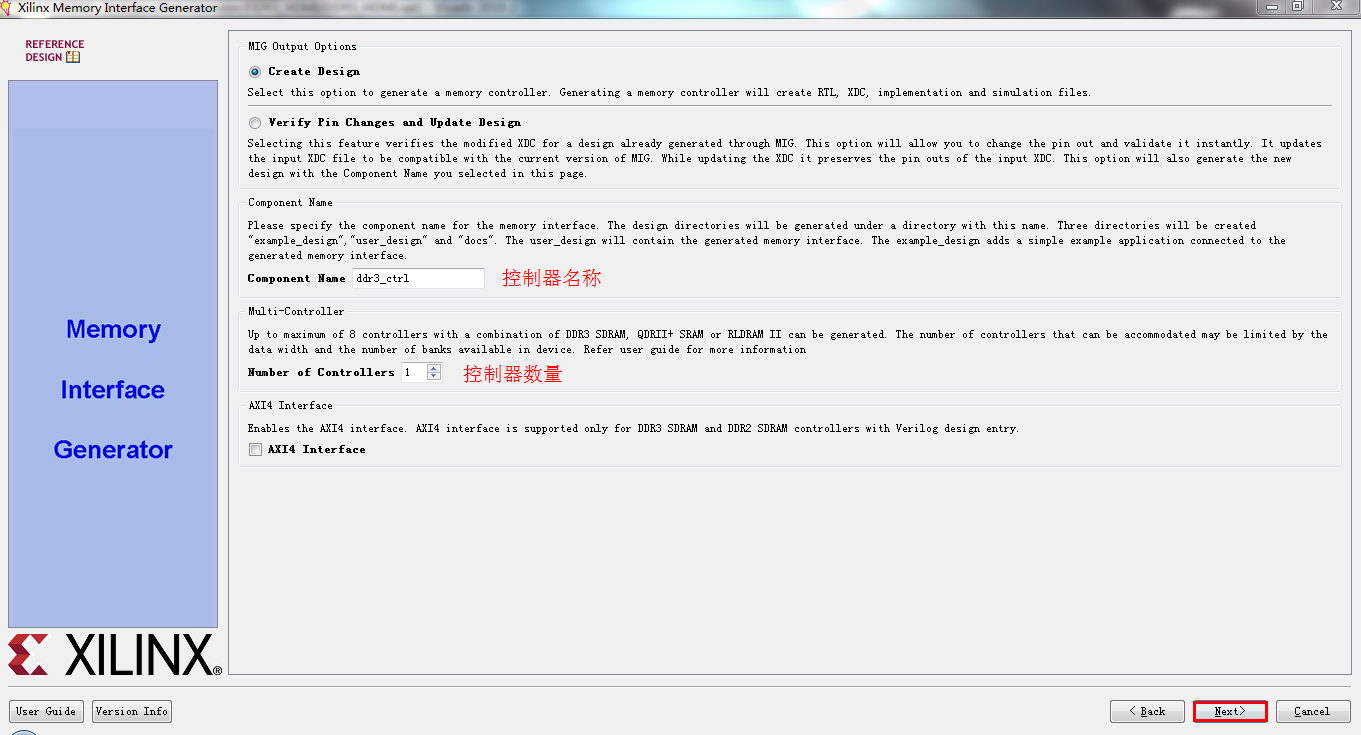

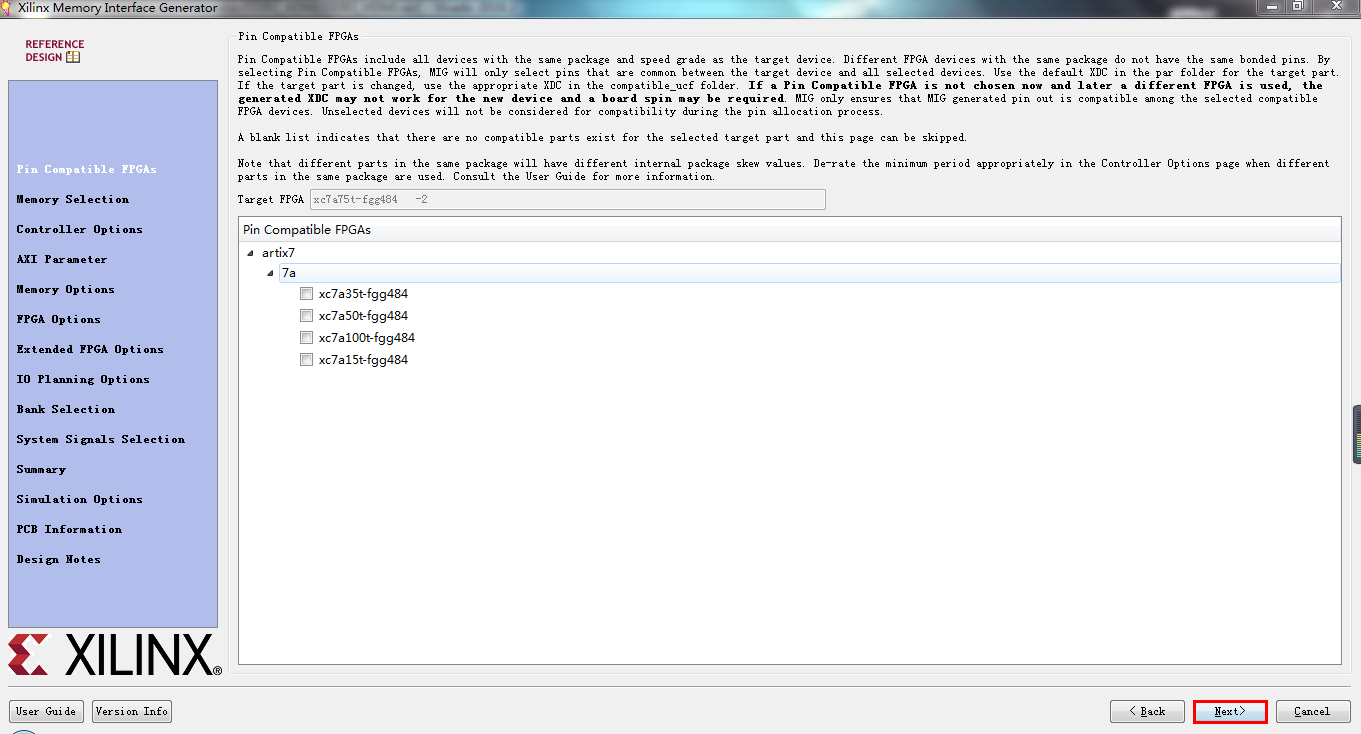

DDR3(1):IP核调取

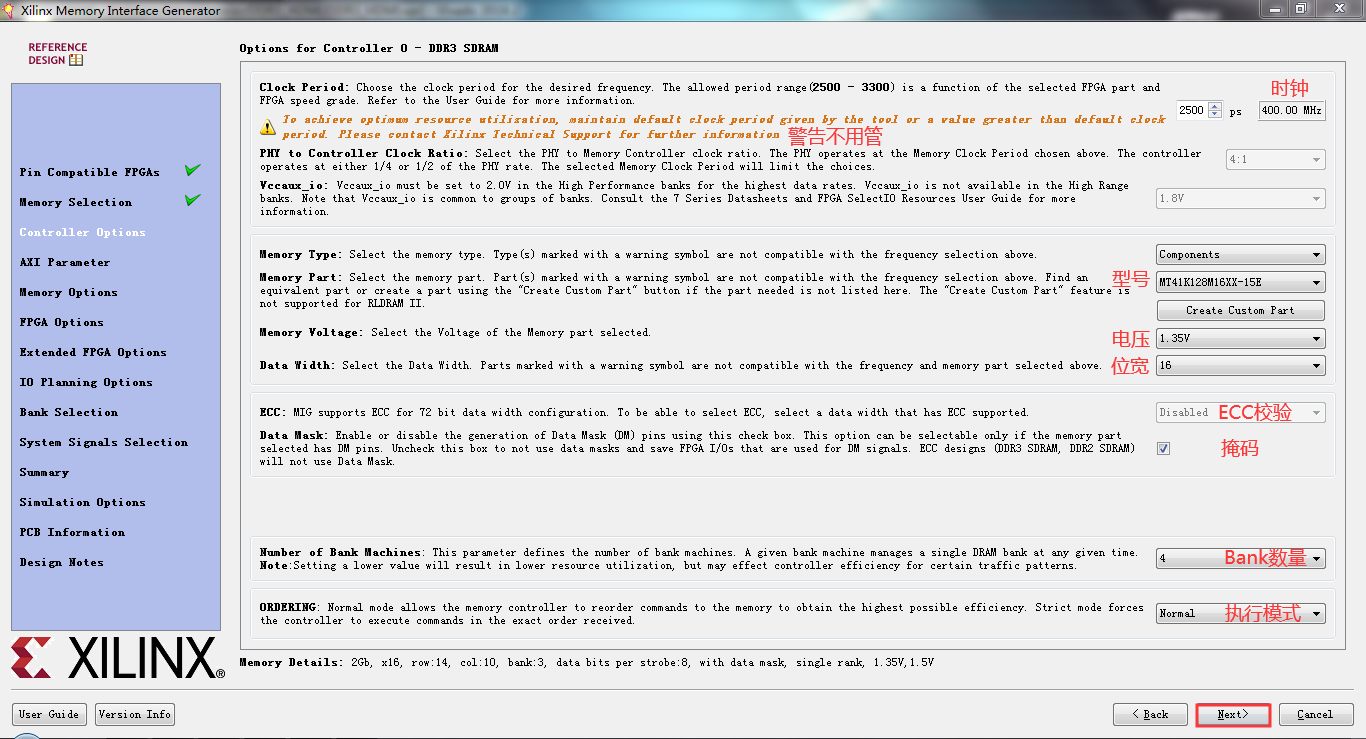

Clock Period : 给DDR3的同步的时钟,此时钟再产生DDR3的800M(400M时钟双沿传递),不用管warning,在此我们设置为 400MHz,若是 FPGA 芯片速度等级不同,则可能该工作频率的范围不一样

Memory Part : 选择 DDR3 SDRAM 的芯片类型,此处需要根据开发板上的芯片类型来选择,若是列表内没有相应的芯片类型,则可以在 Create Custom Part 中根据 DDR3 芯片参数来设定

DDR3的带宽计算 : 400 * 2 * 16 = 12.8 Gbps (400: 控制器 PHY 的时钟, 2: DDR 双沿采样, 16: 16bit,bus 的位宽。)

DDR3控制器是半双工模式(分时读写),平均分配的话每个操作占有 .4Gbps 的理论带宽,实际没有那么多,因为刷新、激活、读写指令等也都会占用周期。因此实际应用我们会*.8来考虑。

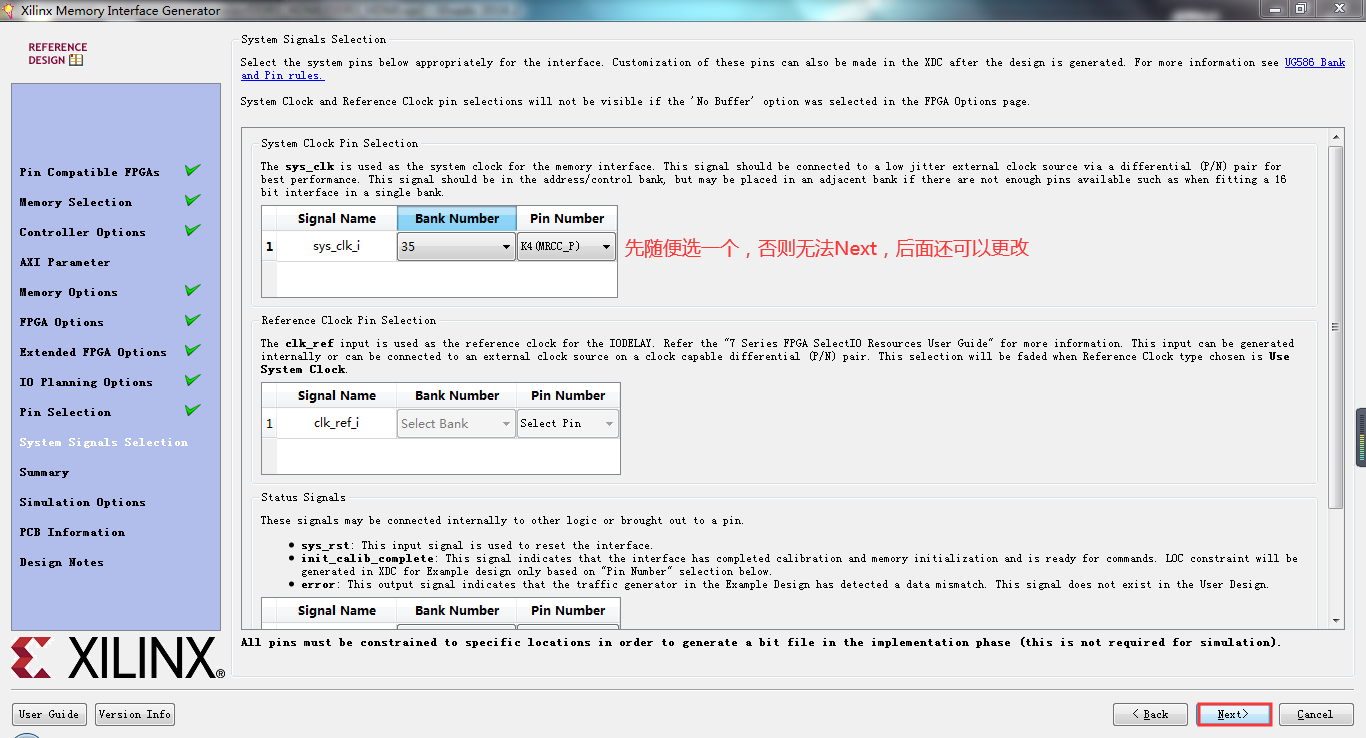

系统时钟

--------------------------------------------------------------------------

single_ended :来源于引脚的单端时钟

deferential :差分时钟

no buffer :来源于 FPGA 内部的时钟。 参考时钟

--------------------------------------------------------------------------

single_ended、deferential、no buffer,

use system clock:只有在 system clock 时钟频率为199MHZ~201MHz 时,才存在该选项。

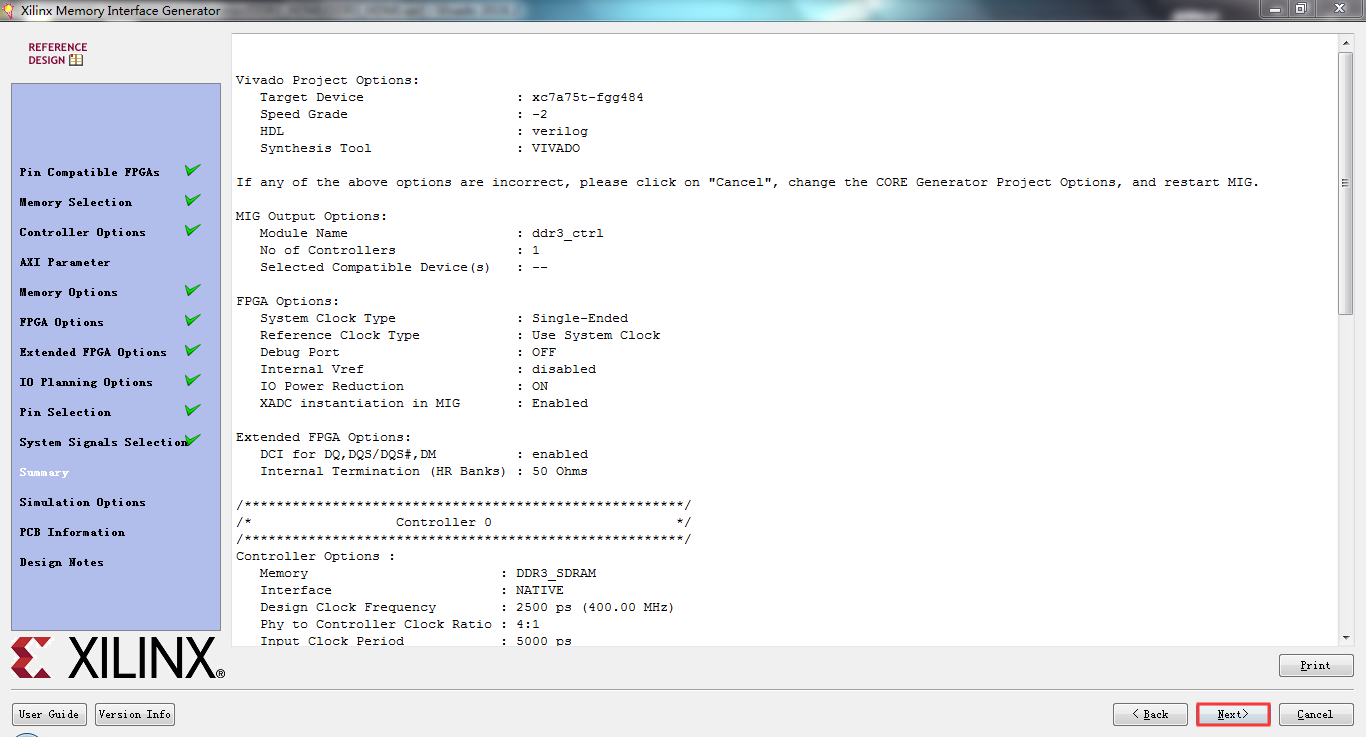

docs : 该IP核相关文档,如使用方法等。

example_design : 该IP核参考例程,仿真模型等。

user_design : 用户可使用的文件,如综合文件、约束文件。

DDR3(1):IP核调取的更多相关文章

- Xilinx DDR3 IP核使用问题汇总(持续更新)和感悟

一度因为DDR3的IP核使用而发狂. 后来因为解决问题,得一感悟.后面此贴会完整讲述ddr3 ip的使用.(XILINX K7) 感悟:对于有供应商支持的产品,遇到问题找官方的流程.按照官方的指导进行 ...

- Lattice 的 DDR IP核使用调试笔记之工程建立

DDR3的IP核的使用相当重要,尤其是对视频处理方面. 下面接收DDR3 的IP 核的生成步骤. 1. 选择DDR IP核的生成路径.名字以及哪种语言之后就可以设置DDR IP 的参数了. 2.选择存 ...

- 在使用FPGA来控制DDR3/DDR2 IP 的时候两个错误的解决办法

对于熟悉Intel FPGA的老(gong)司(cheng)机(shi)来说,外部存储器的控制早已是轻车熟路,但是对于新手,DDR3/DDR2 的IP使用也许并没有那么简单,不过没关系,骏龙的培训网站 ...

- 基于MIG IP核的DDR3控制器(一)

最近学习了DDR3控制器的使用,也用着DDR完成了一些简单工作,想着以后一段可能只用封装过后的IP核,可能会忘记DDR3控制器的一些内容,想着把这个DDR控制器的编写过程记录下来,便于我自己以后查看吧 ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

- Lattice 的 Framebuffer IP核使用调试笔记之datasheet笔记

本文由远航路上ing 原创,转载请标明出处. 学习使用以及调试Framebuffer IP 核已经有一段时间了,调试的时候总想记录些东西,可是忙的时候就没有时间来写,只有先找个地方记录下,以后再总结. ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- (转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)

原地址modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核) 1.打开D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\compxlibgui.e ...

随机推荐

- Java中assert(断言)的使用

Java中assert(断言)的使用 1.Eclipse中默认assert(断言)是关闭,开启方式如下: 简单来说:就是设置一下jvm的参数,参数是-enableassertions或者-ea(推荐) ...

- XSS靶场练习

0x00:前言 一个XSS练习平台,闯关形式,一共20关 0x01:开始 第一行都是代码插入点,下面几行是payloads(插入点和payloads中间空一行) LV1 <script>a ...

- xamarin Mqtt

1 什么是MQTT? mqtt (Message Queuing Telemetry Transport,消息队列遥测传输)是 IBM 开发的一个即时通讯协议,有可能成为物联网的重要组成部分.MQTT ...

- docker 网络模式 和 端口映射

docker 的 网络模式 docker 自带 3 种 网络模式:分别是bridge网络,host网络,none网络,可以使用 docker network ls 命令查看. 1.none网络 这 ...

- nfs—文件转换器

前端时间,在做一次设备升级时对nfs有了新的认识. nfs一般认为是文件共享服务器,但在实际的工作环境中,业务服务器有诸多限制,需要有加密隔离措施等等,版本升级和功能调试不同于平时的实验环境. 特别好 ...

- 201871010101-陈来弟《面向对象程序设计(java)》第二周学习总结

201871010101-陈来弟<面向对象程序设计(java)>第二周学习总结 项目 内容 这个作业属于哪个课程 <任课教师博客主页链接>https://www.cnblogs ...

- CentOS7 只下载安装包不安装

参考文档 yum安装本地rpm软件方案详解 https://www.jb51.net/article/132305.htm createrepo CentOS-Media.repo 本地软件源 --d ...

- 去掉VSS控制

1:删除.vssscc.vssver.scc .项目名.csproj.vspscc文件 2:.csproj文件删除以下内容 SccProjectName = "SAK" S ...

- jQuery对象和DOM对象转换,解决jQuery对象不能使用js方法的问题

有时候想要jQuery对象使用js方法,但是jQuery对象是什么js方法都不能用,怎么办呢?方法其实很简单,只要转换jQuery和DOM对象就可以了. 方法一: var $cr = $(" ...

- C# XML封装

/************************************************* * 描述: * * Author:yuanshuo@healthcare.cn * Date:20 ...