Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi、Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号。列表有:

| Xi | Yi | Cin | Sum | Cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

由左边表格可知:

Sum=X’Y'Cin+X'YCin'+XY'Cin'+XYCin=X'(Y⊕Cin)+X(Y⊙Cin)=X'(Y⊕Cin)+X(Y⊕Cin)'=X⊕Y⊕Cin

Cout=X’YCin+XYCin'+XY'Cin+XYCin=XY+(X⊕Y)Cin

如果取:P=X⊕Y ; G=XY

那么:Sum=P⊕Cin Cout=PCin+G

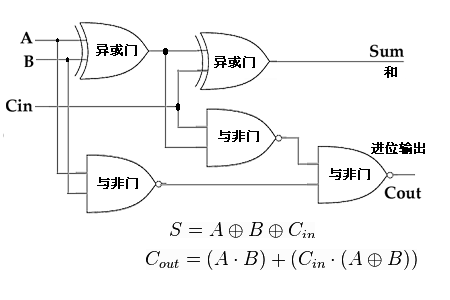

图中对Cout的公式进行了,即Cout'=(AB)'(PCin)'=(AB)'((A⊕B)Cin)'

下面是全加器的门级Verilog语言描述:

module Fadd(x,y,Cin,Cout,Sum);

input x,y,Cin;

output Cout,Sum;

wire a,b,c; xor xor1(a,x,y);

xor2(Sum,a,Cin);

and and1(b,x,y);

and2(c,Cin,a);

or or1(Cout,b,c); endmodule

全加器的行为描述:

module add(x,y,Cin,Sum,Cout);

input x,y,Cin;

output Sum,Cin;

assign Sum=x^y^Cin;

assign Cout=x&y+(x^y)&Cin;

endmodule

module add_N(x,y,Cin,Cout,Sum);

input x,y,Cin;

output Sum,Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

利用行为级描述的Verilog全加器可以很简单的扩展成4位或者16位等全加器:

module add_4(x,y,Cin,Cout,Sum);

input [:]x,y;

input Cin;

output [:]Sum;

output Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

module add_N(x,y,Cin,Cout,Sum);

input [N-:]x,y;

input Cin;

output [N-:]Sum;

output Cout;

assign {Cout,Sum}=x+y+Cin;

endmodule

Verilog学习笔记简单功能实现(二)...............全加器的更多相关文章

- Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义: 用16*8 RAM实现一个同步先进先出(FIFO)队列设计.由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出.写入和读出的操作(高电平有效)由时钟的上 ...

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- Verilog学习笔记简单功能实现(五)...............序列检测设计

这里采用夏宇闻教授第十五章的序列检测为例来学习; 从以上的状态转换图可以写出状态机的程序: module seqdet(x,out,clk,rst); input x,clk,rst; output ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog学习笔记简单功能实现(七)...............接口设计(并行输入串行输出)

利用状态机实现比较复杂的接口设计: 这是一个将并行数据转换为串行输出的变换器,利用双向总线输出.这是由EEPROM读写器的缩减得到的,首先对I2C总线特征介绍: I2C总线(inter integra ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- Verilog学习笔记简单功能实现(一)...............D触发器

module D_flop(data,clk,clr,q,qb); input data,clk,clr; output q,qb; wire a,b,c,d,e,f,ndata,nclk; nand ...

- Verilog学习笔记简单功能实现(八)...............异步FIFO

基本原理: 1.读写指针的工作原理 写指针:总是指向下一个将要被写入的单元,复位时,指向第1个单元(编号为0). 读指针:总是指向当前要被读出的数据,复位时,指向第1个单元(编号为0). ...

- Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第二十二章:四元数(QUATERNIONS)

原文:Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第二十二章:四元数(QUATERNIONS) 学习目标 回顾复数,以及 ...

随机推荐

- TroubleShooting笔记--快照进程sp_replupdateschema和索引重建发生冲突

今天早上服务器出现大面积的阻塞,上去排查blocking,最后大概确定的问题是: rebuild index job(243) --->blocked--->sp_replupdatesc ...

- Chrome插件整理

本文内容都来源于偶整理的fetool. 想让更多使用Chrome的小伙伴,体验到这些令人愉悦的小工具,所以单独整理了这篇文章. 如果你是 前端/服务端/设计/面向Github编程/视觉控,相信下列的插 ...

- SQL Server 2012 Managed Service Account

原创地址:http://www.cnblogs.com/jfzhu/p/4007472.html 转载请注明出处 (一)Windows服务使用的登陆帐号 Windows服务只有登录到某一帐户的情况下才 ...

- Maven常用插件

maven利用各种插件来管理构建项目,本文记录下工作中常用到的插件及使用方法.每个插件都会提供多个目标(goal),用于标示任务.各插件配置在pom.xml里,如下: <build> [. ...

- 我也来说说DDD~大话目录

回到占占推荐博客索引 DDD之前没有接触过,但一但有了接触就一发不可收拾,他会带去进入一个全新的世界! DDD不是新技术,而是新思想,新模式,是软件开发领域的一次突破,它更接近于业务,对于业务的改动它 ...

- ASP.NET Core - ASP.NET Core MVC 的功能划分

概述 大型 Web 应用比小型 Web 应用需要更好的组织.在大型应用中,ASP.NET MVC(和 Core MVC)所用的默认组织结构开始成为你的负累.你可以使用两种简单的技术来更新组织方法并及时 ...

- easyuidatagrid中load,reload,loadData的区别

摘要:datagrid中有load,reload,loadData那三个方式,皆是加载数据的,但又有差别.下面让我们一起来看看: 首先,load方法,比如我已经定义一个datagrid的id为grid ...

- EasyUI DateTimeBox设置默认时间的注意点

- ExtJs4 基础必备

认识ExtJs的开发包 下载路径:http://www.sencha.com/products/extjs/download/ 解压有20多兆,别怕,真正运行的没这么大.认识下这个包的文件结构吧. b ...

- centos6.5 下搭建lamp环境

一直以为很麻烦,实际操作起来并没有遇到什么问题,yum源是163,php版本是5.3(有点老,以后再更新吧):详细步骤如下: 第一步:安装php mysql apache yum -y install ...