操作系统-存储管理(3)高速缓存Cache

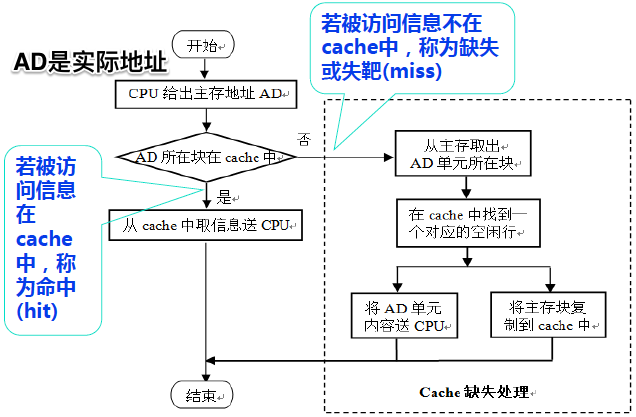

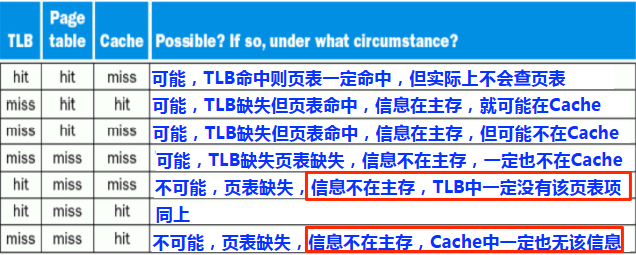

- 联想存储器:根据内容进行寻址的存储器(冯氏模型中是按照地址进行寻址,但在高速存储器中往往只存有部分信息,此时需要根据内容进行检索)

- 地址转换部件:通过联想存储器建立目录表以实现快速地址转换。命中时直接访问Cache;未命中时从内存读取放入Cache

- 替换部件:在缓存已满时按一定策略进行数据块替换,并修改地址转换部件

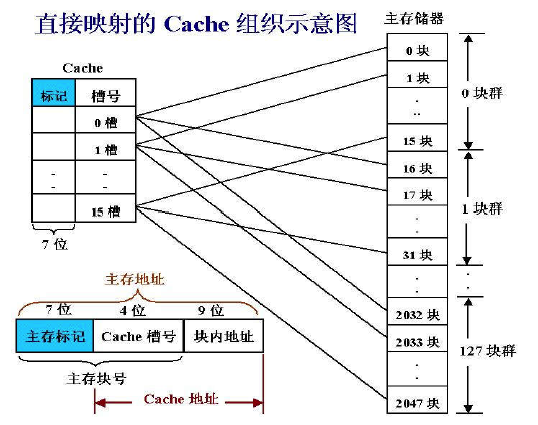

- 直接(Direct)映射/模映射:每个主存块映射到Cache的固定行

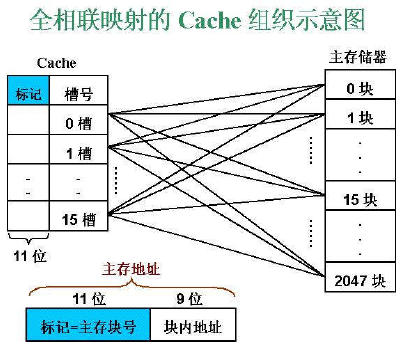

- 全相联(Full Associate):每个主存块映射到Cache的任一行

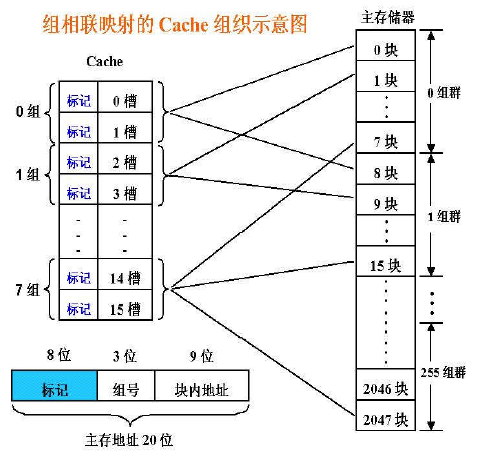

- 组相联(Set Associate):每个主存块映射到Cache固定组中任

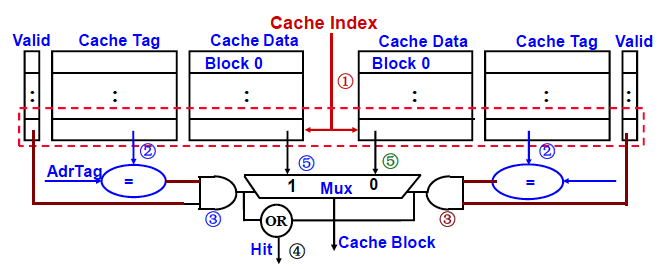

- Cache Index 选择其中的一个Cache行集合(共2行)

- 对这个集合中的两个Cache行的Tag并行进行比较

- 根据比较结果确定信息在哪个行,或不在Cache中

| 可能的位置 | 关联度 | 缺失率 | 命中时间 | tag位数 | |

| 直接映射 | 唯一映射 | 最低,为1 | 最高 | 最小 | 最小 |

| 全相联映射 | 任意映射 | 最高,为Cache行数 | 最低(关联度越高命中率越高) | 最大 | 标记=主存块号 |

| N-路组相联映射 | N-路映射 | 居中,为N | 路数翻倍,增加1位 |

- 先进先出FIFO (first-in-first-out)

- 最近最少用LRU ( least-recently used)

- 每组4行时,计数器有2位。计数值越小则说明越被常用。命中时,被访问行的计数器置0,比其低的计数器加1,其余不变。

- 未命中且该组未满时,新行计数器置为0,其余全加1。

- 未命中且该组已满时,计数值为3的那一行中的主存块被淘汰,新行计数器置为0,其余加1。

- 最不经常用LFU ( least-frequently used)

- 随机替换算法(Random)

- 因为Cache中的内容是主存块副本,当对Cache中的内容进行更新时,就存在Cache和主存如何保持一致的问题。

- 当多个设备都允许访问主存时。I/O设备可直接读写内存时,如果Cache中的内容被修改,则I/O设备读出的对应主存单元的内容无效;若I/O设备修改了主存单元的内容,则Cache中对应的内容无效。

- 当多个CPU都带有各自的Cache而共享主存时。某个CPU修改了自身Cache中的内容,则对应的主存单元和其他CPU中对应的内容都变为无效。

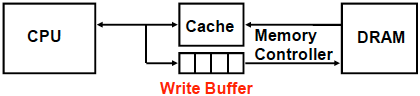

- 全写法Write Through(通写法、写直达法、直写法):

- 回写法Write Back(一次性写方式、写回法):只写cache不写主存,缺失时一次写回,每行有个修改位dirty bit脏位,大大降低主存带宽需求,控制可能很复杂

操作系统-存储管理(3)高速缓存Cache的更多相关文章

- 再说Postgres中的高速缓存(cache)

表的模式信息存放在系统表中,因此要访问表,就需要首先在系统表中取得表的模式信息.对于一个PostgreSQL系统来说,对于系统表和普通表模式的访问是非常频繁的.为了提高这些访问的效率,PostgreS ...

- 操作系统-存储管理(6)buffer/cache/swap

为了提高文件系统性能,内核利用一部分物理内存分配出缓冲区,用于缓存系统操作和数据文件,当内核收到读写的请求时,内核先去缓存区找是否有请求的数据,有就直接返回,如果没有则通过驱动程序直接操作磁盘. 缓存 ...

- 细说Oracle数据库与操作系统存储管理二三事

在上大学的时候,学习操作系统感觉特别枯燥,都是些条条框框的知识点,感觉和实际应用的关联不大.发现越是工作以后,在工作中越想深入了解,发现操作系统知识越发重要.在实践中结合理论还是不错的一种学习方法.自 ...

- 操作系统-存储管理(5)IA-32/Linux的地址转换

IA-32/Linux按字节编址:在保护模式下,IA-32采用段页式虚拟存储管理方式,存储地址采用逻辑地址.线性地址和物理地址来进行描述. 逻辑地址由48位组成,包含16位段选择符(高13位为段表项的 ...

- linux查看CPU高速缓存(cache)信息

一.Linux下查看CPU Cache级数,每级大小 dmesg | grep cache 实例结果如下: 二.查看Cache的关联方式 在 /sys/devices/system/cpu/中查看相应 ...

- 操作系统之cache、伙伴系统、内存碎片、段式页式存储管理

存储管理是操作系统非常重要的功能之一,本文主要介绍操作系统存储管理的基础知识,包括缓存相关知识.连续内存分配.伙伴系统.非连续内存分配.内存碎片等,并结合linux系统对这些知识进行简单的验证.文章内 ...

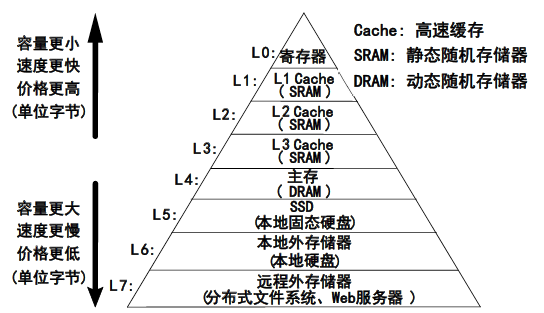

- 寄存器,cache、伙伴系统、内存碎片、段式页式存储管理

cache.伙伴系统.内存碎片.段式页式存储管理 目录 分层的存储管理 cache 局部性原理 置换算法 写回策略 linux环境下的cache 连续内存分配与内存碎片 内部碎片与外部碎片 动态分区分 ...

- 深入解析Windows操作系统笔记——CH2系统结构

2.系统结构 本章主要介绍系统的总体结构,关键部件之间的交互,以及运行在什么环境. 2.系统结构 2.1 需求和设计目标 2.2 操作系统模型 2.3 总体结构 2.3.1 可移植性 2.3.2 对称 ...

- (转)CPU Cache与内存对齐

转自:http://blog.csdn.net/zhang_shuai_2011/article/details/38119657 原文如下: 一. CacheCache一般来说,需要关心以下几个方面 ...

随机推荐

- Redis 和 memcache 简单比较

1.Redis不仅仅支持简单的key-value类型的数据,同时还提供list.set.zset.hash等数据结构的存储. 2.Redis支持master-slave(主--从)模式应用. 3.Re ...

- Python List min()方法

描述 min() 方法返回列表元素中的最小值.高佣联盟 www.cgewang.com 语法 min()方法语法: min(list) 参数 list -- 要返回最小值的列表. 返回值 返回列表元素 ...

- 每日一道 LeetCode (3):回文数

前文合集 每日一道 LeetCode 文章合集 题目:回文数 题目来源:https://leetcode-cn.com/problems/palindrome-number/ 判断一个整数是否是回文数 ...

- C#与网络相关的两个监听的事件

今天遇到一个问题,当网络连接有问题的时候设计软件向用户发送通知,查了资料发现了两个相关的事件分享一下. 一.System.Net.NetworkInformation命名空间下的NetworkChan ...

- Selenium多窗口切换代码

# #!/usr/bin/python3 # -*- coding: utf-8 -*- # @Time : 2020/7/31 16:05 # @Author : Gengwu # @FileNam ...

- JSON 和 POJO 互转,List<T> 和 JSON 互转

JSON 和 POJO import com.alibaba.fastjson.JSONObject; import org.slf4j.Logger; import org.slf4j.Logger ...

- ios wkwebview didReceiveAuthenticationChallenge crash解决

//需要响应身份验证时调用 同样在block中需要传入用户身份凭证 //现在就是不进行https验证了 然后就闪退不了了 - (void)webView:(WKWebView *)webView di ...

- Maven骨架生成项目速度慢问题解决办法

在创建maven project时(使用了archetype),速度慢的令人不敢相信,从Idea的控制台可以看到信息停留在: [INFO] <<< maven-archetype-p ...

- 秦九韶算法 & 三分法

前言 今天考试出了一个题 郭郭模拟退火骗了75分 于是再次把咕咕了好久的模退提上日程 如果进展顺利 明后天应该会开爬山算法和模退的博客笔记 今天先把今天考试的正解学习一下--三分法 引入 老规矩上板子 ...

- Eclipse工具的简单使用

前言 虽然编写Java用Idea比较好,但是对于正处于大学阶段的我,还是要和老师的步伐保持一致,但是,用的Idea这个工具多了,我就感觉对eclipse这个工具不是怎么熟悉了,甚至还有点对一些工具的使 ...