Verilog-异步FIFO

参考博文:https://blog.csdn.net/alangaixiaoxiao/article/details/81432144

1、概述

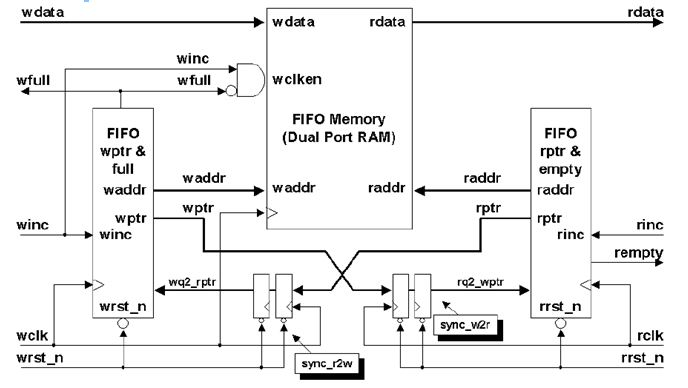

异步FIFO设计的关键是产生“写满”和“读空”信号,这两个信号的产生需要用到读指针rptr和写指针wptr构建组合逻辑进行判断,然而读指针属于读时钟域rclk,写指针属于写时钟域wclk,因此必须进行同步化处理以消除亚稳态。异步FIFO的设计一般采用2种手段进行同步化处理:

(1)将读指针rptr打2拍到写时钟域,将写指针wptr打两拍到读时钟域,消除亚稳态;

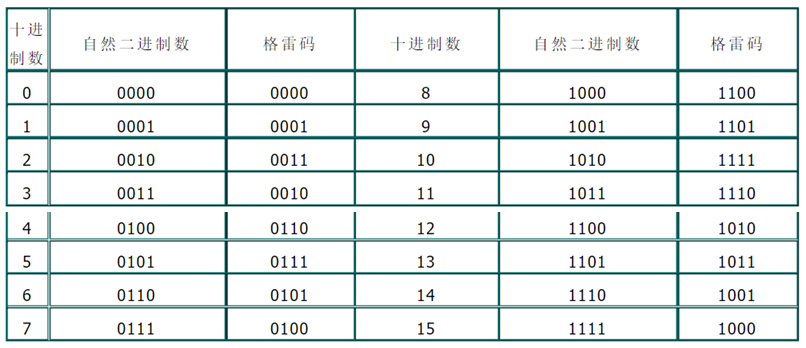

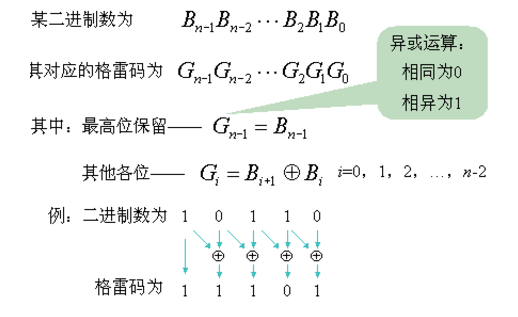

(2)由于读写指针都是多比特信号,直接对它们进行同步化容易产生亚稳态,且用组合逻辑进行判断容易产生毛刺,因此改用格雷码进行异步时钟域的传输。

2、代码

设计思路有以下几点:

(1)在指针中添加一个额外的位(extra bit),当写指针增加并越过最后一个FIFO地址时,就将写指针这个未用的MSB加1,其它位回零。对读指针也进行同样的操作。此时,对于深度为2^n的FIFO,需要的读/写指针位宽为(n+1)位,如对于深度为8的FIFO,需要采用4bit的计数器,0000~0111、1000~1111,MSB作为折回标志位,而低3位作为地址指针。如果两个指针的MSB不同,说明写指针比读指针多折回了一次;如r_addr=0000,而w_addr = 1000,为满。如果两个指针完全相同,为空。

(2)使用gray码解决了一个问题,但同时也带来另一个问题,即在格雷码域如何判断空与满。空的判断标准仍是完全相同,满的判断标准需要满足:

■ 格雷码指针的最高位不同,因为wptr必须比rptr多折回一次。

■ wptr与rptr的次高位不相等,如下表的7(格雷码为0100)和15(格雷码为1000),转化为二进制对应的是0111和1111,MSB不同说明多折回一次,111相同代表同一位置。

■ 其余位完全相同

(3)对双口RAM的寻址采用二进制码,异步时钟域的交互采用格雷码。

`timescale 1ns / 1ps module asynchronous_fifo

#(parameter ASIZE=,DSIZE=)

(

// 读

input rclk,

input rrst_n,

input rinc,

output [DSIZE-:] rdata,

output rempty,

// 写

input wclk,

input wrst_n,

input winc,

input [DSIZE-:] wdata,

output wfull

); // 读写地址,由wbin、rbin的低位生成

wire [ASIZE-:] waddr,raddr;

reg [ASIZE:] wbin,rbin;

// 读写指针(比地址位宽大1)

reg [ASIZE:] wgray,rgray;

wire [ASIZE:] wbinnext,wgraynext,rbinnext,rgraynext;

// 经打拍后的读写指针

reg [ASIZE:] rq1_wgray,rq2_wgray,wq1_rgray,wq2_rgray; reg rempty_val,wfull_val; // 双端口存储器

reg [DSIZE-:] mem [:(<<ASIZE)-];

reg [DSIZE-:] rdata_reg;

//assign rdata = mem[raddr];

always @(posedge wclk) begin

if(!wfull && winc) mem[waddr] <= wdata;

end

always @(posedge rclk or negedge rrst_n) begin

if(!rrst_n) rdata_reg <= ;

else if(!rempty && rinc) rdata_reg <= mem[raddr];

else rdata_reg <= {DSIZE{'bz}}; // 设成z态方便看波形

end

assign rdata = rdata_reg; // 同步化处理

always @(posedge rclk or negedge rrst_n)begin

if(!rrst_n) {rq1_wgray,rq2_wgray} <= ;

else {rq1_wgray,rq2_wgray} <= {wgray,rq1_wgray};

end always @(posedge wclk or negedge wrst_n) begin

if(!wrst_n) {wq1_rgray,wq2_rgray} <= ;

else {wq1_rgray,wq2_rgray} <= {rgray,wq1_rgray};

end // 写地址和写满信号产生

always @(posedge wclk or negedge wrst_n) begin

if(!wrst_n) {wbin,wgray} <= ;

else {wbin,wgray} <= {wbinnext,wgraynext};

end

assign wbinnext = (~wfull & winc)? (wbin+'b1) : wbin;

assign waddr = wbin[ASIZE-:];

assign wgraynext = (wbinnext>>)^wbinnext; always @(posedge wclk or negedge wrst_n) begin

if(!wrst_n) wfull_val <= ; // 用同步到写时钟域的读指针与写指针进行比较,高两位不同其他位相同则满

else wfull_val <= (wgraynext=={~wq2_rgray[ASIZE:ASIZE-],wq2_rgray[ASIZE-:]});

end

assign wfull = wfull_val; // 读地址和读空信号

always @(posedge rclk or negedge rrst_n) begin

if(!rrst_n) {rbin,rgray} <= ;

else {rbin,rgray} <= {rbinnext,rgraynext};

end

assign rbinnext = (~rempty & rinc)? (rbin+'b1) : rbin;

assign raddr = rbin[ASIZE-:];

assign rgraynext = (rbinnext >> ) ^ rbinnext; always @(posedge rclk or negedge rrst_n) begin

if(!rrst_n) rempty_val <= ; // 用同步到读时钟域的写指针与读指针进行比较,各位都相同则满

else rempty_val <= (rgraynext==rq2_wgray);

end

assign rempty = rempty_val; endmodule

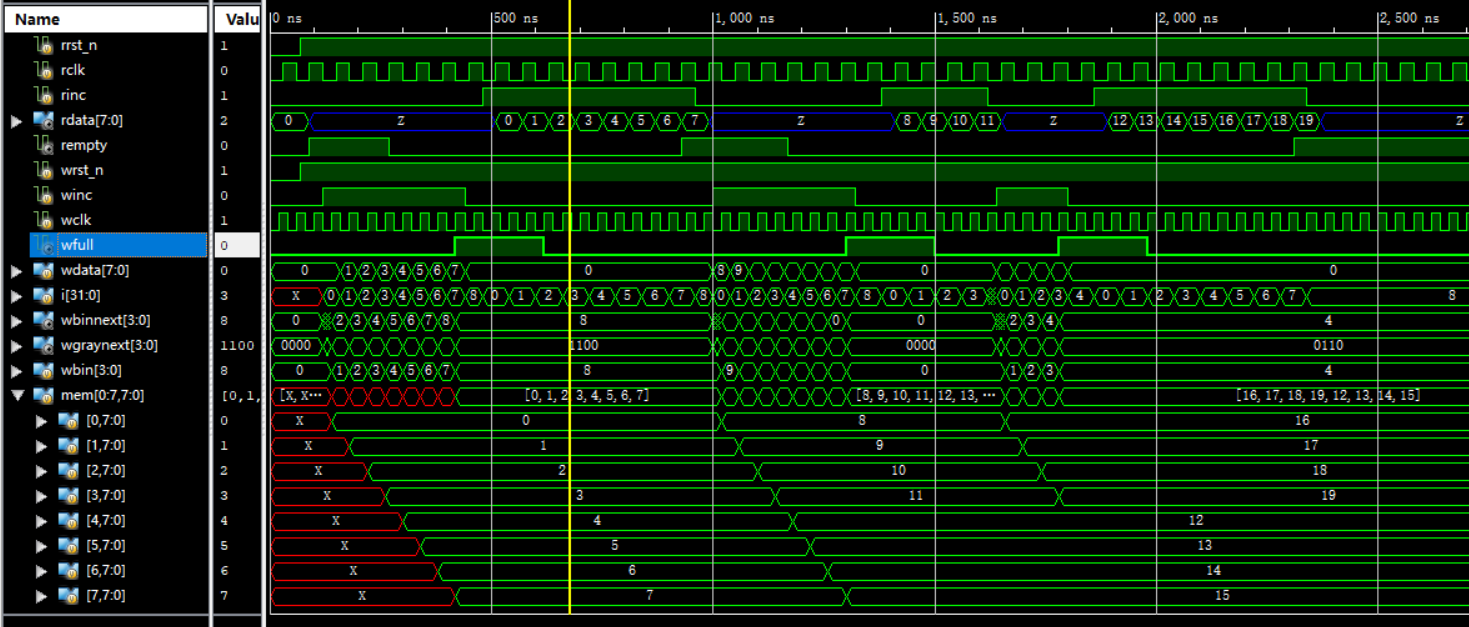

3、验证

(1)testbench

写8个数据(0-7)——触发wfull信号——读8个数据(0-7)——触发rempty信号——写8个数据(8-15)——触发wfull信号——读4个数据(8-11)——写4个数据(16-19)——触发wfull信号——读8个数据(12-19)——触发rempty信号

`timescale 1ns / 1ps

module asynchronous_fifo_tb;

// Inputs

reg rclk;

reg rrst_n;

reg rinc;

reg wclk;

reg wrst_n;

reg winc;

reg [:] wdata;

// Outputs

wire [:] rdata;

wire rempty;

wire wfull;

integer i;

// Instantiate the Unit Under Test (UUT)

asynchronous_fifo uut (

.rclk(rclk),

.rrst_n(rrst_n),

.rinc(rinc),

.rdata(rdata),

.rempty(rempty),

.wclk(wclk),

.wrst_n(wrst_n),

.winc(winc),

.wdata(wdata),

.wfull(wfull)

);

initial begin

// Initialize Inputs

rclk = ;

rrst_n = ;

rinc = ;

wclk = ;

wrst_n = ;

winc = ;

wdata = ;

// Wait 100 ns for global reset to finish

#;

rrst_n = ;

wrst_n = ;

@(negedge rclk);

// Write

for(i=;i<;i=i+) begin

wdata = i;

winc = ;

@(negedge wclk);

end

winc = ; //写满

wdata = ;

//Read

@(negedge rclk);

for(i=;i<;i=i+) begin

rinc = ;

@(negedge rclk);

end

rinc = ; //读空

// Write

@(negedge wclk);

for(i=;i<;i=i+) begin

wdata = i+;

winc = ;

@(negedge wclk);

end

winc = ;

wdata = ; // 写满

//Read

@(negedge rclk);

for(i=;i<;i=i+) begin

rinc = ;

@(negedge rclk);

end

rinc = ; // 读一半

// Write

@(negedge wclk);

for(i=;i<;i=i+) begin

wdata = i+;

winc = ;

@(negedge wclk);

end

winc = ;

wdata = ; // 写一半

//Read

@(negedge rclk);

for(i=;i<;i=i+) begin

rinc = ;

@(negedge rclk);

end

rinc = ; //读空

// Add stimulus here

end

always # wclk = ~wclk;

always # rclk = ~rclk;

endmodule

(2)读空信号(rempty)存在几个周期的置0延迟,即在空状态写,写入数据后rempty不会立即置0,而是会经过几个周期以后才会置0,这跟跨异步时钟域的打拍有关,因为写指针需要2个周期才能同步到读时钟域与读指针进行比较。rempty在读状态下的置1不存在延迟,因为当前同步到读时钟域的写指针已经是最新的了,读指针的变化立即就可以触发置1,置0延迟置1不延迟对于实际使用是没有太大影响的,反之则有。同样写满信号(wfull)的置0也存在延迟。

Verilog-异步FIFO的更多相关文章

- 同步fifo与异步fifo

参考以下帖子: https://blog.csdn.net/hengzo/article/details/49683707 https://blog.csdn.net/Times_poem/artic ...

- 异步fifo的Verilog实现

一.分析 由于是异步FIFO的设计,读写时钟不一样,在产生读空信号和写满信号时,会涉及到跨时钟域的问题,如何解决? 跨时钟域的问题:由于读指针是属于读时钟域的,写指针是属于写时钟域的,而异步FIFO ...

- 异步FIFO总结+Verilog实现

异步FIFO简介 异步FIFO(First In First Out)可以很好解决多比特数据跨时钟域的数据传输与同步问题.异步FIFO的作用就像一个蓄水池,用于调节上下游水量. FIFO FIFO是一 ...

- 异步FIFO的verilog实现与简单验证(调试成功)

最近在写一个异步FIFO的时候,从网上找了许多资料,文章都写的相当不错,只是附在后面的代码都多多少少有些小错误. 于是自己写了一个调试成功的代码,放上来供大家参考. 非原创 原理参考下面: 原文 ht ...

- 怎么用Verilog语言描述同步FIFO和异步FIFO

感谢 知乎龚大佬 打杂大佬 网上几个nice的博客(忘了是哪个了....) 前言 虽然FIFO都有IP可以使用,但理解原理还是自己写一个来得透彻. 什么是FIFO? Fist in first out ...

- Verilog设计异步FIFO

转自http://ninghechuan.com 异步FIFO有两个异步时钟,一个端口写入数据,一个端口读出数据.通常被用于数据的跨时钟域的传输. 同步FIFO的设计.一个时钟控制一个计数器,计数器增 ...

- 异步FIFO及verilog原码

这几天看了Clifford E. Cummings的两篇大作<Simulation and Synthesis Techniques for Asynchronous FIFO Design&g ...

- 异步fifo的设计

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一.FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo深度(简单来说就是需要存多少个数据) ...

- 基于FPGA的异步FIFO设计

今天要介绍的异步FIFO,可以有不同的读写时钟,即不同的时钟域.由于异步FIFO没有外部地址端口,因此内部采用读写指针并顺序读写,即先写进FIFO的数据先读取(简称先进先出).这里的读写指针是异步的, ...

- 异步fifo的设计(FPGA)

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一.FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo深度(简单来说就是需要存多少个数据) ...

随机推荐

- python3-cookbook笔记:第八章 类与对象

python3-cookbook中每个小节以问题.解决方案和讨论三个部分探讨了Python3在某类问题中的最优解决方式,或者说是探讨Python3本身的数据结构.函数.类等特性在某类问题上如何更好地使 ...

- 苹果Mac电脑永久路由的添加 & Mac 校园网连接教程

学校校园网面向全校师生开放,无奈Windows用户基数大,学校只为Windows平台制作了内网连接工具,Mac平台资源较少,本人查阅相关资料后,总结整理出以下步骤,方便本校学生连接校园网.有永久路由添 ...

- linux文件、文件夹操作

1. pwd 查看当前所在的路径 2. ls 显示文件列表 ls -l 显示文件列表以及详情 ls -la 显示所有文件列表以及详情(包含隐藏文件) 注意:ls -l 相当于ll 例如 ...

- UESTC 1324 卿学姐与公主 分块板子

#include<iostream> #include<cmath> using namespace std; ; //表示当前数在哪一块里面 int belong[maxn] ...

- Qt的QString,QByteArray,char *相互转换

1.QString转换为QByteArray QString str = "; QByteArray byte = str.toUtf8(); // 转换为Utf8格式 byte.toLoc ...

- H5网页布局+css代码美化

HTML5的结构化标签,对搜索引擎更友好 li 标签对不利于搜索引擎的收录,尽量少用 banner图片一般拥有版权,不需要搜索引擎收录,因此可以使用ul + li <samp></s ...

- 纪中9日T4 2298. 异或

2298. 异或 (File IO): input:gcdxor.in output:gcdxor.out 时间限制: 1000 ms 空间限制: 262144 KB 具体限制 题目描述 Sarv ...

- Qt读写文件

1.头文件 #include<QFile> #include<QFileDialog> #include<QDataStream> 2.写代码前工作 在ui界面拖入 ...

- 使用IDA pro逆向ARM M系核心的Bin固件

使用IDA pro逆向ARM M系核心的Bin固件 物联网和智能设备这两年还是比较火的,我们的手中或多或少都有了几个智能设备,比如手环,智能手表,或者门锁什么之类的东西,但是同学们在做逆向的时候, ...

- 超级丑数--用查找的api解决

质数又称素数.一个大于1的自然数,除了1和它自身外,不能被其他自然数整除的数叫做质数:否则称为合数. 质因数(素因数或质因子)在数论里是指能整除给定正整数的质数.除了1以外,两个没有其他共同质因子的正 ...