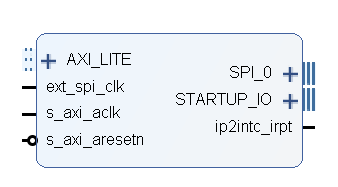

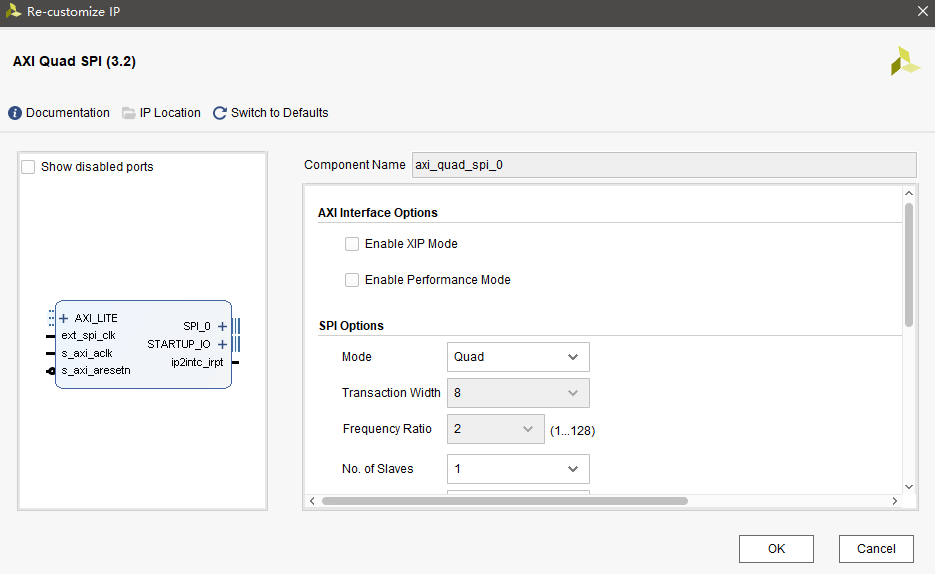

关于AXI_Quad_SPI的寄存器配置

关于AXI_Quad_SPI的寄存器配置

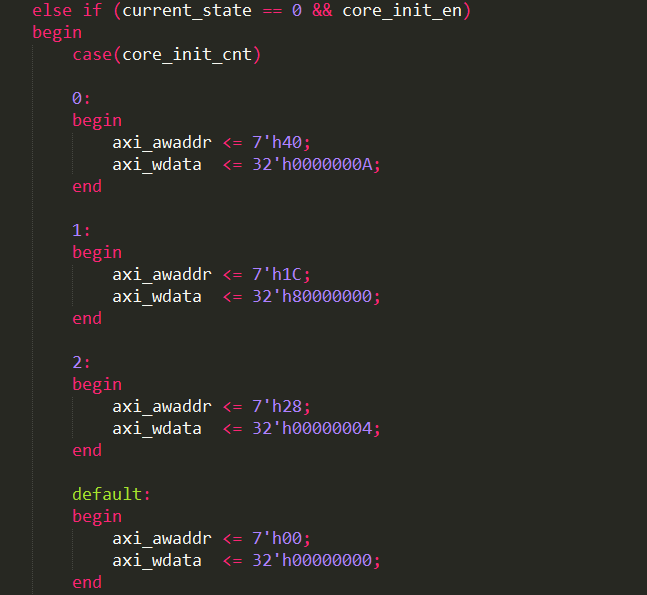

1.核初始化配置

首先是:

40:0000_000A

1C:8000_0000

28:0000_0004

2.命令与dummy_data

60:000001E6

60:00000186

68:{24'h000000,cmd}

68:{24'h000000,add0}

68:{24'h000000,add1}

68:{24'h000000,add2}

68:{24'h000000,data1}

68:{24'h000000,data2}

68:{24'h000000,data3}

68:{24'h000000,DUMMY_DATA}

68:{24'h000000,DUMMY_DATA}

68:{24'h000000,DUMMY_DATA}

68:{24'h000000,DUMMY_DATA}

68:{24'h000000,DUMMY_DATA}

68:{24'h000000,DUMMY_DATA}

68:{24'h000000,DUMMY_DATA}

68:{24'h000000,DUMMY_DATA}

70:00000000

60:00000086

20:00000004

70:FFFFFFFF

60:00000186

AXI_Quad_SPI核在使用中碰到的问题:

对IP核进行初始化后,执行的第一个命令无效,第二个命令才能正常执行,如果开机第一个命令需要执行写使能命令,即需要把写使能命令执行两边,第二个才生效,第三个,第四个...均能正常执行。这个问题与SPI的clk 调用了startup primitive这一源语有关。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/02/01 10:32:30

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module top( input clk_27m_in,

inout [:]spi_dq,

inout spi_ss ); //--------------------------------------------------------------

wire clk_100M;

clk_wiz_0 U2(

.clk_out1(clk_100M),

.clk_in1(clk_27m_in)

); //--------------------------------------------------------------

wire rst;

//wire start_write;

wire start_core_init;

wire finish_core_init;

wire start_core_write;

wire wait_core_int;

wire finish_core_write;

wire start_read;

wire [:]axi_araddr;

wire core_init_en;

wire core_write_en;

wire [:]cmd;

wire [:]add0;

wire [:]add1;

wire [:]add2;

wire [:]data1;

wire [:]data2;

wire [:]data3;

vio_0 U3 (

.clk(clk_100M), // input wire clk

.probe_out0(rst), // output wire [0 : 0] probe_out0

.probe_out1(start_core_init), // output wire [0 : 0] probe_out1

.probe_out2(start_read), // output wire [0 : 0] probe_out2

.probe_out3(axi_araddr), // output wire [31 : 0] probe_out3

.probe_out4(core_init_en), // output wire [0 : 0] probe_out4

.probe_out5(core_write_en), // output wire [0 : 0] probe_out5

.probe_out6(cmd), // output wire [7 : 0] probe_out6

.probe_out7(add0), // output wire [7 : 0] probe_out7

.probe_out8(add1), // output wire [7 : 0] probe_out8

.probe_out9(add2), // output wire [7 : 0] probe_out9

.probe_out10(data1), // output wire [7 : 0] probe_out10

.probe_out11(data2), // output wire [7 : 0] probe_out11

.probe_out12(data3), // output wire [7 : 0] probe_out12

.probe_out13(finish_core_init), // output wire [0 : 0] probe_out13

.probe_out14(start_core_write), // output wire [0 : 0] probe_out14

.probe_out15(wait_core_int), // output wire [0 : 0] probe_out15

.probe_out16(finish_core_write) // output wire [0 : 0] probe_out16

); //--------------------------------------------------------------

ila_0 U4 (

.clk(clk_100M), // input wire clk

.probe0(start_write_rise), // input wire [0:0] probe0

.probe1(start_read_rise), // input wire [0:0] probe1

.probe2(m_axi_awvalid), // input wire [0:0] probe2

.probe3(m_axi_wvalid), // input wire [0:0] probe3

.probe4(m_axi_arvalid), // input wire [0:0] probe4

.probe5(m_axi_rready), // input wire [0:0] probe5

.probe6(m_axi_bready), // input wire [0:0] probe6

.probe7(s_axi_awready), // input wire [0:0] probe7

.probe8(s_axi_arready), // input wire [0:0] probe8

.probe9(s_axi_wready), // input wire [0:0] probe9

.probe10(s_axi_rvalid), // input wire [0:0] probe10

.probe11(s_axi_bvalid), // input wire [0:0] probe11

.probe12(io0_i), // input wire [0:0] probe12

.probe13(io0_o), // input wire [0:0] probe13

.probe14(io0_t), // input wire [0:0] probe14

.probe15(io1_i), // input wire [0:0] probe15

.probe16(io1_o), // input wire [0:0] probe16

.probe17(io1_t), // input wire [0:0] probe17

.probe18(io2_i), // input wire [0:0] probe18

.probe19(io2_o), // input wire [0:0] probe19

.probe20(io2_t), // input wire [0:0] probe20

.probe21(io3_i), // input wire [0:0] probe21

.probe22(io3_o), // input wire [0:0] probe22

.probe23(io3_t), // input wire [0:0] probe23

.probe24(ss_i), // input wire [0:0] probe24

.probe25(ss_o), // input wire [0:0] probe25

.probe26(ss_t), // input wire [0:0] probe26

.probe27(m_axi_awaddr), // input wire [6:0] probe27

.probe28(m_axi_araddr), // input wire [6:0] probe28

.probe29(current_state), // input wire [6:0] probe29

.probe30(core_init_cnt), // input wire [6:0] probe30

.probe31(m_axi_wdata), // input wire [31:0] probe31

.probe32(m_axi_rdata), // input wire [31:0] probe32

.probe33(s_axi_rdata), // input wire [31:0] probe33

.probe34(core_write_cnt), // input wire [6:0] probe34

.probe35(axi_awaddr), // input wire [6:0] probe35

.probe36(next_state), // input wire [6:0] probe36

.probe37(axi_wdata) // input wire [31:0] probe37

); //--------------------------------------------------------------

reg start_write;

always @(posedge clk_100M or posedge rst)

begin

if(rst)

start_write <= 'b0; else if (current_state == && core_init_en)

begin

if(core_init_cnt == )

begin

if(start_core_init_rise)

start_write <= 'b1;

else

start_write <= 'b0;

end else if(core_init_cnt == )

begin

if(finish_core_init_rise)

start_write <= 'b1;

else

start_write <= 'b0;

end else

start_write <= 'b1;

end else if(current_state == && core_write_en)

begin

if(core_write_cnt == )

begin

if(start_core_write_rise)

start_write <= 'b1;

else

start_write <= 'b0;

end else if(core_write_cnt == )

begin

if(wait_core_int_rise)

start_write <= 'b1;

else

start_write <= 'b0;

end else if(core_write_cnt == )

if(finish_core_write_rise)

start_write <= 'b1;

else

start_write <= 'b0; else

start_write <= 'b1;

end else

start_write <= 'b0;

end //--------------------------------------------------------------

reg start_write_delay;

wire start_write_rise; reg start_read_delay;

wire start_read_rise; reg start_core_init_delay;

wire start_core_init_rise; reg finish_core_init_delay;

wire finish_core_init_rise; reg start_core_write_delay;

wire start_core_write_rise; reg wait_core_int_delay;

wire wait_core_int_rise; reg finish_core_write_delay;

wire finish_core_write_rise; always @(posedge clk_100M or posedge rst)

begin

if (rst)

begin

start_write_delay <= 'b0;

start_read_delay <= 'b0;

start_core_init_delay <= 'b0;

finish_core_init_delay <= 'b0;

start_core_write_delay <= 'b0;

wait_core_int_delay <= 'b0;

finish_core_write_delay <= 'b0; end

else

begin

start_write_delay <= start_write;

start_read_delay <= start_read;

start_core_init_delay <= start_core_init;

finish_core_init_delay <= finish_core_init;

start_core_write_delay <= start_core_write;

wait_core_int_delay <= wait_core_int;

finish_core_write_delay <= finish_core_write; end

end assign start_write_rise = !start_write_delay && start_write;

assign start_read_rise = !start_read_delay && start_read;

assign start_core_init_rise = !start_core_init_delay && start_core_init;

assign finish_core_init_rise = !finish_core_init_delay && finish_core_init;

assign start_core_write_rise = !start_core_write_delay && start_core_write;

assign wait_core_int_rise = !wait_core_int_delay && wait_core_int;

assign finish_core_write_rise = !finish_core_write_delay && finish_core_write; //-------------------------------------------------------------- parameter DUMMY_DATA = 'hFF;

reg [:]axi_awaddr;

reg [:]axi_wdata; reg [:]core_init_cnt;

reg [:]core_write_cnt;

always @(posedge clk_100M or posedge rst)

begin

if (rst)

begin

core_init_cnt <= ;

core_write_cnt <= ;

end

else if (current_state == && core_init_en)

begin

case(core_init_cnt) :

begin

axi_awaddr <= 'h40;

axi_wdata <= 'h0000000A;

end :

begin

axi_awaddr <= 'h1C;

axi_wdata <= 'h80000000;

end :

begin

axi_awaddr <= 'h28;

axi_wdata <= 'h00000004;

end default:

begin

axi_awaddr <= 'h00;

axi_wdata <= 'h00000000;

end endcase end else if(current_state == && core_init_en)

begin

if(core_init_cnt < )

core_init_cnt <= core_init_cnt + 'b1;

else

core_init_cnt <= ;

end else if(current_state == && core_write_en)

begin

case(core_write_cnt)

/*

0:

begin

axi_awaddr <= 7'h70;

axi_wdata <= 32'hFFFFFFFF;

end

*/

:

begin

axi_awaddr <= 'h60;

axi_wdata <= 'h000001E6;

end :

begin

axi_awaddr <= 'h60;

axi_wdata <= 'h00000186;

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,cmd};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,add0};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,add1};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,add2};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,data1};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,data2};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,data3};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h68;

axi_wdata <= {'h000000,DUMMY_DATA};

end :

begin

axi_awaddr <= 'h70;

axi_wdata <= 'h00000000;

end :

begin

axi_awaddr <= 'h60;

axi_wdata <= 'h00000086;

end :

begin

axi_awaddr <= 'h20;

axi_wdata <= 'h00000004;

end :

begin

axi_awaddr <= 'h70;

axi_wdata <= 'hFFFFFFFF;

end :

begin

axi_awaddr <= 'h60;

axi_wdata <= 'h00000186;

end default:

begin

axi_awaddr <= 'h00;

axi_wdata <= 'h00000000;

end endcase

end else if(current_state == && core_write_en)

begin

if(core_write_cnt < )

core_write_cnt <= core_write_cnt + 'b1;

else

core_write_cnt <= ;

end end //--------------------------------------------------------------

reg [:]current_state;

reg [:]next_state;

always @ (posedge clk_100M or posedge rst)

begin

if(rst)

current_state <= IDLE;

else

current_state <= next_state;

end //--------------------------------------------------------------

parameter [:] IDLE = 'd0 ,

WRITE_START = 'd1 ,

WRITE_VALID = 'd2 ,

WRITE_READY = 'd3 ,

WRITE_BREADY = 'd4 ,

WRITE_END = 'd5 ,

READ_START = 'd11 ,

READ_VALID = 'd12 ,

READ_READY = 'd13 ,

READ_FINISH = 'd14 ,

READ_END = 'd15 ; always @ (*)

begin

next_state = IDLE;

case(current_state)

IDLE:

begin

if(start_write_rise)

next_state = WRITE_START;

else if(start_read_rise)

next_state = READ_START;

else

next_state = IDLE;

end WRITE_START:

begin

next_state = WRITE_VALID;

end WRITE_VALID:

begin

if(s_axi_awready && s_axi_wready)

next_state = WRITE_READY;

else

next_state = WRITE_VALID;

end WRITE_READY:

begin

if(s_axi_bvalid)

next_state = WRITE_BREADY;

else

next_state = WRITE_READY;

end WRITE_BREADY:

begin

next_state = WRITE_END;

end WRITE_END:

begin

next_state = IDLE;

end READ_START:

begin

next_state = READ_VALID;

end READ_VALID:

begin

if(s_axi_arready)

next_state = READ_READY;

else

next_state = READ_VALID;

end READ_READY:

begin

if(s_axi_rvalid)

next_state = READ_FINISH;

else

next_state = READ_READY;

end READ_FINISH:

begin

next_state = READ_END;

end READ_END:

begin

next_state = IDLE;

end endcase

end //-------------------------------------------------------------

reg m_axi_awvalid;

reg m_axi_wvalid;

reg m_axi_arvalid; reg m_axi_rready;

reg m_axi_bready; reg [:]m_axi_awaddr;

reg [:]m_axi_araddr; reg [:]m_axi_wdata;

reg [:]m_axi_rdata; always @(posedge clk_100M or posedge rst)

begin

if (rst)

begin

m_axi_awvalid <= 'b0;

m_axi_wvalid <= 'b0;

m_axi_arvalid <= 'b0;

m_axi_rready <= 'b0;

m_axi_bready <= 'b0;

m_axi_awaddr <= ;

m_axi_araddr <= ;

m_axi_wdata <= ;

m_axi_rdata <= ;

end

else

begin m_axi_awvalid <= 'b0;

m_axi_wvalid <= 'b0;

m_axi_arvalid <= 'b0;

m_axi_rready <= 'b0;

m_axi_bready <= 'b0; case(current_state)

//IDLE: WRITE_START:

begin

m_axi_awaddr <= axi_awaddr;

m_axi_wdata <= axi_wdata;

m_axi_awvalid <= 'b1;

m_axi_wvalid <= 'b1;

m_axi_bready <= 'b1;

end WRITE_VALID:

begin

m_axi_awvalid <= 'b1;

m_axi_wvalid <= 'b1;

m_axi_bready <= 'b1;

end WRITE_READY:

begin

m_axi_bready <= 'b1;

end //WRITE_BREADY:

//WRITE_END: READ_START:

begin

m_axi_araddr <= axi_araddr;

m_axi_arvalid <= 'b1;

end READ_VALID:

begin

m_axi_arvalid <= 'b1;

end //READ_READY: READ_FINISH:

begin

m_axi_rdata <= s_axi_rdata;

m_axi_rready <= 'b1;

end //READ_END: default:

begin

m_axi_awvalid <= 'b0;

m_axi_wvalid <= 'b0;

m_axi_arvalid <= 'b0;

m_axi_rready <= 'b0;

m_axi_bready <= 'b0;

end endcase end

end //-------------------------------------------------------------

wire s_axi_awready;

wire s_axi_arready;

wire s_axi_wready;

wire s_axi_rvalid;

wire s_axi_bvalid;

wire [:]s_axi_rdata; wire io0_i;

wire io0_o;

wire io0_t;

wire io1_i;

wire io1_o;

wire io1_t;

wire io2_i;

wire io2_o;

wire io2_t;

wire io3_i;

wire io3_o;

wire io3_t;

wire ss_i;

wire ss_o;

wire ss_t; axi_quad_spi_0 U1 (

.ext_spi_clk(clk_100M), // input wire ext_spi_clk

.s_axi_aclk(clk_100M), // input wire s_axi_aclk

.s_axi_aresetn(~rst), // input wire s_axi_aresetn

.s_axi_awaddr(m_axi_awaddr), // input wire [6 : 0] s_axi_awaddr

.s_axi_awvalid(m_axi_awvalid), // input wire s_axi_awvalid

.s_axi_awready(s_axi_awready), // output wire s_axi_awready

.s_axi_wdata(m_axi_wdata), // input wire [31 : 0] s_axi_wdata

.s_axi_wstrb('b1111), // input wire [3 : 0] s_axi_wstrb

.s_axi_wvalid(m_axi_wvalid), // input wire s_axi_wvalid

.s_axi_wready(s_axi_wready), // output wire s_axi_wready

.s_axi_bresp(), // output wire [1 : 0] s_axi_bresp

.s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid

.s_axi_bready(m_axi_bready), // input wire s_axi_bready

.s_axi_araddr(m_axi_araddr), // input wire [6 : 0] s_axi_araddr

.s_axi_arvalid(m_axi_arvalid), // input wire s_axi_arvalid

.s_axi_arready(s_axi_arready), // output wire s_axi_arready

.s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata

.s_axi_rresp(), // output wire [1 : 0] s_axi_rresp

.s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid

.s_axi_rready(m_axi_rready), // input wire s_axi_rready

.io0_i(io0_i), // input wire io0_i

.io0_o(io0_o), // output wire io0_o

.io0_t(io0_t), // output wire io0_t

.io1_i(io1_i), // input wire io1_i

.io1_o(io1_o), // output wire io1_o

.io1_t(io1_t), // output wire io1_t

.io2_i(io2_i), // input wire io2_i

.io2_o(io2_o), // output wire io2_o

.io2_t(io2_t), // output wire io2_t

.io3_i(io3_i), // input wire io3_i

.io3_o(io3_o), // output wire io3_o

.io3_t(io3_t), // output wire io3_t

.ss_i(ss_i), // input wire [0 : 0] ss_i

.ss_o(ss_o), // output wire [0 : 0] ss_o

.ss_t(ss_t), // output wire ss_t

.cfgclk(cfgclk), // output wire cfgclk

.cfgmclk(cfgmclk), // output wire cfgmclk

.eos(eos), // output wire eos

.preq(preq), // output wire preq

.ip2intc_irpt(ip2intc_irpt) // output wire ip2intc_irpt

); IOBUF dq0(

.IO (spi_dq[]),

.O (io0_i),

.I (io0_o),

.T (io0_t)

); IOBUF dq1(

.IO (spi_dq[]),

.O (io1_i),

.I (io1_o),

.T (io1_t)

); IOBUF dq2(

.IO (spi_dq[]),

.O (io2_i),

.I (io2_o),

.T (io2_t)

); IOBUF dq3(

.IO (spi_dq[]),

.O (io3_i),

.I (io3_o),

.T (io3_t)

); IOBUF spiss(

.IO (spi_ss),

.O (ss_i),

.I (ss_o),

.T (ss_t)

); endmodule

关于AXI_Quad_SPI的寄存器配置的更多相关文章

- ili9325--LCD寄存器配置研究

2011-06-22 22:18:12 自己根据ili9325的规格书编写驱动.发现LCD屏没显示.于是怀疑是某些寄存器设置错误.要调试的话最好还是先熟悉寄存器的作用,调试的时候只要看到现象就能分析了 ...

- STM8串口初始化寄存器配置

//库函数配置 UART1_DeInit(); UART1_Init((u32)1000000, UART1_WORDLENGTH_8D, UART1_STOPBITS_1, \ UART1_PARI ...

- 摄像头驱动OV7725学习笔记连载(二):0V7725 SCCB时序的实现之寄存器配置

上一篇博客主要介绍了OV7725的电气特性以及SCCB接口的时序和输出一帧图像的时序图以及数据的拼接.输出一帧图像与输出时钟PCLK有关. 上图是OV7725实现的整体框架,有点丑.FPGA描述SCC ...

- stm8s + si4463 寄存器配置

/***********************************************函 数: main功 能: 程序入口输 入: /输 出: /描 述: /**************** ...

- 与或左移右移操作在ARM寄存器配置中的作用

逻辑运算: 与运算&:与0清零 清零用与运算 或运算 |:或1置一 置一用或运算 异或 ^:不同为1 /*****单个寄存器清零置一*************************** ...

- STM32的操作过程,寄存器配置与调试过程(转载)

很多学习stm32的,为什么学习stm32他也不知道,我们所知道的就是各个论坛讨论stm32的很多,而我们很多人之所以学习stm32是很多的淘宝卖家做了大量的图片文字宣传,于是我们经不住诱惑就买了板子 ...

- AD9361寄存器配置顺序,循环模式,自收自发

:] cmd_data; :] index; begin case(index) 'h000,8'h00};//set spi -- 'h3df,8'h01};//set init -- 'h037, ...

- USB2.0学习笔记连载(十八):keil实现寄存器的配置及相关函数讲解(二)

其实之前也有提及过,Cypress公司提供的官方文件和应用手册真的可以解决很多问题.做的也很人性化,操作也及其简单,几乎只要在 TD_int()里面配置一些常用的参数即可,其他都可以不用操作. 作为一 ...

- DSP EPWM学习笔记2 - EPWM相关寄存器设置问题解析

DSP EPWM学习笔记2 - EPWM相关寄存器设置问题解析 彭会锋 本篇主要针对不太熟悉的TZ 故障捕获 和 DB 死区产生两个子模块进行学习研究 感觉TI的寄存器命名还是有一定规律可循的 SEL ...

随机推荐

- LexAndYacc 安装程序

在ubuntu 下面执行 sudo apt-get install byacc flex bison

- Ubuntu add sudo

为了安全起见,ubuntu中的普通用户一般没有root权限,因此即使知道管理员密码也无法使用sudo,但这个情况可以通过加入sudoer列表或者加入sudo组来改变. 拓展: 不管使用哪种方式,使得一 ...

- VMware网络连接IP设置

网络配置(仅主机模式) 一.改变虚拟机IP地址达到联网目的 仅主机模式,第一步,打开我的电脑属性,查看VMt1网卡IP设置,设置一个区段:192.168.xx.aa xx.aa自由设置,简 ...

- dubbo AdaptiveExtension

AdaptiveExtension 自适应Extension,作者其实在使用Extension方和Extension之间插入AdaptiveExtension用来自适应,也可以说是适配. 所以,我们发 ...

- [LeetCode&Python] Problem 387. First Unique Character in a String

Given a string, find the first non-repeating character in it and return it's index. If it doesn't ex ...

- P1242 新汉诺塔(搜索+模拟退火)

题目链接:传送门 题目大意: 汉诺塔,给定n个盘子(n <= 45),起始状态和结束状态,求最小的步数以及路径. 思路: 考虑用dfs贪心地将剩余最大盘归位. #include<bits/ ...

- Automatic Text Difficulty Classifier Assisting the Selection Of Adequate Reading Materials For European Portuguese Teaching --paper

the system uses existing Natural Language Processing (NLP) tools, a parser and an hyphenator, and tw ...

- Linux中ctrl+z,ctrl+d和ctrl+c的区别

Ctrl-c Kill foreground processCtrl-z Suspend foreground processCtrl-d Terminate input, or exit shell

- 2017.5.11 MapReduce运行机制

和HDFS一样,MapReduce也是采用Master/Slave的架构 MapReduce1包含4个部分:Client.JobTracker.TaskTracker和Task Client 将JAR ...

- 《DSP using MATLAB》Problem 7.1

只有春节那么几天才能和家人团聚,看着爸爸妈妈一年比一年老,自己还是一无所有,照顾好自己尚且惭愧,真是悲从中来,又能怎么办呢, 唯有奋发努力,时不我待,多想想怎么赚钱,加油. 代码: function ...