【RL-TCPnet网络教程】第5章 PHY芯片和STM32的MAC基础知识

第5章 PHY芯片和STM32的MAC基础知识

本章节为大家讲解STM32自带的MAC和PHY芯片的基础知识,为下一章底层驱动的讲解做一个铺垫。

5.1 初学者重要提示

5.2 什么是MAC

5.3 MAC地址

5.4 STM32自带MAC基础知识

5.5 以太网PHY基础知识

5.6 总结

5.1 初学者重要提示

1、学习本章节后,务必学习STM32参考手册中MAC章节的基础知识讲解,非常重要。

2、实际项目中,关于MAC的配置问题,需要大家学习我们论坛网友发的这个帖子。

IEEE MAC地址购买价格及购买方案选择:http://bbs.armfly.com/read.php?tid=28416 。

5.2 什么是MAC

媒体访问控制(MAC,Media Access Control),又称作介质访问控制,简称MAC,是局域网中数据链路层的下层部分,提供地址及媒体访问的控制方式,使得不同设备或网络上的节点可以在多点的网络上通信,而不会互相冲突,上述的特性在局域网中格外重要。早期网络发展时以MAC判别各个网络接口的位置,但后来互联网发展后,才有IP的制定与使用。若只是两台设备之间全双工的通信,因为两台设备可以同时发送及接收数据,不会冲突,因此不需要用到MAC协议。

媒体访问控制MAC子层负责解决与媒体接入有关的问题,在物理层的基础上进行无差错的通信。

MAC子层是网络与设备的接口,它从网络层接收数据帧,然后通过媒体访问规则和物理层将数据帧发送到物理链路上。它也从物理层接收数据帧,再送到网络层。总的来说,MAC有三大功能:

(1)决定节点何时发送数据包。

(2)将数据帧发送到物理层,然后发送到物理链路。

(3)从物理层接收数据帧,然后送给网络层处理。

其中最重要的是第一点:决定节点何时发送数据包。对于每一种媒体访问控制技术,用来控制节点发送时机的规则叫做媒体访问规则。局域网上的节点不能想要发送数据就发送,节点只能在轮到它的时候才发送。

5.3 MAC地址

MAC地址,又称为物理地址、硬件地址,用来定义网络设备的位置。在OSI模型中,第三层网络层负责 IP地址,第二层数据链路层则负责 MAC地址。因此一个主机会有一个MAC地址,而每个网络位置会有一个专属于它的IP地址。

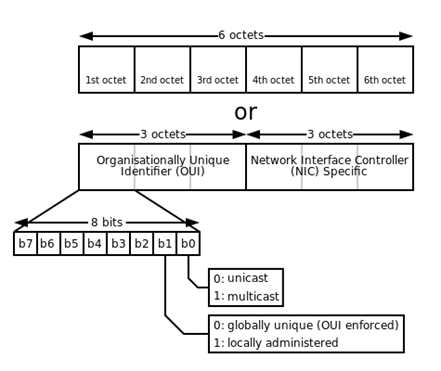

MAC地址长度是48bit(6字节),由16进制的数字组成,分为前24位和后24位:

(1)前24位叫做组织唯一标志符(Organizationally Unique Identifier,即OUI),是由IEEE的注册管理机构给不同厂家分配的代码,区分了不同的厂家。

(2)后24位是由厂家自己分配的,称为扩展标识符。同一个厂家生产的网卡中MAC地址后24位是不同的。

MAC地址的完整数据格式如下(来自wiki百科):

第一个字节的后两位比较重要:

b0 = 0:表示MAC单播地址。

b0 = 1 : 表示MAC组播地址。

b1 = 0:表示OUI分配的全球唯一MAC地址。

b1 = 1:表示用于本地管理的MAC地址。

为了更好地理解,举几个例子:

00:xx:xx:xx:xx:xx是MAC单播地址。

01:xx:xx:xx:xx:xx是MAC组播地址。

01:00:5e:xx:xx:xx是IPv4组播地址。

ff:ff:ff:ff:ff:ff则作为广播地址。

00:50:c2:xx:xx:xx 是意法半导体的MAC地址。

5.4 STM32自带MAC基础知识

关于STM32自带的MAC部分,STM32参考手册中写的晦涩难懂,特别是中文翻译版本,逻辑混乱,如果可以的话,建议大家看英文版。

STM32参考手册中对MAC的讲解主要分为三部分:

1、MAC的接口MII和RMII。

参考手册中对这一部分讲解的比较详细,也比较容易理解,建议初学者务必读一读。我们这里就不将其复制粘贴过来了。

2、MAC802.3帧格式,帧发送,帧接收等方面的讲解。

这一个部分知识点理解起来比较困难,配合下一章节的底层驱动就好理解了。

3、MAC的DMA收发方式控制。

手册中给出了DMA方式的发送和接收的初始化顺序,在下一章节讲解底层驱动的时候结合驱动代码会理解的更好,建议初学者也读一遍。

5.5 以太网PHY基础知识

仅有STM32自带的MAC还不能做网络通信,还需要外接以太网PHY芯片才可以,如同RS485通信一样,仅有一个串口是不行的,还需要外接RS485的PHY芯片。

PHY(Port Physical Layer),可称之为端口物理层,是一个对OSI模型物理层的简称。现在常用于STM32的有DP83848,LAN8270,DM9161/9162等。这些PHY芯片都大同小异,基本寄存器都是一样的,只有扩展寄存和厂商专门设置的寄存器不同。如果用户将其中一个PHY驱动成功了,驱动另一个也是非常方便的,下面是DP83848和DM9161/9162的基本寄存器和扩展寄存器:

/* DP83848C and DM9161 PHY Registers is the same */ #define PHY_REG_BMCR 0x00 /* Basic Mode Control Register */ #define PHY_REG_BMSR 0x01 /* Basic Mode Status Register */ #define PHY_REG_IDR1 0x02 /* PHY Identifier 1 */ #define PHY_REG_IDR2 0x03 /* PHY Identifier 2 */ #define PHY_REG_ANAR 0x04 /* Auto-Negotiation Advertisement */ #define PHY_REG_ANLPAR 0x05 /* Auto-Neg. Link Partner Abitily */ #define PHY_REG_ANER 0x06 /* Auto-Neg. Expansion Register */ #define PHY_REG_ANNPTR 0x07 /* Auto-Neg. Next Page TX .DM9161 NO */ /* Register BMCR bit defination */ #define PHY_FULLD_100M 0x2100 /* Full Duplex 100Mbit */ #define PHY_HALFD_100M 0x2000 /* Half Duplex 100Mbit */ #define PHY_FULLD_10M 0x0100 /* Full Duplex 10Mbit */ #define PHY_HALFD_10M 0x0000 /* Half Duplex 10MBit */ #define PHY_AUTO_NEG 0x1000 /* Select Auto Negotiation */ /* PHY Extended Registers only for DP83848C */ #define PHY_REG_STS 0x10 /* Status Register */ #define PHY_REG_MICR 0x11 /* MII Interrupt Control Register */ #define PHY_REG_MISR 0x12 /* MII Interrupt Status Register */ #define PHY_REG_FCSCR 0x14 /* False Carrier Sense Counter */ #define PHY_REG_RECR 0x15 /* Receive Error Counter */ #define PHY_REG_PCSR 0x16 /* PCS Sublayer Config. and Status */ #define PHY_REG_RBR 0x17 /* RMII and Bypass Register */ #define PHY_REG_LEDCR 0x18 /* LED Direct Control Register */ #define PHY_REG_PHYCR 0x19 /* PHY Control Register */ #define PHY_REG_10BTSCR 0x1A /* 10Base-T Status/Control Register */ #define PHY_REG_CDCTRL1 0x1B /* CD Test Control and BIST Extens. */ #define PHY_REG_EDCR 0x1D /* Energy Detect Control Register */ /* PHY Extended Registers only for DM9161 */ #define PHY_REG_DSCR 0x10 /* Specified Congfiguration Register */ #define PHY_REG_DSCSR 0x11 /* Specified Congfiguration and Status Register */ #define PHY_REG_10BTCSR 0x12 /* 10Base-T Status/Control Register */ #define PHY_REG_PWDOR 0x13 /* Power Down Control Register */ #define PHY_REG_CONGFIG 0x14 /* Specified Congfig Register */ #define PHY_REG_INTERRUPT 0x15 /* Specified interrupt Register */ #define PHY_REG_SRECR 0x16 /* Specified Receive Error Counter */ #define PHY_REG_DISCR 0x17 /* Specified Disconnect Counter Register */ #define PHY_REG_RLSR 0x18 /* Hardware reset latch state Register */ #define PHY_REG_PSCR 0x1D /* Power Saving control register */

对于初学者来说,了解这些知识点就够了,具体如何配置这些寄存器会在下个章节讲解。

5.6 总结

本章节就为大家讲解这么多,主要是为下章节的讲解做个铺垫。学习完毕本章节后,务必将STM32参考手册中MAC章节读一遍。

【RL-TCPnet网络教程】第5章 PHY芯片和STM32的MAC基础知识的更多相关文章

- 【STM32H7教程】第55章 STM32H7的图形加速器DMA2D的基础知识和HAL库API

完整教程下载地址:http://www.armbbs.cn/forum.php?mod=viewthread&tid=86980 第55章 STM32H7的图形加速器DMA2D的基 ...

- 【安富莱TCPnet网络教程】HTTP通信实例

第41章 HTTP超文本传输协议基础知识 本章节为大家讲解HTTP(HyperText Transfer Protocol,超文本传输协议),从本章节开始,正式进入嵌入式Web的设计和学习. ...

- 【RL-TCPnet网络教程】第6章 RL-TCPnet底层驱动说明

第6章 RL-TCPnet底层驱动说明 本章节为大家讲解RL-TCPnet的底层驱动,主要是STM32自带MAC的驱动实现和PHY的驱动实现. 6.1 初学者重要提示 6.2 KEI ...

- 【STM32H7教程】第15章 STM32H7的GPIO基础知识(重要)

完整教程下载地址:http://www.armbbs.cn/forum.php?mod=viewthread&tid=86980 第15章 STM32H7的GPIO基础知识(重要) ...

- 【RL-TCPnet网络教程】第2章 嵌入式网络协议栈基础知识

第2章 嵌入式网络协议栈基础知识 本章教程为大家介绍嵌入式网络协议栈基础知识,本章先让大家有一个全面的认识,后面章节中会为大家逐一讲解用到的协议. 基础知识整理自百度百科,wiki百科等 ...

- 【RL-TCPnet网络教程】第32章 RL-TCPnet之Telnet服务器

第32章 RL-TCPnet之Telnet服务器 本章节为大家讲解RL-TCPnet的Telnet应用,学习本章节前,务必要优先学习第31章的Telnet基础知识.有了这些基础知识之后,再搞 ...

- 【RL-TCPnet网络教程】第30章 RL-TCPnet之SNTP网络时间获取

第30章 RL-TCPnet之SNTP网络时间获取 本章节为大家讲解RL-TCPnet的SNTP应用,学习本章节前,务必要优先学习第29章的NTP基础知识.有了这些基础知识之后,再搞本章节会 ...

- 【RL-TCPnet网络教程】第28章 RL-TCPnet之DNS应用

第28章 RL-TCPnet之DNS应用 本章节为大家讲解RL-TCPnet的DNS应用,学习本章节前,务必要优先学习第27章的DNS基础知识.有了这些基础知识之后,再搞本章节会有事半功倍的 ...

- 【RL-TCPnet网络教程】第20章 RL-TCPnet之BSD Socket客户端

第20章 RL-TCPnet之BSD Socket客户端 本章节为大家讲解RL-TCPnet的BSD Socket,学习本章节前,务必要优先学习第18章的Socket基础知识.有了这些基础知 ...

随机推荐

- Vue:window.onresize

1. 添加属性screenHeight 和 timer. screenHeight: window.innerHeight timer: '' // window.onresize函数频繁调用时,页 ...

- 八 ip和子网详解

IP和子网掩码我们都知道,IP是由四段数字组成,在此,我们先来了解一下3类常用的IP A类IP段 0.0.0.0 到127.255.255.255 B类IP段 128.0.0.0 到191.255. ...

- 使用HDFS完成wordcount词频统计

任务需求 统计HDFS上文件的wordcount,并将统计结果输出到HDFS 功能拆解 读取HDFS文件 业务处理(词频统计) 缓存处理结果 将结果输出到HDFS 数据准备 事先往HDFS上传需要进行 ...

- git增加子模块

要拉取GIT代码时,有时候需要拉取多个GIT模块,一起配合使用: 1.下载主模块: git clone -b master http://username:passwd@git.wondershare ...

- Python3学习笔记十三

1. css 老师的博客:http://www.cnblogs.com/yuanchenqi/articles/6856399.html 选择器:找到想要改变的标签 css的功能:渲染和布局 2. ...

- net读取文件字节流要注意的小细节

]; var numBytesToRead = (int)fileLenght; ; using (fs) { do { ); numBytesRead += n; numBytesToRead -= ...

- 将一个整数M分成N个整数 要求每个都在区间【minV, maxV】之间

将一个整数M分成N个整数 要求每个都在区间[minV, maxV]之间,怎么分比较快捷???? 说明: N是>=1且<=9的数,分割的数据只要符合[minV, maxV]区间即可,可以是等 ...

- tensorflow Tensorboard可视化-【老鱼学tensorflow】

tensorflow自带了可视化的工具:Tensorboard.有了这个可视化工具,可以让我们在调整各项参数时有了可视化的依据. 本次我们先用Tensorboard来可视化Tensorflow的结构. ...

- 随笔【js】

1.js是大小写敏感的 2. 区别 getElementBy ID , getElementsBy Name, getElementsBy TagName以人来举例说明,人有能标识身份的身份证,有姓 ...

- git修改远程仓库关联

公司搬移, 作为git仓库的服务器IP地址变了. 本地代码挺多,重新检出太占时间,可以修改一个什么配置让我本地仓库和新的远程仓库建立关联吗, 答案是肯定的! 方法有很多,这里简单介绍几种: 以下均以项 ...