Translation Lookaside Buffer

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION

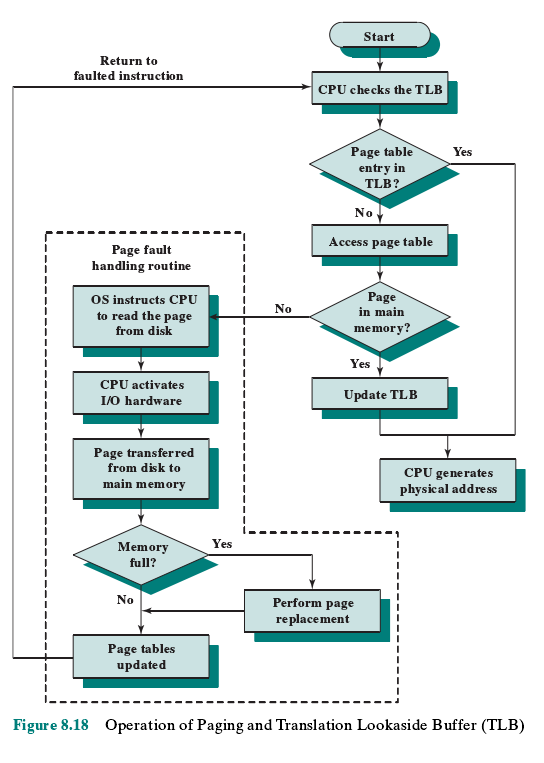

In principle, then, every virtual memory reference can cause two physical mem-

ory accesses: one to fetch the appropriate page table entry, and one to fetch the

desired data. Thus, a straightforward virtual memory scheme would have the effect

of doubling the memory access time. To overcome this problem, most virtual

memory schemes make use of a special cache for page table entries, usually called

a translation lookaside buffer (TLB). This cache functions in the same way as a

memory cache and contains those page table entries that have been most recently

used. Figure 8.18 is a flowchart that shows the use of the TLB. By the principle of

locality, most virtual memory references will be to locations in recently used pages.

Therefore, most references will involve page table entries in the cache. Studies of

the VAX TLB have shown that this scheme can significantly improve performance

[CLAR85, SATY81].

Note that the virtual memory mechanism must interact with the cache system

(not the TLB cache, but the main memory cache). This is illustrated in Figure 8.19.

A virtual address will generally be in the form of a page number, offset. First, the

memory system consults the TLB to see if the matching page table entry is present.

If it is, the real (physical) address is generated by combining the frame number with

the offset. If not, the entry is accessed from a page table. Once the real address is

generated, which is in the form of a tag and a remainder, the cache is consulted to

see if the block containing that word is present (see Figure 4.5). If so, it is returned

to the processor. If not, the word is retrieved from main memory.

The reader should be able to appreciate the complexity of the processor hard-

ware involved in a single memory reference. The virtual address is translated into

a real address. This involves reference to a page table, which may be in the TLB, in

main memory, or on disk. The referenced word may be in cache, in main memory,

or on disk. In the latter case, the page containing the word must be loaded into main

memory and its block loaded into the cache. In addition, the page table entry for

that page must be updated.

Translation Lookaside Buffer的更多相关文章

- 全面学习理解TLB(Translation Look-aside Buffer)地址变换高速缓存

全面学习理解TLB(Translation Look-aside Buffer)地址变换高速缓存 前言: 本文学习思路是:存在缘由 --> 存在好处 --> 定义性质 --> 具 ...

- PatentTips - Virtual translation lookaside buffer

BACKGROUND OF THE INVENTION A conventional virtual-machine monitor (VM monitor) typically runs on a ...

- 【转】TLB(Translation Lookaside Buffers,TLB)的作用

原文网址:http://sdnydubing.blog.163.com/blog/static/137470570201122810503396/ 从虚拟地址到物理地址的转换过程可知:使用一级页表进行 ...

- Linux中Buffer和Cache的区别

1. Cache:缓存区,是高速缓存,是位于CPU和主内存之间的容量较小但速度很快的存储器,因为CPU的速度远远高于主内存的速度,CPU从内存中读取数据需等待很长的时间,而 Cache保存着CPU刚 ...

- armv8 memory translation

AArch32,arm的32bit架构: AArch64,arm的64bit架构: ARMv8.2-LPA,是armv8.2中的新feature,扩大了IPA和PA的支持范围,从48bit扩展到52b ...

- Cache 和 Buffer 都是缓存,主要区别是什么?【转】

作者:Towser 链接:https://www.zhihu.com/question/26190832/answer/32387918 来源:知乎 著作权归作者所有.商业转载请联系作者获得授权,非商 ...

- 【学习笔记】cache/buffer

cache 是为了弥补高速设备和低速设备的鸿沟而引入的中间层,最终起到**加快访问速度**的作用.buffer 的主要目的进行流量整形,把突发的大数量较小规模的 I/O 整理成平稳的小数量较大规模的 ...

- cache和buffer区别探讨

一. 1.Buffer(缓冲区)是系统两端处理速度平衡(从长时间尺度上看)时使用的.它的引入是为了减小短期内突发I/O的影响,起到流量整形的作用.比如生产者——消费者问题,他们产生和消耗资源的速度大体 ...

- PatentTips - Supporting address translation in a virtual machine environment

BACKGROUND A conventional virtual-machine monitor (VMM) typically runs on a computer and presents to ...

随机推荐

- 对Android项目中的文件夹进行解释

对Android项目中的文件夹进行解释: · src:里面存放的是Activity程序,或者是以后的其他组件,在此文件夹之中建立类的时候一定要注意,包名称不能是一级. · gen:此文件夹中的内容是自 ...

- 【项目启动】 tomcat启动,项目无法启动,无法正常访问/项目可以启动,报错:java.lang.ClassNotFoundException: ContextLoaderListener

使用maven搭建项目(这个错误和是不是使用maven搭建项目没有关系),然后部署到tomcat中运行. 出现问题1: tomcat跑起来了,但是启动时间很短,没有报错,项目不能正常访问 项目启动时间 ...

- php:订单号和时区

1.php制作订单号 $data['orderid'] = date("YmdHis") . settype(rand(100000, 999999), string) ; 2.p ...

- 2016.7.8 计算机网络复习要点第四章之地址解析协议ARP

1.地址解析协议ARP:知道一个机器的IP地址,需要找到其相应的硬件地址:ARP协议的用途是为了从网络层使用的IP地址解析出在链路层使用的硬件地址: 2.由于是IP协议使用了ARP协议,因此通常就把A ...

- 二分搜索 UVALive 6076 Yukari's Birthday (12长春K)

题目传送门 题意:问使得sum (k^i) = n || n -1 (1 <= i <= r) 的min (r*k)组合的r和k 分析:r的最大不会超过40,枚举r,二分搜索k.注意会爆 ...

- LCIS HDOJ 4512 吉哥系列故事——完美队形I

题目传送门 题意:中文题面 分析:LCIS应用:设置b[]为a[]的反转,然后LCIS,若相等的是自己本身,则+1, 否则+2 代码: #include <cstdio> #include ...

- 最短路(Floyd_Warshall) POJ 2240 Arbitrage

题目传送门 /* 最短路:Floyd模板题 只要把+改为*就ok了,热闹后判断d[i][i]是否大于1 文件输入的ONLINE_JUDGE少写了个_,WA了N遍:) */ #include <c ...

- Oracle 使用小计(2)

1.时间转换 1.1 字符串转时间 今天需要写SQL语句更新数据库的时间,按照SQL Server的习惯写成 UPDATE TABLE A ’ WHERE ORDER_ID = ‘A12345678’ ...

- CodeForces Round 198

总体感觉这次出的题偏数学,数学若菜表示果断被虐.不过看起来由于大家都被虐我2题居然排到331,rating又升了74.Div2-AA. The Walltime limit per test1 sec ...

- 中国大数据六大技术变迁记(CSDN)

大会召开前期,特别梳理了历届大会亮点以记录中国大数据技术领域发展历程,并立足当下生态圈现状对即将召开的BDTC 2014进行展望: 追本溯源,悉大数据六大技术变迁 伴随着大数据技术大会的发展,我们亲历 ...