FPGA编程技巧系列之按键边沿检测

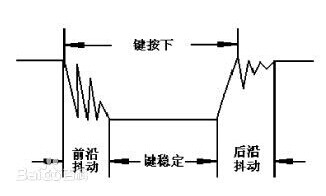

- 抖动的产生:

通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是按键消抖。

- 抖动时间

抖动时间的长短由按键的机械特性决定,一般为5ms~10ms。这是一个很重要的时间参数,在很多场合都要用到按键稳定闭合时间的长短则是由操作人员的按键动作决定的,一般为零点几秒至数秒。键抖动会引起一次按键被误读多次。为确保FPGA对键的一次闭合仅作一次处理,必须去除键抖动。在键闭合稳定时读取键的状态,并且必须判别到键释放稳定后再作处理。

图1 按键抖动

- FPGA内实现消抖的方法

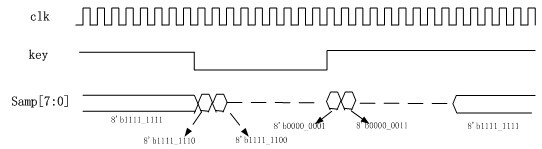

在FPGA内实现按键消抖的方法多种多样,但是最简单的是采用移位寄存器的方法进行消抖。因为移位寄存器的方法不需要对时钟进行分频,也不需要进行延时等复杂操作,即可实现对按键边沿的检测。假设未按下时键值=1.

1、在无键按下时,移位寄存器samp[7:0]始终采集到高电平,即samp[7:0]=8'b1111_1111;

2、当键按下时,samp[7:0]将采集到低电平,数据的变化方式为samp[7:0]=8'b1111_1110-->8'b1111_1100-->8'b1111_1000--> ........——>8'b0000_0000;samp[7:0]=8'b1111_1110即为按键下降沿。

3、当松开按键时,samp[7:0]将重新采集到高电平,数据变化方式为samp[7:0]=8'b0000_0001-->8'b0000_0011--> ........-->8'b1111_1111;当samp[7:0]=8'b0111_1111时,即为按键上升沿。

图2 移位寄存器消抖原理图

- 参考Verilog代码

//模块名:EdgeDetect,边沿检测

//button:按键,无键按下时为高电平//clk:10M时钟

//rst:复位按钮,低电平有效

//rise:检测到上升沿,高电平有效,宽度为1个clk

//fall:检测到下降沿,高电平有效,宽度为1个clk module EdgeDetect(

input clk,

input rst,

input button,

output reg rise,

output reg fall

); reg[7:0] samp;//移位寄存器采集button键值

//移位寄存器采集button信息

always@(posedge clk or negedge rst)

begin

if(!rst)

samp<='b1111_1111;

else

samp<={samp[:],button};

end //产生上升沿信息

always@(posedge clk or negedge rst)

begin

if(!rst)

rise<='b0;

else if(samp=='b0111_1111)

rise<='b1;

else

rise<='b0;

end //产生下降沿信息

always@(posedge clk or negedge rst)

begin

if(!rst)

fall<='b0;

else if(samp=='b1111_1110)

fall<='b1;

else

fall<='b0;

end endmodule

FPGA编程技巧系列之按键边沿检测的更多相关文章

- FPGA编程技巧系列之输入输出偏移约束详解

1. 偏移约束的作用 偏移约束(Offset Constraint)用来定义一个外部时钟引脚(Pad)和数据输入输出引脚之间的时序关系,这种时序关系也被称为器件上的Pad-to-Setup或Clo ...

- Xilinx FPGA编程技巧之常用时序约束详解

1. 基本的约束方法 为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取.最普遍的三种路径为: 输入路径(Input Path),使用输入约束 寄存器到寄存器路径(Register-to ...

- 少儿编程|Scratch编程教程系列合集,总有一款适合你

如果觉得资源不错,友情转发,贵在分享!!! 少儿编程Scratch: 少儿编程Scratch第一讲:Scratch完美的初体验少儿编程Scratch第二讲:奇妙的接球小游戏少儿编程Scratch第三讲 ...

- 边沿检测方法-FPGA入门教程

本节实验主要讲解FPGA开发中边沿检测方法,我们在设计中会经常用到.这个地方大家一定要理解. 1.1.1.原理介绍 学习HDL语言设计与其他语言不一样,HDL语言设计需要考虑更多的信号的电气特性,时序 ...

- FPGA学习笔记之格雷码、边沿检测、门控时钟

一.格雷码 格雷码的优点主要是进位时只有一位跳变,误码率低. 1.二进制转格雷码 我们观察下表: 二进制码 格雷码 00 00 01 01 10 11 11 10 二进制码表示为B[],格雷码表示为G ...

- FPGA基础入门篇(四) 边沿检测电路

FPGA基础入门篇(四)--边沿检测电路 一.边沿检测 边沿检测,就是检测输入信号,或者FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测.在检测到所需要的边沿后产生一个高电平的脉冲.这在FPGA电 ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

- FPGA调试技巧

FPGA调试技巧 八月,一直在debug, 编译,查信号,几乎没机会,也没心思停留下来看点东西,静心思考,做点笔记.今天,在硬盘上翻到了保存已久,但一直没想起来读的一本手册.这是我初入职场,决定从硬件 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

随机推荐

- c#-关于自动属性的思考

参考:c#-关于自动属性的思考 我的理解:自动属性跟 公有字段 一模一样,编程习惯而已.目前是这么认为的. 自动属性:public string Name{ get; set } 公有字段:pub ...

- No tests found with test runner 'JUnit 3'

报异常:No tests found with test runner 'JUnit 3' 解决方案: 主要因为你当前建的JUnit类是3的版本,将该类备份,重新创建一个类. 1.右键目录New--O ...

- BZOJ_2186_[Sdoi2008]沙拉公主的困惑_欧拉函数

BZOJ_2186_[Sdoi2008]沙拉公主的困惑_欧拉函数 Description 大富翁国因为通货膨胀,以及假钞泛滥,政府决定推出一项新的政策:现有钞票编号范围为1到N的阶乘,但是,政府只发行 ...

- Luogu网校听课笔记(自用

TG助学课——noilinux 8.2 深夜 Noi Linux的使用——darkflames的博客 #include<bits/stdc++.h> using namespace std ...

- Python3中使用PyMongo的方法详解

前言 本文主要给大家介绍的是关于在Python3使用PyMongo的方法,分享出来供大家参考学习,下面话不多说了,来一起看看详细介绍: MongoDB存储 在这里我们来看一下Python3下Mongo ...

- web项目中url-pattern改成'/'后,js、css、图片等静态资源(404)无法访问问题解决办法

感谢http://blog.csdn.net/this_super/article/details/7884383的文章 1.增加静态资源url映射 如Tomcat, Jetty, JBoss, Gl ...

- Hibernate中两种获取Session的方式

转自:https://www.jb51.net/article/130309.htm Session:是应用程序与数据库之间的一个会话,是hibernate运作的中心,持久层操作的基础.对象的生命周期 ...

- 使用AES128加密字符串

import lombok.extern.slf4j.Slf4j; import org.apache.commons.codec.binary.Base64; import org.apache.c ...

- windows下patch

经常在网上看到有人发布patch文件来更新他们的开源代码,例如cegui.ogre等都使用这种形式来修bug或者增加一些小功能.但是,我们下载到的patch文件,貌似是linux/unix的diff工 ...

- Redis的相关命令

Redis的相关命令 redis程序的命令 /usr/bin/redis-benchmark /usr/bin/redis-check-aof /usr/bin/redis-check-rdb /us ...