SystemVerilog Assertion 设计、调试、测试总结(3)

上两篇主要是讲述断言的概念,基本语法,总结等等

这一篇主要是以PPT的形式展示各个场景下关于断言的应用。

为了在设计中加入断言的功能,因此需要写一个DUT。如下:

`define true

`define free (a && b && c && d) module assertion(

input clk,

input rst_n

); reg a = 'b0 ;

reg b = 'b0 ;

reg c = 'b0 ;

reg d = 'b0 ;

reg e = 'b0 ;

reg f = 'b0 ;

reg start = 'b0 ;

reg stop = 'b0 ; always @(posedge clk)

begin

a <= $urandom_range(,);

b <= $urandom_range(,);

c <= $urandom_range(,);

d <= $urandom_range(,);

e <= $urandom_range(,);

f <= $urandom_range(,);

start <= $urandom_range(,);

stop <= $urandom_range(,);

end assign state = {a,b,c,d};

assign bus = {a,b,c,d}; `ifdef SIM_ASSERTION_ON

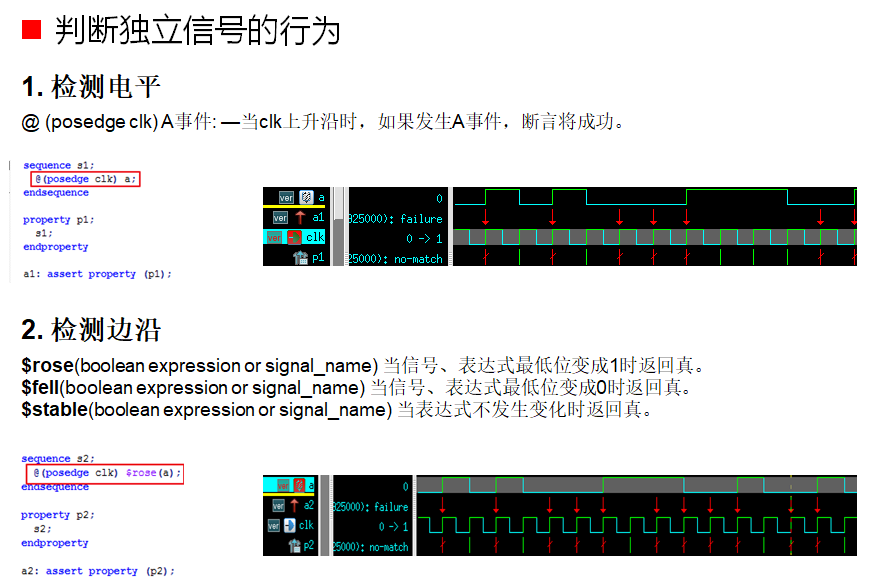

//a1

sequence s1;

@(posedge clk) a;

endsequence property p1;

s1;

endproperty a1: assert property (p1); //a2

sequence s2;

@(posedge clk) $rose(a);

endsequence property p2;

s2;

endproperty a2: assert property (p2); //a3

property p3;

@(posedge clk) a || b;

endproperty a3: assert property (p3); //a4

sequence s4;

@(posedge clk) a ## b;

endsequence property p4;

s4;

endproperty a4: assert property (p4); //a5

property p5;

@(posedge clk) a ## b;

endproperty a5:assert property(p5); //a6

sequence s6;

@(posedge clk) a ## b;

endsequence property p6;

not s6;

endproperty a6: assert property(p6); //a7

property p7;

@(posedge clk) a ## b;

endproperty a7: assert property (p7)

$display("Property p7 successed\n");

else

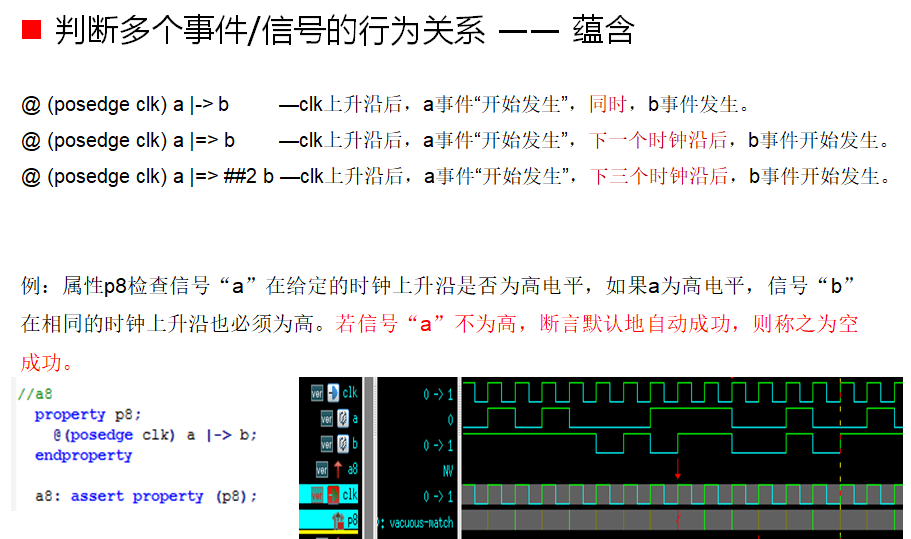

$display("Property p7 failed\n"); //a8

property p8;

@(posedge clk) a |-> b;

endproperty a8: assert property (p8); //a9

property p9;

@(posedge clk) a |=> b;

endproperty a9: assert property (p9); //a10

property p10;

@(posedge clk) a |-> ## b;

endproperty a10: assert property (p10); //a11

sequence s11a;

@(posedge clk)(a && b) ## c;

endsequence sequence s11b;

@(posedge clk) ## !d;

endsequence property p11;

s11a |-> s11b;

endproperty a11: assert property (p11); //a12

property p12;

@(posedge clk) ( a&&b ) |-> ## [:] c;

endproperty a12: assert property (p12); //a13

property p13;

@(posedge clk) ( a&&b ) |-> ## [:] c;

endproperty a13: assert property (p13); //a14

property p14;

@(posedge clk) a |-> ##[:$] b ##[:$] c;

endproperty a14: assert property (p14); //a15

sequence s15a;

@(posedge clk) a ## b;

endsequence sequence s15b;

@(posedge clk) c ## d;

endsequence property p15a;

s15a |=> s15b;

endproperty property p15b;

s15a.ended |-> ## s15b.ended;

endproperty a15a: assert property (p15a);

a15b: assert property (p15b); //a17

property p17;

@(posedge clk) c ? d == a : d == b;

endproperty a17: assert property(p17); //a18

sequence s18a;

@(posedge clk) a ## b;

endsequence sequence s18a_ext;

@(posedge clk) a ## b ## `true;

endsequence sequence s18b;

@(posedge clk) c ## d;

endsequence property p18;

@(posedge clk) s18a.ended |-> ## s18b.ended;

endproperty property p18_ext;

@(posedge clk) s18a_ext.ended |-> ## s18b.ended;

endproperty a18: assert property (p18);

a18_ext: assert property (p18_ext); //a19

property p19;

@(posedge clk) (c && d) |-> ($past((a&&b), ) == 'b1);

endproperty a19: assert property (p19); //a20

property p20;

@(posedge clk) (c && d) |-> ($past ( ( a&&b ), , e) == 'b1);

endproperty a20: assert property (p20); //a21

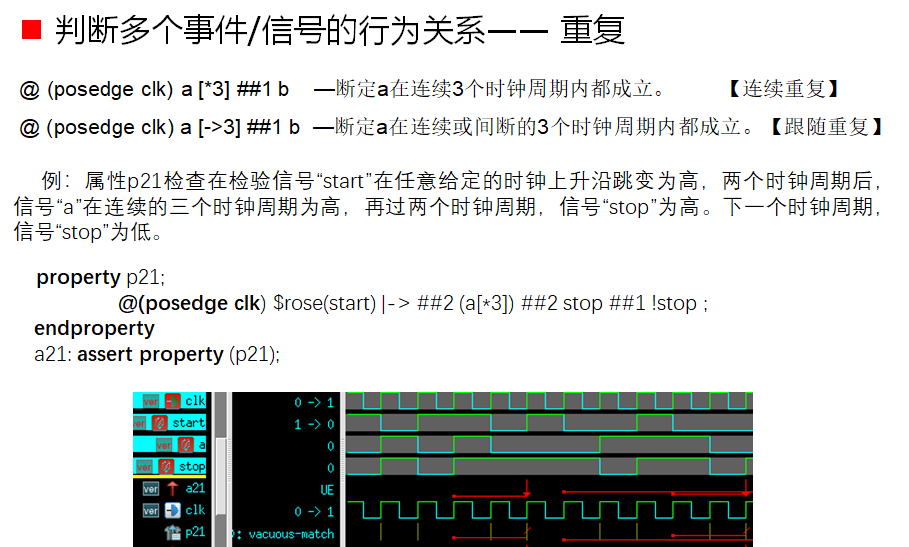

property p21;

@(posedge clk) $rose(start) |-> ## (a[*]) ## stop ## !stop ;

endproperty a21: assert property (p21); //a22

property p22;

@(posedge clk) $rose(start) |-> ## ((a ## b) [*]) ## stop ;

endproperty a22: assert property (p22); //a23

property p23;

@(posedge clk) $rose(start) |-> ## ((a ##[:] b) [*]) ## stop ;

endproperty

a23: assert property (p23); //a24

property p24;

@(posedge clk) $rose(start) |-> ## (a [* : $]) ## stop ;

endproperty a24: assert property (p24); //a25

property p25;

@(posedge clk) $rose(start) |-> ## (a [->]) ## stop ;

endproperty a25: assert property (p25); //a26

property p26;

@(posedge clk) $rose(start) |-> ## (a [=]) ## stop ## !stop;

endproperty a26: assert property (p26); //a27

sequence s27a;

@(posedge clk) a ##[:] b;

endsequence sequence s27b;

@(posedge clk) c ##[:] d;

endsequence property p27;

@(posedge clk) s27a and s27b ;

endproperty a27: assert property(p27); //a28

sequence s28a;

@(posedge clk) a ##[:] b;

endsequence sequence s28b;

@(posedge clk) c ##[:] d;

endsequence property p28;

@(posedge clk) s28a intersect s28b ;

endproperty a28: assert property(p28); //a29

sequence s29a;

@(posedge clk) a ##[:] b;

endsequence sequence s29b;

@(posedge clk) c ##[:] d;

endsequence property p29;

@(posedge clk) s29a or s29b ;

endproperty a29: assert property(p29); //a30

sequence s30a;

@(posedge clk) a ##[:] b;

endsequence sequence s30b;

@(posedge clk) c ##[:] d;

endsequence property p30;

@(posedge clk) first_match (s30a or s30b) ;

endproperty a30: assert property(p30); //a31

property p31;

@(posedge clk) $fell(start) |->

(!start) throughout

(## ( !a && !b ) ## ( c[->] ) ## ( a&&b ) );

endproperty a31: assert property(p31); //a32

sequence s32a;

@(posedge clk)

(( !a && !b ) ## ( c[->] ) ## ( a&&b ) );

endsequence sequence s32b;

@(posedge clk)

$fell(start) ## [:] $rose(start);

endsequence sequence s32;

@(posedge clk)

s32a within s32b;

endsequence property p32;

@(posedge clk)

$fell(start) |-> s32;

endproperty a32: assert property(p32); //a33

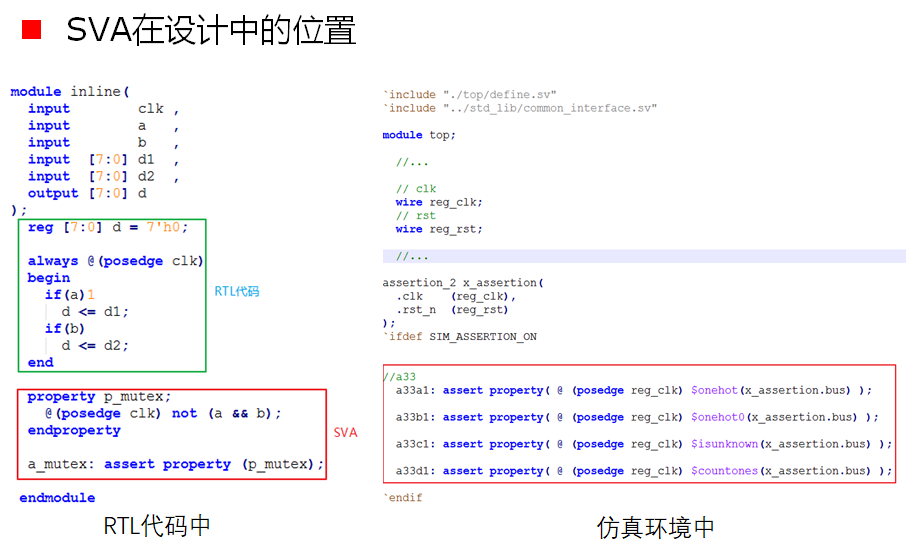

a33a: assert property( @ (posedge clk) $onehot(state) ); a33b: assert property( @ (posedge clk) $onehot0(state) ); a33c: assert property( @ (posedge clk) $isunknown(bus) ); a33d: assert property( @ (posedge clk) $countones (bus) ); //a34

property p34;

@(posedge clk)

disable iff (rst_n)

$rose (start) |-> a[=] ## b[=] ## !start ;

endproperty //a35

property p35;

(@(posedge clk) [*:] intersect(a ##[:$] b ##[:$] c));

endproperty a35: assert property(p35); //a36

property arb (a,b,c,d);

@(posedge clk) ($fell (a) ##[:] $fell(b) ) |->

## ($fell (c) && $fell(d) ) ##

(!c && !d) [*] ## (c&&d) ## b;

endproperty a36_1: assert property(arb(a1,b1,c1,d1));

a36_2: assert property(arb(a2,b2,c2,d2));

a36_3: assert property(arb(a3,b3,c3,d3)); //a37

property p_nest;

@(posedge clk) $fell (a) |->

## (!b && !c && !d ) |->

## [:] `free;

endproperty a_nest: assert property(p_nest); property p_nest1;

@(posedge clk) $fell (a) ## (!b && !c && !d )

|-> ## [:] `free;

endproperty a_nest1: assert property(p_nest1); //a_if_else

property p_if_else;

@(posedge clk) ($fell (start)##(a || b))|->

if (a)

(c[->] ## e)

else

(d[->] ## f);

endproperty a_if_else: assert property(p_if_else); `endif endmodule

通过运行Makefile脚本,调用VCS以及Verdi命令来实现以及查看断言的波形。

总结如下:

目录

1、概述

2、断言的常用语法

3、断言的应用

至此,关于断言的知识点全部更新完全,有疑问的欢迎交流。

SystemVerilog Assertion 设计、调试、测试总结(3)的更多相关文章

- SystemVerilog Assertion 设计、调试、测试总结(1)

暑期实习两个月的其中一个任务是:如何在设计中加入断言?以及断言的基本语法.三种应用场景下的断言(如FIFO.FSM.AXI4-lite总线).参考书籍:<System Verilog Asser ...

- SystemVerilog Assertion 设计、调试、测试总结(2)

上一篇博客主要写了SVA的基本语法(详细),这一篇主要写SVA语法总结,以及如何查看SVA波形等. 断言assertion被放在verilog设计中,方便在仿真时查看异常情况.当异常出现时,断言会报警 ...

- systemverilog assertion

1.一般是单独写一个module 里面放assertion, 然后在验证平台顶层和RTL的实例化bind起来 2. |->表示直接进行判断,|=>表示下一拍判断,一般一个断言最好只写一 ...

- [连载]《C#通讯(串口和网络)框架的设计与实现》- 0.前言

目 录 前言 前言 刚参加工作,使用过VB.VC开发软件,随着C#的崛起,听说是C++++,公司决定以后开发软件使用C#,凭借在 ...

- 在线调试lua原型设计

在规模日益增长的软件项目开发中, 如何有效的进行代码调试成为影响开发效率的致命因素之一.在当今网络游戏项目中, lua几乎成了项目脚本的标配.编译型的语言, 诸如C++, 都有良好的ide支持调试.而 ...

- SystemVerilog的历史

随着软件的功能需求越来越复杂,C语言不足以解决现有的问题,于是C++被发明了:C++的指针漫天飞,对内存的处理过于复杂,于是Java被发明了:芯片的功能不断地扩大,Verilog不足以应对日益复杂的芯 ...

- Chrome 控制台console的用法(学了之后对于调试js可是大大有用的哦)

大家都有用过各种类型的浏览器,每种浏览器都有自己的特色,本人拙见,在我用过的浏览器当中,我是最喜欢Chrome的,因为它对于调试脚本及前端设计调试都有它比其它浏览器有过之而无不及的地方.可能大家对co ...

- 痞子衡嵌入式:飞思卡尔Kinetis开发板OpenSDA调试器那些事(上)- 背景与架构

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家介绍的是飞思卡尔Kinetis MCU开发板板载OpenSDA调试器(上篇). 众所周知,嵌入式软件开发几乎离不开调试器,因为写一个稍有代码规模 ...

- JS调试技巧

大家都有用过各种类型的浏览器,每种浏览器都有自己的特色,本人拙见,在我用过的浏览器当中,我是最喜欢Chrome的,因为它对于调试脚本及前端设计调试都有它比其它浏览器有过之而无不及的地方.可能大家对co ...

随机推荐

- ubuntu apache 通过端口新建多个站点

cd /etc/apache2/sites-available 最近的虚拟机没绑定域名,所以呢,就先用域名加端口新建几个站点用着 1. vim /etc/apapche2/apapche2.conf ...

- uWSGI配置参数释义

uWSGI配置参数释义 socket : 地址和端口号,例如:socket = 127.0.0.1:50000 processes : 开启的进程数量 workers : 开启的进程数量,等同于pro ...

- CodeForces-220B Little Elephant and Array

小象喜欢玩数组.他有一个数组a,由n个正整数组成,从1到n进行索引.让我们用索引i表示数字ai. 此外,小象对数组还有m个查询,每个查询的特征是一对整数lj和rj(1 ≤ lj ≤ rj ≤ n).对 ...

- Hibernate学习(七)

Hibernate缓存 1.一级缓存:Session 级别的缓存 2.二级缓存: SessionFactory 级别的缓存 3.查询缓存:需二级缓存的支持,查询缓存依赖二级缓存 一级缓存 1.依赖于 ...

- IPSec的高可用性技术

IPSec VPN的高可用性技术:①.DPD(Dead Peer Detection)对等体检测 ——旨在检查有问题的IPSec VPN网络,并快速的切换到备 ...

- PostgreSQL数据库-分页sql--offset

select * from users order by score desc limit 3;--取成绩的前3名=====select * from users order by score des ...

- Python学习第二十一课——Mysql 对数据库的基本操作

数据库操作(DDL) 在数据库下创建表(create_table) 创建表代码块: CREATE TABLE employee( id TINYINT PRIMARY KEY auto_increme ...

- Educational Codeforces Round 73 (Rated for Div. 2)F(线段树,扫描线)

这道题里线段树用来区间更新(每次给更大的区间加上当前区间的权重),用log的复杂度加快了更新速度,也用了区间查询(查询当前区间向右直至最右中以当前区间端点向右一段区间的和中最大的那一段的和),也用lo ...

- rem布局,在用户调整手机字体大小/用户调整浏览器字体大小后,布局错乱问题

一.用户调整浏览器字体大小,影响的是从浏览器打开的web页. 浏览器设置字体大小,影响浏览器打开的页面.通过js可控制用户修改字体大小,使页面不受影响. (function(doc, win) { / ...

- Vue专题系列

一. 简介 1. 说明 Vue (读音 /vjuː/,类似于 view) 是一套用于构建用户界面的渐进式框架.与其它大型框架不同的是,Vue 被设计为可以自底向上逐层应用.Vue 的核心库只关注视图 ...