Verilog代码和FPGA硬件的映射关系(五)

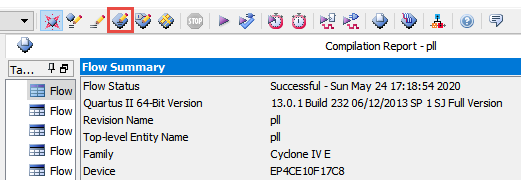

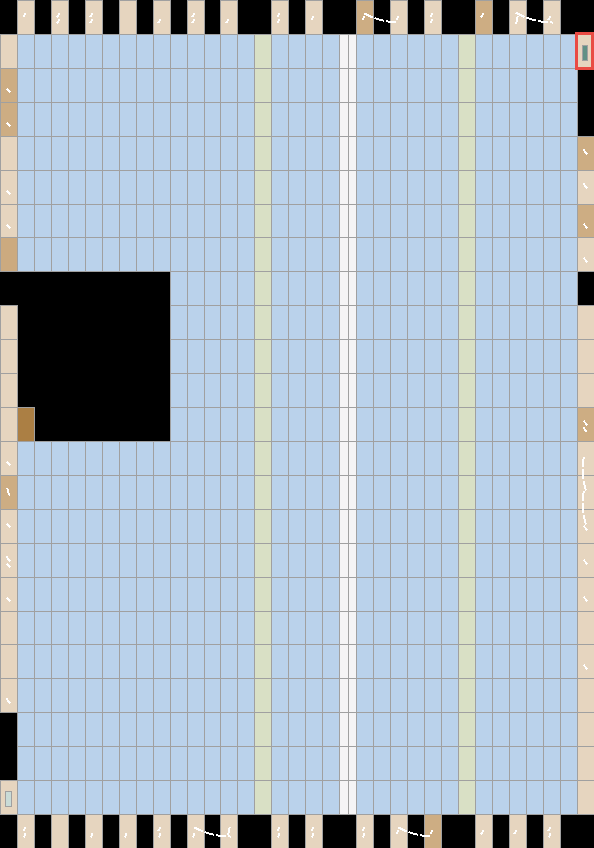

既然我们可以指定寄存器放在IOB内,那我们同样也可以指定PLL的位置。首先要确保我们有多个PLL才行。如图1所示,我们所使用的EP4CE10F17C8芯片刚好有两个。

图 1

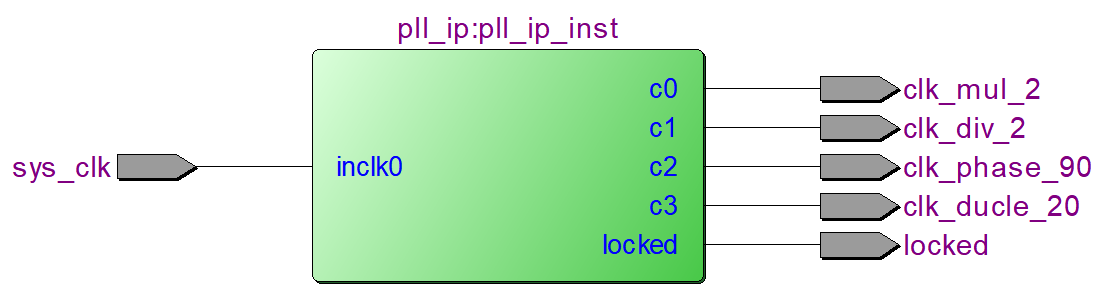

为了演示这个例子,我们使用pll工程,RTL代码如下所示:

//--------------------------------------------------

module pll(

input wire sys_clk , //系统时钟50MHz output wire clk_mul_2 , //系统时钟经过2倍频后的时钟

output wire clk_div_2 , //系统时钟经过2分频后的时钟

output wire clk_phase_90 , //系统时钟经过相移90°后的时钟

output wire clk_ducle_20 , //系统时钟变为占空比为20%的时钟

output wire locked //检测锁相环是否已经锁定,只有该信号为高时输出的时钟才是稳定的 ); //------------------------pll_ip_inst------------------------

pll_ip pll_ip_inst(

.inclk0 (sys_clk ), //input inclk0 .c0 (clk_mul_2 ), //output c0

.c1 (clk_div_2 ), //output c1

.c2 (clk_phase_90 ), //output c2

.c3 (clk_ducle_20 ), //output c3

.locked (locked ) //output locked

); endmodule

//-------------------------------------------------

代码编写完后依然需要点击“Start Analysis & Synthesis”图标进行分析和综合。然后双击“Netlist Viewers”下的“RTL Viewer”查看RTL视图。

图 2

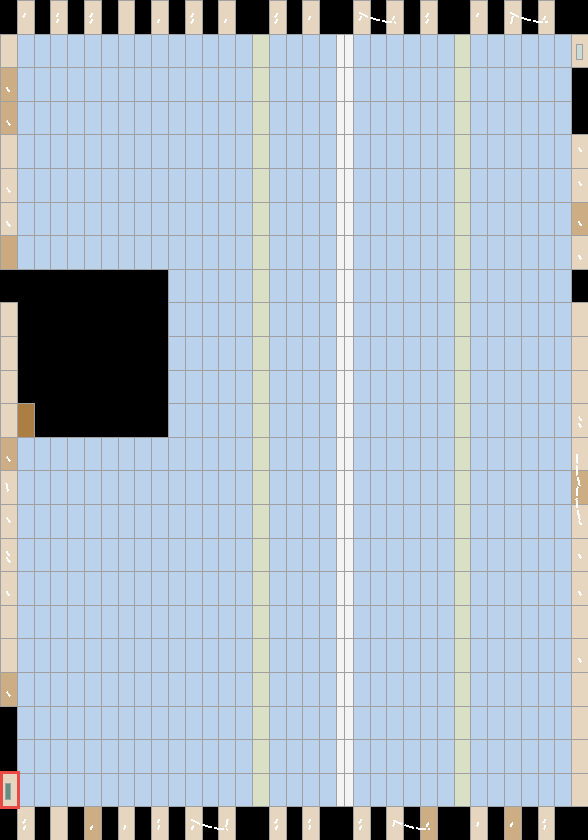

点击“Start Compilation”图标全编译进行布局布线,然后打开Chip Planner视图。Chip Planner打开后的界面如图3所示,我们可以看到在版图模型中左下角有一块颜色变深的区域,与之形成鲜明对比的是右上角颜色没有变深的位置,这就是我们FPGA芯片中两个PLL的位置,而颜色变深的区域说明资源被占用。

图 3

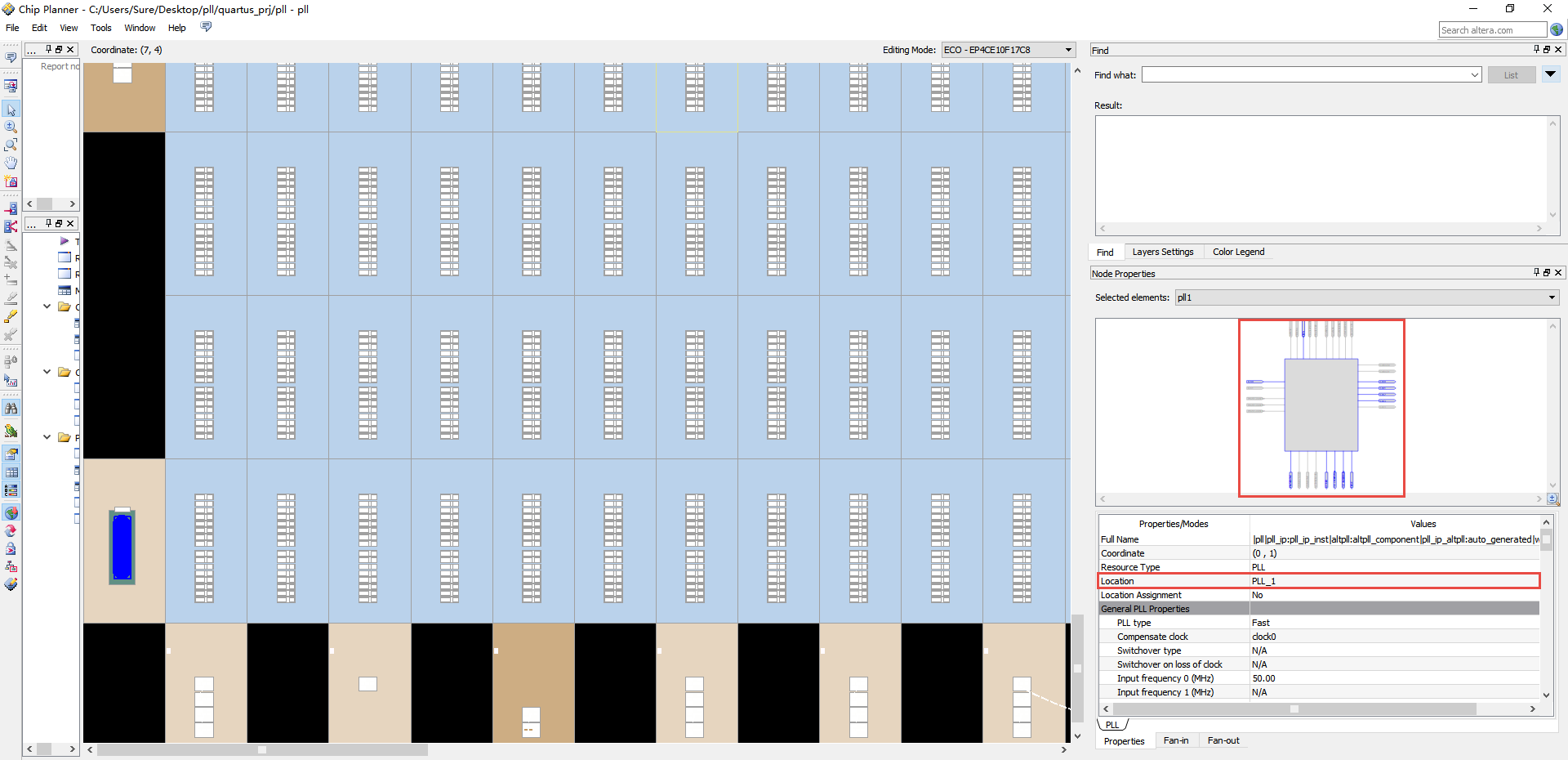

放大并点击该PLL,如图4所示,可以在右侧看到该PLL的结构图中显示的部分蓝色高亮信号,下面“Location”则显示了该PLL的名字为“PLL_1”。

图 4

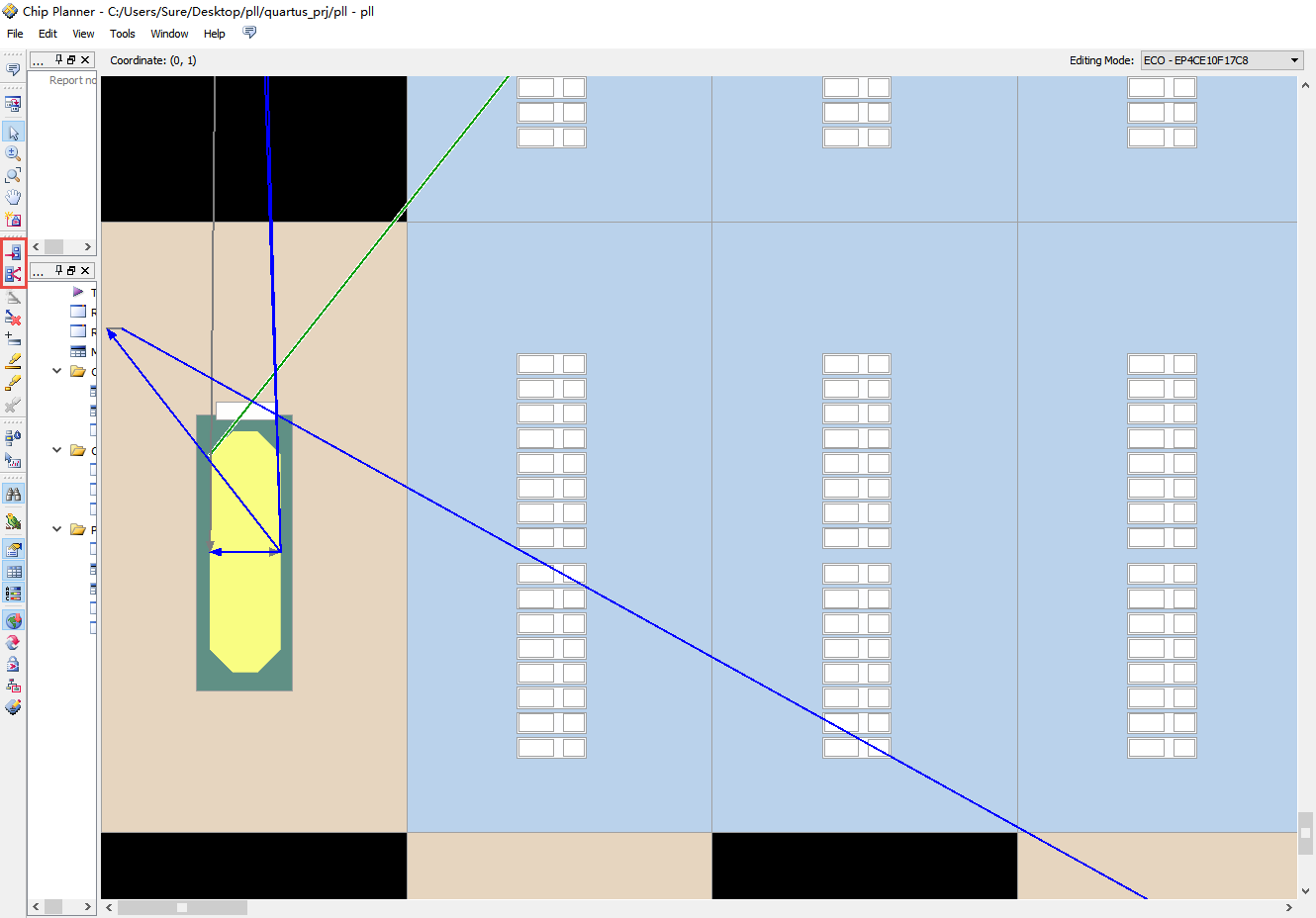

如图5所示,选中该PLL后点击左侧的图标显示扇入扇出线路径,可以看到PLL在芯片内的连接关系。

图 5

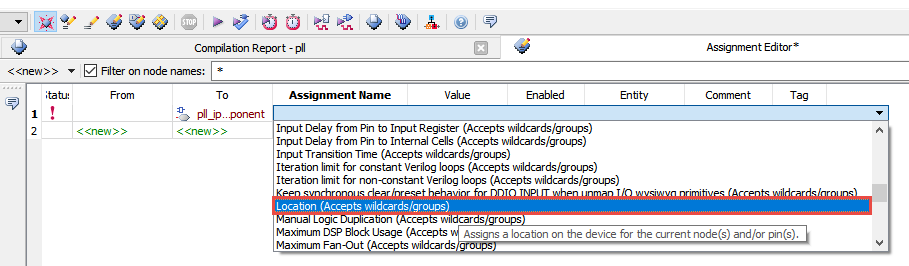

如图6所示,我们回到工程界面点击“Assignment Editor”图标来约束PLL的位置。

图 6

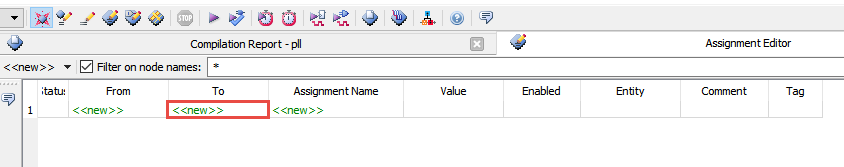

如图7所示,在打开的“Assignment Editor”界面中点击“To”下面的“<<new>>”添加要约束的项。

图 7

在打开的“Node Finder”界面中我们找到信号的输入key_in,如图8所示,根据序号顺序,在①处的“Named :”选项框中输入“*pll*”,点击 ②处的“List”,在③处的“Node Found :”列表中就会列出名为altpll:altpll_component的信号,双击③处的altpll:altpll_component 信号或点击图标④,altpll:altpll_component信号就被添加到⑤处的“Selected Nodes:”中了。如果我们想取消⑤处选择的信号则在“Selected Nodes:”选中该信号后点击图标⑥即可。设置完毕后点击“OK”退出。

图 8

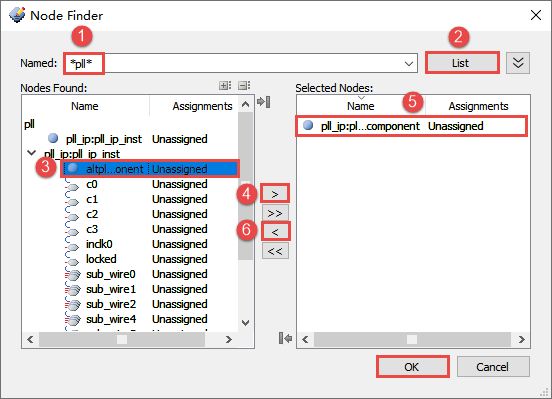

如图9所示,设置“Assignment Name”,下拉列表找到“Location(Accepts wildcards/groups)”,这是设置位置的约束。

图 9

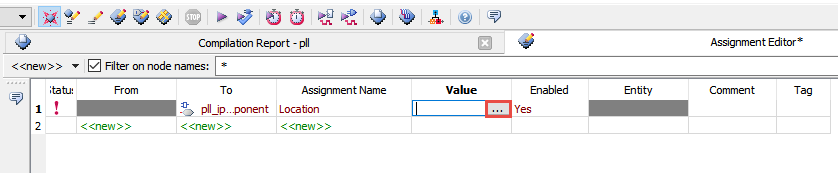

如图10所示,点击“Value”下的“...”。

图 10

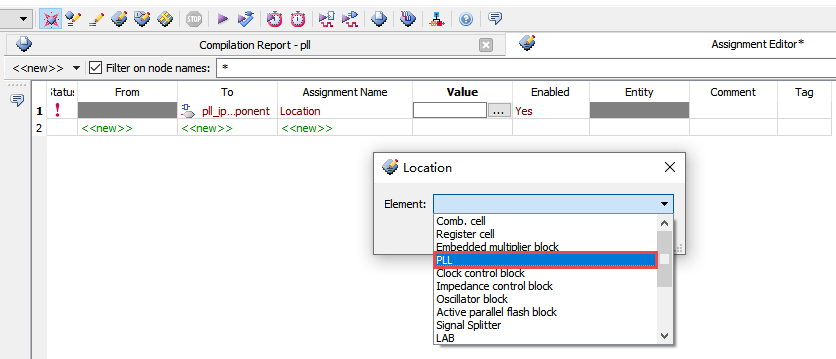

如图11所示,在弹出的“Location”对话框中的“Element:”选择“PLL”。可以看到在这里我们还可以设置其他元素的位置。

图 11

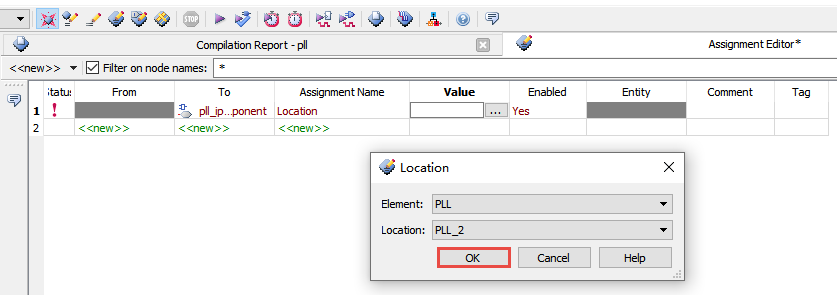

如图12所示,“Location:”选择“PLL_2”。

图 12

如图13所示,“Location”对话框设置完毕后点击“OK”。

图 13

全部设置完成后的结果如图14所示。

图 14

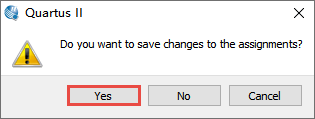

点击“Start Compilation”图标全编译进行布局布线,否则无法重新映射资源。此时会弹出如所示的对话框,提示是否要保存更改,选择“Yes”后会执行布局布线。

图 15

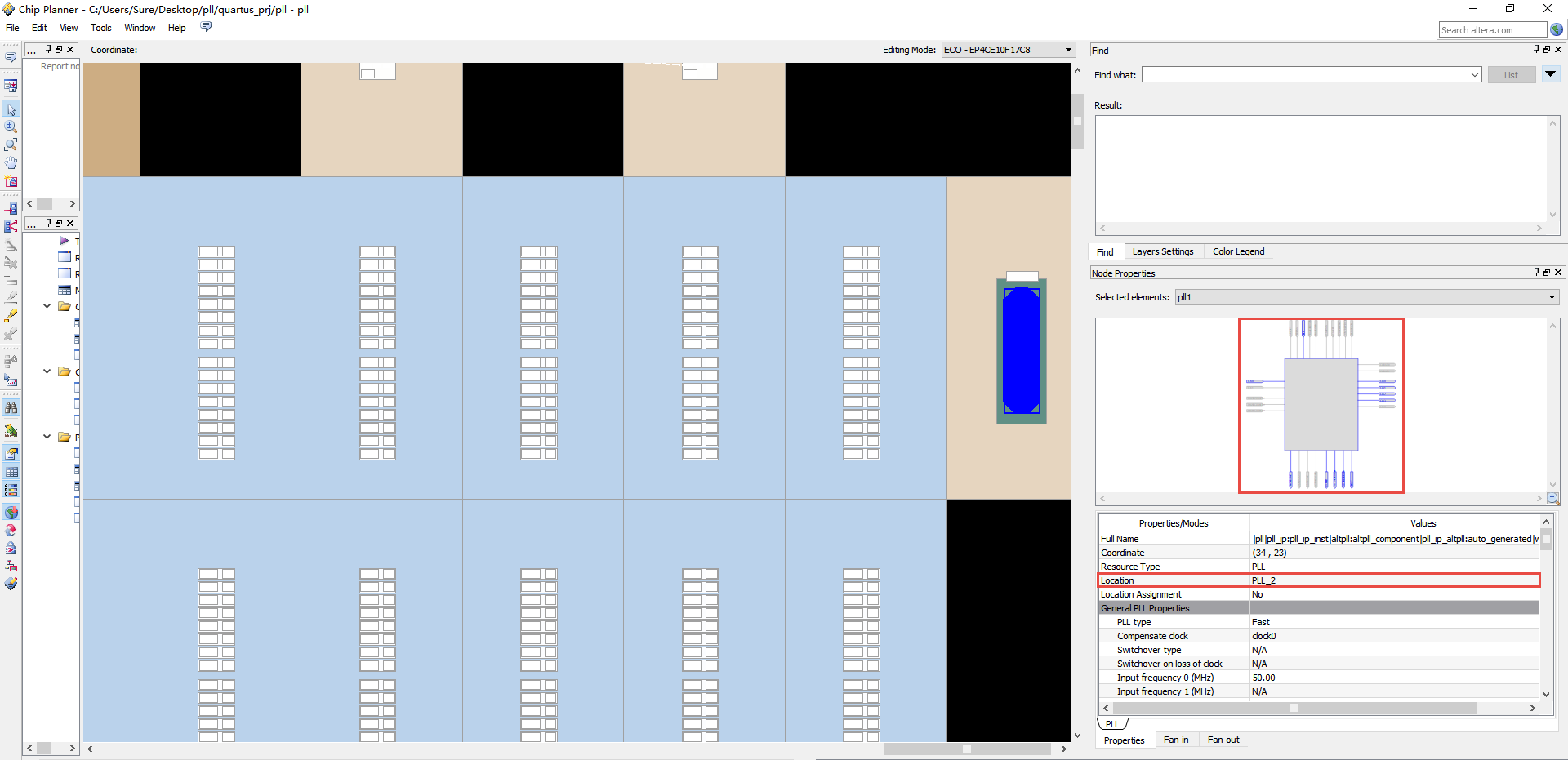

当布局布线重新完成映射后我们再来看看Chip Planner视图,如图16所示,我们可以发现在版图模型的右上角一块颜色变深的区域,与左下颜色没有变深的位置形成鲜明的对比,颜色变深的区域说明资源被占用。

图 16

放大并点击该PLL,如图17所示,可以在右侧看到该PLL的结构图中显示的部分蓝色高亮信号,下面“Location”则显示了该PLL的名字为“PLL_2,说明已经成功映射上了。

图 17

如图18所示,选中该PLL后点击左侧的图标显示扇入扇出线路径,可以看到PLL在芯片内的连接关系。

图 18

修改PLL的映射位置意义何在呢?当我们的时序在某些情况下不好的时候就可以通过修改PLL的映射位置来调整时序,以实现时序的收敛。

欢迎加入FPGA技术学习交流群,本群致力于为广大FPGAer提供良好的学习交流环境,不定期提供各种本行业相关资料!QQ交流群号:450843130

Verilog代码和FPGA硬件的映射关系(五)的更多相关文章

- Verilog代码和FPGA硬件的映射关系(三)

组合逻辑和FPGA之间的映射关系我们知道了,那时序逻辑和FPGA之间又是一种怎样的映射关系呢?我们就以前面寄存器章节的例子来向大家说明,也一同把当时为什么用异步复位更节约资源的原因告诉大家.我们先来看 ...

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- Verilog代码和FPGA硬件的映射关系(二)

大家可能会有这样的疑问,我们编写的Verilog代码最终会在FPGA上以怎样的映射关系来实现功能呢?我们以一个最简单的组合逻辑与门为例来向大家说明.RTL代码如下所示: //------------- ...

- Verilog代码和FPGA硬件的映射关系(四)

其实在FPGA的开发中理想情况下FPGA之间的数据要通过寄存器输入.输出,这样才能使得延时最小,从而更容易满足建立时间要求.我们在FPGA内部硬件结构中得知,IOB内是有寄存器的,且IOB内的寄存器比 ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- ASP.NET Core的路由[1]:注册URL模式与HttpHandler的映射关系

ASP.NET Core的路由是通过一个类型为RouterMiddleware的中间件来实现的.如果我们将最终处理HTTP请求的组件称为HttpHandler,那么RouterMiddleware中间 ...

- hibernate笔记--使用注解(annotation)方式配置单(双)向多对一的映射关系

前面几篇都是介绍的用配置文件来实现实体类到数据库表的映射,这种方式是比较麻烦的,每一个pojo类都需要写一个相应的*.hbm.xml,无疑增加了很多代码量,不过也有优点就是利于维护,为了方便开发,Hi ...

- hibernate笔记--单(双)向的多对多映射关系

在讲单向的多对多的映射关系的案例时,我们假设我们有两张表,一张角色表Role,一张权限表Function,我们知道一个角色或者说一个用户,可能有多个操作权限,而一种操作权限同时被多个用户所拥有,假如我 ...

随机推荐

- ZLEXCOUNT key min max

1 简介 ZLEXCOUNT 命令用于计算有序集合中指定成员之间的成员数量. 2 语法 2.1 完整示例 zlexcount zset [member1 [member5 2.2 说明 指令 是否必须 ...

- JVM调优方法笔记

1.性能工具介绍 jvisualvm jmap jstat jstack/threaddump jprofiler jmeter 2.性能调优4步骤 重现问题 定位问题 模拟问题 解决问题 http: ...

- JavaScript实现插入排序

一.插入排序简介: 想象我们斗地主,摸排阶段,手里的牌都按照从小到大排序.如果每摸一张牌,我们就把他插入合适的位置,使得它比后面位置的牌小,比前面位置的牌大或者相等. 类似这样的一种排序方法就是插入排 ...

- 瑞幸咖啡还是星巴克,一杯下午茶让我明白 设计模式--模板方法模式(Template Method Pattern)

简介 Define the skeleton of an algorithm in an operation,deferring some steps to subclasses.Template M ...

- FZU 1894 志愿者选拔

Problem 1894 志愿者选拔 Accept: 2308 Submit: 7003 Time Limit: 1500 mSec Memory Limit : 32768 KB Problem D ...

- Jenkins 部署(基于 Linux)

1.安装 JDK 我不列出来了,自行百度 java -version 2.安装 tomcat (1)创建目录 tomcat8 (2)导入 tomcat 文件到 tomcat8 录中并解压 (3)启动 ...

- Hello World的五十种不同实现方法!!!!!

我们作为一名程序员,职业生涯中至少完成了一个“Hello, World!“程序.当我们学习一门新的语言时,“Hello, World!“通常是我们所写的第一个程序.程序员一般也都会使用多门语言,甚至有 ...

- springdata jpa基本注解

Springdata jpa的基本注解 1:@Entity @Entity注解用在实体类声明语句前,说明该Java类为实体类,将映射到指定的数据库表. 2:@Table @Table注解用在当实体类与 ...

- 08_CSS入门和高级技巧(6)

排查错误 Chrome浏览器的审查功能. 错误1:选择器写错了,压根没有选择上: 如果写了一个错误的选择器, <style type="text/css"> dvi p ...

- LeetCode--Unique Morse Code Words && Flipping an Image (Easy)

804. Unique Morse Code Words (Easy)# International Morse Code defines a standard encoding where each ...