基于FPGA的三段式状态机

- 状态机分类:

通常, 状态机的状态数量有限, 称为有限状态机(FSM) 。由于状态机所有触发器的时钟由同一脉冲边沿触发, 故也称之为同步状态机。 根据状态机的输出信号是否与电路的输入有关分为 Mealy 型状态机和 Moore 型状态机。

Mealy 型状态机:

电路的输出信号不仅与电路当前状态有关, 还与电路的输入有关。

Moore 型状态机:

电路的输出仅仅与各触发器的状态, 不受电路输入信号影响或无输入。

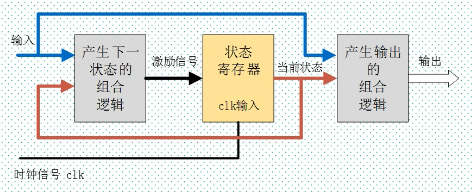

三段式状态机的一般结构:

1)利用参数定义语句 parameter 描述状态机各个状态名称, 即状态编码。一般采用独热码。

2)用时序always模块,格式化描述次态寄存器(下一个状态的寄存器)迁移到现态寄存器。

3)用组合逻辑always模块,描述状态转移条件判断或者状态转移规律。

4)同步时序always模块,格式化描述各个状态的输出。

实现代码:

- module test(

- input clk,

- input rst_n,

- output reg out

- );

- //reg define

- reg q;

- //第一步,状态声明和状态编码

- reg [:] current_state;

- reg [:] next_state;

- parameter [:] S0='b0000;

- parameter [:] S1='b0010;

- parameter [:] S2='b0100;

- parameter [:] S3='b1000;

- //第二部,时序逻辑: 描述状态转换,格式固定

- always@(posedge clk)

- begin

- if(!rst_n)

- current_state <= ;

- else

- current_state <= next_state;

- end

- //第三部,组合逻辑: 描述状态转移条件,即只考虑状态之间的跳转,也就是说各个状态机之间跳转关系。

- always @ (current_state or .... ) //电平触发,

- begin

- next_state = x; //要初始化,使得系统复位后能进入正确的状态

- case(current_state)

- S0: if(...)

- next_state = S1; //阻塞赋值

- else

- ......

- S1: if(...)

- next_state = S2; //阻塞赋值

- else

- ......

- .

- .

- .

- default : .....

- endcase

- end

- //第四部,用时序always块输出逻辑: 让输出 out, 经过寄存器 q 锁存后输出, 消除毛刺

- always@(posedge clk)

- begin

- if(!rst_n)

- out<='b0;

- else

- begin

- case(current_state)

- S0:

- out<='b0;

- S1:

- out<='b1;

- .

- .

- .

- default : ....

- endcase

- end

- end

- assign q = ou; //让输出 out, 经过寄存器 q 锁存后输出, 消除毛刺

- endmodule

基于FPGA的三段式状态机的更多相关文章

- FPGA三段式状态机的思维陷阱

用三段式描述状态机的好处,国内外各位大牛都已经说的很多了,大致可归为以下三点: 1.将组合逻辑和时序逻辑分开,利于综合器分析优化和程序维护; 2.更符合设计的思维习惯; 3.代码少,比一段式状态机更简 ...

- 简单三段式状态机实验2-LCD12864

此实验是在“基于I2C EPPRPM(AT24C02B) + LCD12864实验”基础上,把LCD模块里的一段式状态机改成三段式,I2C EPPROM模块暂时未改出来,一步一步来吧,改完后代码下载到 ...

- 简单三段式状态机实验1-SOS

一直想从一段式状态机切换到三段式状态机,从书上和网上不断搜寻三段式案例及方法,感觉很简单,就想拿之前做过的实验把一段式改成三段式,可是写起来并非那么简单,很棘手,改完后也没有成功,尤其状态机里面的计数 ...

- Verilog笔记.三段式状态机

之前都是用的一段式状态机,逻辑与输出混在一起,复杂点的就比较吃力了. 所以就开始着手三段式状态机. 组合逻辑与时序逻辑分开,这样就能简单许多了. 但是两者在思考方式上也有着很大的区别. 三段式,分作: ...

- 10010序列检测器的三段式状态机实现(verilog)

序列检测器是时序数字电路设计中经典的教学范例,夏宇闻的<verilog数字系统设计教程>一书中有这个例子,用verilog设计一个“10010”序列的检测器.看完后我觉得F和G两个状态多余 ...

- 三段式状态机 [CPLD/FPGA]

状态机的组成其实比较简单,要素大致有三个:输入,输出,还有状态. 状态机描述时关键是要描述清楚前面提高的几个状态机的要素,即如何进行状态转移:每个状态的输出是什么:状态转移是否和输入条件相关等. 有人 ...

- Verilog三段式状态机描述

时序电路的状态是一个状态变量集合,这些状态变量在任意时刻的值都包含了为确定电路的未来行为而必需考虑的所有历史信息. 状态机采用VerilogHDL语言编码,建议分为三个always段完成. 三段式建模 ...

- verilog 三段式状态机的技巧

三段式代码多,但是有时钟同步,延时少,组合逻辑跟时序逻辑分开并行出错少. (1)同步状态转移 (2)当前状态判断接下来的状态 (3)动作输出 如果程序复杂可以不止三个always .always ...

- (原创)Verilog三段式状态机

下面以上图一个简单的FSM说明三段式Verilog状态机范式: `timescale 1ns / 1ps module FSM( clk,rst_n, in1,in2, out1,out2, CS,N ...

随机推荐

- Java逆向工程(数据库表生成java类)

说起来倒是挺简单的,就是听着名字感觉挺高大上.逆向工程方式有很多,比如mybatis就提供了一个这样的工具mybatis-genderator,这个我反正是没用过只是听说过,以前在公司都是用公司写好的 ...

- Vue+elementUI build打包部署后字体图标丢失问题

错误描述:Vue+elementUI build打包部署后字体图标丢失,控制台显示文件element-icons.woff和element-icons.ttf文件404 错误展现: 控制台报错截图 ...

- 使用JavaScript获取前一周的日期

在开发当中遇到了一个关于echarts初始展示当前前7天的数据,正好记录一下如何获取前"n"天的日期, 返回时间格式:2020-02-02 // 返回前number天的日期格式为2 ...

- python读取配置文件报keyerror-文件路径不正确导致的错误

- 在其他模块使用反射读取配置文件报错,但是在反射模块中读取GetData.check_list又是正确的 反射模块如下: # get_data.py from API_AUTO.p2p_projec ...

- Thymeleaf模板笔记

1.常用标签: 使用thymeleaf模板,首要在html中引入: <html xmlns:th="http://www.thymeleaf.org"> 引入css.j ...

- mysql--sql_mode报错整理

1.在5.7版本以上mysql中使用group by语句进行分组时, 如果select的字段 , 不是完全对应的group by后面的字段 , 有其他字段 , 那么就会报这个错误 ERROR 1055 ...

- Python---10小结

因一边上班一边自学python,一旦忙起来,python就会放两天,可是2天后之前学的内容就会有点忘记. 今天把python的各种启动方法总结一下; 我的文档路径: ------- 1打开文件所在的c ...

- Jun

Contents 数据来源 代码演示 讨论 一.数据来源 为了节省时间,我直接用了官方所给的数据,分别是雄性和雌性小鼠的肝脏芯片数据 Female Data Male Data 二.代码演示 数据输入 ...

- C++走向远洋——63(项目二2、两个成员的类模板)

*/ * Copyright (c) 2016,烟台大学计算机与控制工程学院 * All rights reserved. * 文件名:text.cpp * 作者:常轩 * 微信公众号:Worldhe ...

- 学了C++不知道怎么搞后台开发?先看看这份学习路线吧!

作者:AJ 在去年结束的秋季招聘中,后台开发或服务器开发的岗位需求一度火热,甚至超过了算法岗.不少同学从诸神黄昏的算法岗战场上退下,转向更偏向工程能力的后台开发岗,从而造成后台开发岗位竞争的大爆发. ...