如何利用FPGA进行时序分析设计

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。

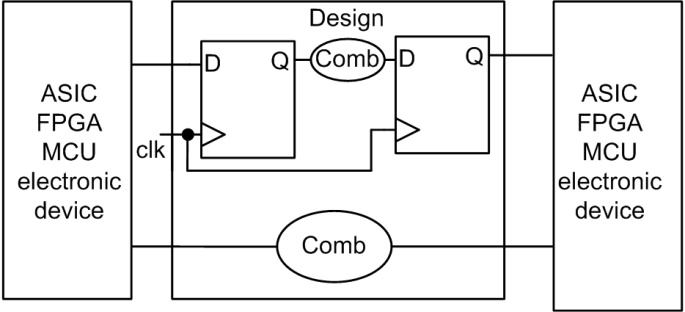

基本的电子系统如图 1所示,一般自己的设计都需要时序分析,如图 1所示的Design,上部分为时序组合逻辑,下部分只有组合逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析上半部分。在进行时序分析之前,需要了解时序分析的一些基本概念,如时钟抖动、时钟偏斜(Tskew)、建立时间(Tsu)、保持时间(Th)等。时序分析也就是分析每一个触发器(寄存器)是否满足建立时间/保持时间,而时序的设计的实质就是满足每一个触发器的建立时间/保持时间的要求。

图 1 基本的电子系统

一、时钟抖动和时钟偏斜

1.时钟抖动

时钟信号边沿变化的不确定时间称为时钟抖动,如图 2所示。一般情况下的时序分析是不考虑时钟抖动,如果考虑时钟抖动,则建立时间应该是Tsu+T1,保持时间应该是Th+T2。

图 2 时钟抖动时序图

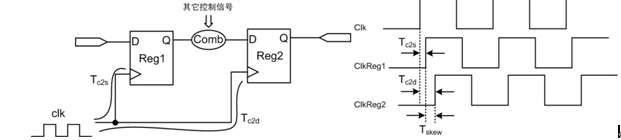

2.时钟偏斜

时序偏斜分析图如图 3所示。时钟的分析起点是源寄存器(Reg1),终点是目标寄存器(Reg2)。时钟在图中的结构中传输也会有延迟,时钟信号从时钟源传输到源寄存器的延时为Tc2s,传输到目标寄存器的延时为Tc2d。时钟网络的延时为Tc2s与Tc2d之差,即Tskew=Tc2d-Tc2s。

图 3 时钟偏斜时序图

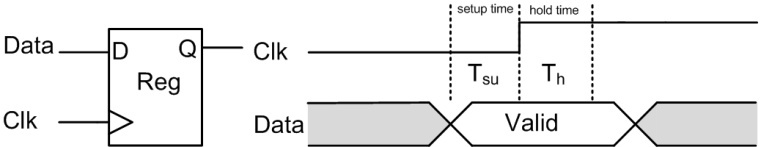

二、建立时间和保持时间

建立时间(Setup Time)常用Tsu表示,指的是在触发器的时钟信号上升沿到来以前,数据和使能信号稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器,使能信号无效,也就是说在这个时钟周期对数据的操作时无效的;保持时间(Hold Time)常用Th表示,指的是在触发器的时钟信号上升沿到来以后,数据和使能信号稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器,对数据的操作同样是无效的,使能信号无效。数据要能稳定传输,就必须满足建立时间和保持时间的关系,图 4标识了它们间的关系。

图 4 建立时间/操持时间的概念

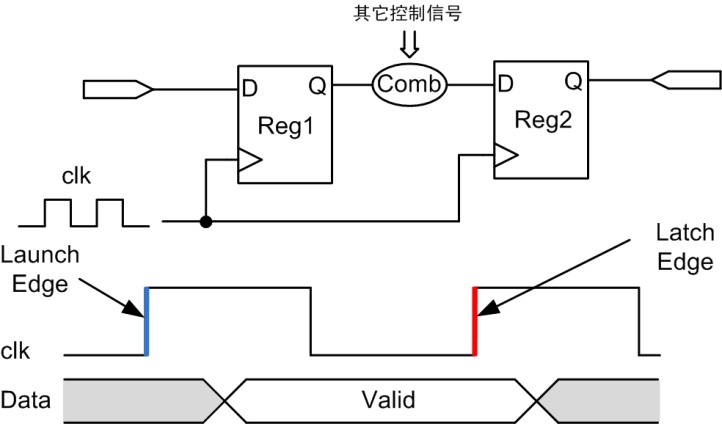

三、发送沿和捕获沿

(1)发送沿(Launch Edge):前级寄存器发送数据对应的时钟沿,是时序分析的起点;

(2)捕获沿(Latch Edge):后记寄存器捕获数据对应的时钟沿,是时序分析的终点。相对于launch Edge通常为一个时钟周期,但不绝对,如多周期。

“信号跳变抵达窗口”:对latch寄存器来说,从previous时钟对应的Hold Time开始,到current 时钟对应的Setup Time 结束。

“信号电平采样窗口”:对latch寄存器来说,从current时钟对应的Setup Time开始,到current时钟对应的Hold Time结束。

launch寄存器必须保证驱动的信号跳变到达latch寄存器的时刻处于“信号跳变抵达窗口”内,才能保证不破坏latch寄存器的“信号电平采样窗口”。

图 5 Launch Edge和Latch Edge

四、数据和时钟的时序分析

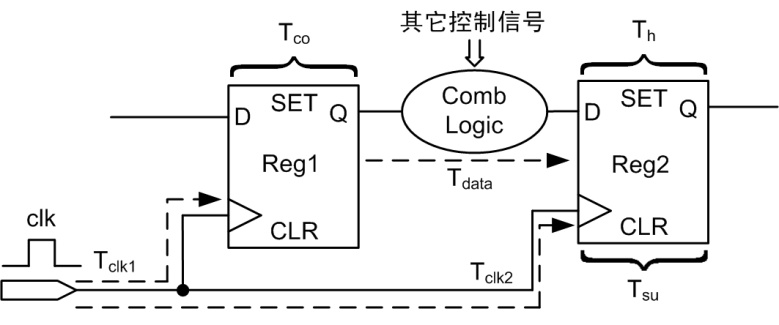

如图 6所示,为分析建立时间/保持时间的基本电路图。Tclk1为Reg1的时钟延时,Tclk2为Reg2的时钟延时,Tco为Reg1固有延时,Tdata为Reg1的到Reg2之间组合逻辑的延时,Tsu为Reg2的建立时间,Th为Reg2的保持时间,设时钟clk周期为T,这里分析数据的建立时间和保持时间。

图 6 基本电路图

1、建立时间的分析

如图 7所示,建立时间的分析是以第一个launch Edge为基准,在Latch Edge查看结果。建立时间的裕量(T为时钟周期):

Setup Stack = (T+Tclk2) – Tsu – (Tclk1+Tco+Tdata)

假设△T = Tclk2-Tclk1,则:

Setup Stack = (T+△T) – Tsu – (Tco+Tdata)

可见△T<0影响建立时间,使建立时间的要求更加苛刻。因此对于△T尽量避免,采用同步单时钟,并且尽量采用全局的时钟信号,这样△T几乎为0,,△T的影响几乎不存在,可以忽略不计。

如果建立时间的裕量Setup Stack小于0,则不满足建立时间,也就会产生不稳定态,并通过寄存器传输下去。

图 7 建立时间时序分析图

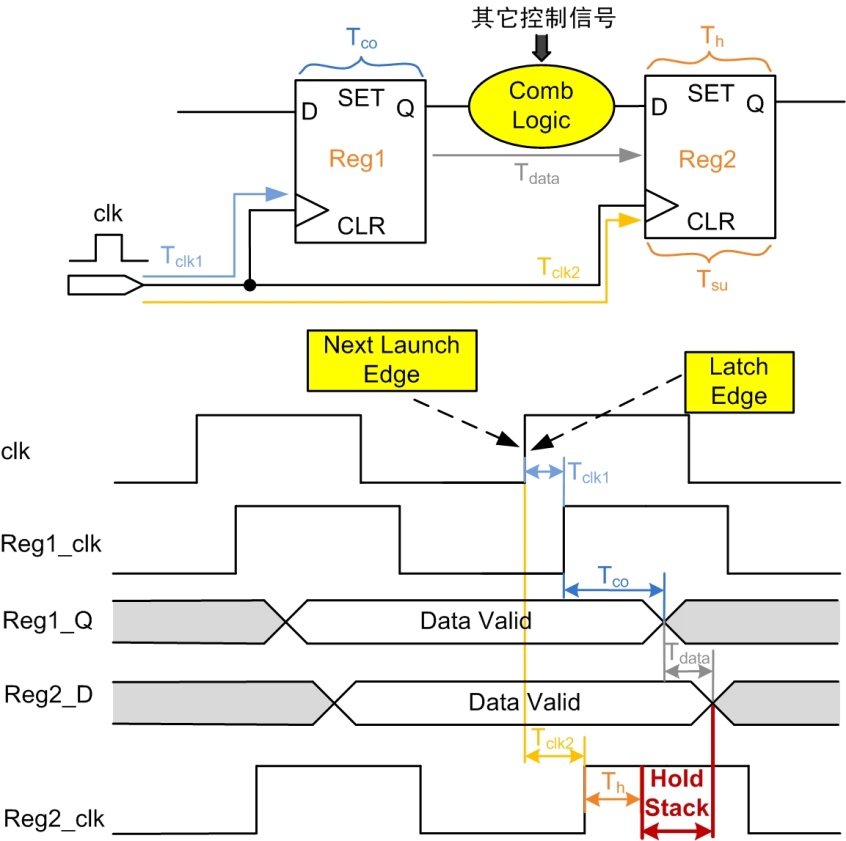

2、保持时间的分析

如图 8所示,保持时间的分析是以第二个launch Edge为基准,在Latch Edge查看结果。保持时间的裕量:

Hold Stack = (Tclk1+Tco+Tdata) – Tclk2 – Th

假设△T = Tclk2-Tclk1,则:

Hold Stack = (Tco+Tdata) – △T – Th

可见△T>0影响保持时间,使保持时间的要求更加苛刻。。因此对于△T尽量避免,采用同步单时钟,并且尽量采用全局的时钟信号,这样△T几乎为0,,△T的影响几乎不存在,可以忽略不计。

如果保持时间的裕量Hold Stack小于0,则不满足保持时间,也就会产生不稳定态,并通过寄存器传输下去。

图 8 保持时间时序分析图

如何利用FPGA进行时序分析设计的更多相关文章

- FPGA Asynchronous FIFO设计思路(2)

FPGA Asynchronous FIFO设计思路(2) 首先讨论格雷码的编码方式: 先看4bit的格雷码,当MSB为0时,正向计数,当MSB为1时,即指针已经走过一遍了,最高位翻转,此时的格雷码是 ...

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- FPGA静态时序分析基础

FPGA静态时序分析基础 基本概念 Skew: 时钟偏移 Skew表示时钟到达不同触发器的延时差别,Tskew = 时钟到达2号触发器的时刻 - 时钟到达1号触发器的时刻. Jitter: 时钟抖动 ...

- 利用FPGA加速实现高性能计算

原文链接 原因:处理器本身无法满足高性能计算(HPC)应用软件的性能需求,导致需求和性能 之间出现了缺口. 最初解决办法:使用协处理器来提升处理器的性能. 协处理器(基于硬件的设计)具有三种能力: 1 ...

- 利用代码生成工具Database2Sharp设计数据编辑界面

在Winform程序开发中,界面部分的开发工作量一般是比较大的,特别是表的字段数据比较多的情况下,数据编辑界面所需要的繁琐设计和后台逻辑处理工作量更是直线上升,而且稍不注意,可能很多处理有重复或者错误 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- FPGA Asynchronous FIFO设计思路

FPGA Asynchronous FIFO设计思路 将一个多位宽,且在不停变化的数据从一个时钟域传递到另一个时钟域是比较困难的. 同步FIFO的指针比较好确定,当FIFO counter达到上限值时 ...

- Xilinx FPGA 的PCIE 设计

写在前面 近两年来和几个单位接触下来,发现PCIe还是一个比较常用的,有些难度的案例,主要是涉及面比较广,需要了解逻辑设计.高速总线.Linux和Windows的驱动设计等相关知识. 这篇文章主要针对 ...

- 利用FPGA实现PCI总线接口及Windows驱动实现

利用FPGA实现PCI总线接口及Windows驱动实现 关于PCI总线协议,资料网上.书本都是.这里我们仅仅对重点对利用FPGA实现PCI总线接口问题进行简单分析.下图是PCI总线接口信号: 配置空间 ...

随机推荐

- MySQL5.7.20 二进制包无ROOT权限下安装, 滴滴云服务器

01, 下载安装包 => https://dev.mysql.com/downloads/mysql/ 02, 上传到linux系统, 笔者这里使用的 滴滴云服务器 安装在 home/dc2- ...

- MySQL(Innodb)索引的原理

引言 回想四年前,我在学习mysql的索引这块的时候,老师在讲索引的时候,是像下面这么说的 索引就像一本书的目录.而当用户通过索引查找数据时,就好比用户通过目录查询某章节的某个知识点.这样就帮助用户有 ...

- Image Base64 Datasnap Image delphi与c#互相兼容识别

delphi用,不能与java.c#互相识别. procedure TServerMethods.UpdateDoc(ItemID : integer; doc : TStream); delphi用 ...

- 5分钟快速打造WebRTC视频聊天<转>

原文地址: 5分钟快速打造WebRTC视频聊天 百度一下WebRTC,我想也是一堆.本以为用这位朋友( 搭建WebRtc环境 )的SkyRTC-demo 就可以一马平川的实现聊天,结果折腾了半天,文本 ...

- BBS-项目流程分析-表的创建

http://www.cnblogs.com/alice-bj/tag/Django%20-%20BBS/ https://www.cnblogs.com/venicid/p/9365019.html ...

- Django--ORM(模型层)-重点

一.ORM简介 MVC或者MVC框架中包括一个重要的部分,就是ORM,它实现了数据模型与数据库的解耦,即数据模型的设计不需要依赖于特定的数据库, 通过简单的配置就可以轻松更换数据库,这极大的减轻了开发 ...

- Python基本数据类型以及字符串

基本数据类型 数字 int ,所有的功能,都放在int里 a1 = 123 a1 = 456 ...

- javascript:图片转base64

第一种: <!DOCTYPE html><html> <head> <meta charset="utf-8"> <meta ...

- 访问Nginx报错

今天新装Nginx,一切妥善后,访问虚拟机服务器的IP,结果发现响应超时 这是因为防火墙的80端口没有打开,在新装的Linux上搭服务器一般会遇到这个问题,重新开放80端口即可解决: (1)firew ...

- 装饰者模式——Head First

一.定义 装饰者模式(Decorator Pattern)动态地将责任附加到对象上.若要扩展功能,装饰者提供了比继承更有弹性的替代方案. 二.类图 三.星巴兹饮料 //Component public ...