低成本FPGA中实现动态相位调整

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自带有DPA电路,但低端的FPGA,如CYCLONE(r)系列中是没有的。下面介绍如何在低端FPGA中实现这个DPA的功能。

实现架构

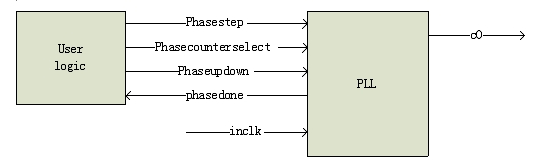

在LVDS输入接收时,时钟和数据的相位可能是不确定的,因此我们需要将时钟的相位作出调整,使得时钟能稳定的采集到输入数据。工作的核心就是用锁相环PLL的相位调整功能,产生若干个时钟的不同相位,看哪些相位能准确的采集到输入数据,然后取窗口中间的一个时钟相位,作为正常工作时的采样时钟。比如通过PLL产生0,45,90,135,……,315度8个相移的时钟,如果0,45,90度相移的时钟能正确采样到输入,那么最后选取中间相位,即45度的时钟作为采样时钟。这样接口上具有最大的时序裕量,从而保证链路的可靠性。下图为这个设计的基本结构,通过PLL调整相位的接口,产生了时钟的不同相位来采集数据,最后选择一个最合适的相位。

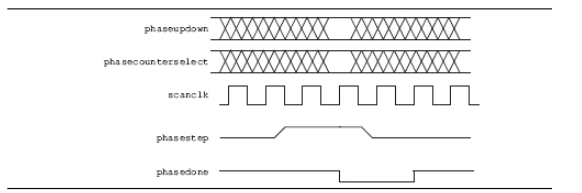

CYCLONE系列的PLL的相位调整接口时序如下图所示:

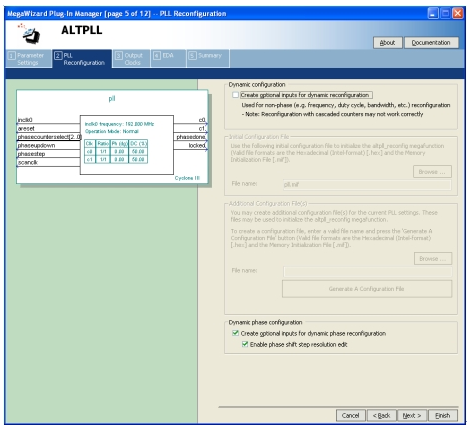

当用户逻辑控制phasestep, phasecounterselect与phaseupdown信号时,PLL的输出时钟C0就改变一次相位。在QII生成PLL时,用户必须选上create optional inputs for dynamic phase reconfigure,否则缺省是不会有这些管脚的,如下图所示。另外必须在output clock tab中写入phase shift step resolution的值,这样才能确定每次相位调整的步长。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

低成本FPGA中实现动态相位调整的更多相关文章

- FPGA中IBERT核的应用(转)

https://wenku.baidu.com/view/50a12d8b9ec3d5bbfd0a74f7.html (必看) 摘要 IBERT即集成式比特误码率测试仪,是Xilinx专门用于具 ...

- FPGA中竞争冒险问题的研究

什么是竞争冒险? 1 引言 现场可编程门阵列(FPGA)在结构上由逻辑功能块排列为阵列,并由可编程的内部连线连接这些功能块,来实现一定的逻辑功能. FPGA可以替代其他PLD或者各种中小规模数 ...

- 理解FPGA中的RAM、ROM和CAM;ROM、RAM、DRAM、SRAM、FLASH

目前大多数FPGA都有内嵌的块RAM(Block RAM),可以将其灵活地配置成单端口RAM(DPRAM,Single Port RAM).双端口RAM(DPRAM,Double Ports RAM) ...

- 巧用FPGA中资源

随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元.DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中.在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利 ...

- 深入理解javascript中的动态集合——NodeList、HTMLCollection和NamedNodeMap

× 目录 [1]NodeList [2]HTMLCollection [3]NamedNodeMap[4]注意事项 前面的话 一说起动态集合,多数人可能都有所了解.但是,如果再深入些,有哪些动态集合, ...

- Quartz 在 Spring 中如何动态配置时间--转

原文地址:http://www.iteye.com/topic/399980 在项目中有一个需求,需要灵活配置调度任务时间,并能自由启动或停止调度. 有关调度的实现我就第一就想到了Quartz这个开源 ...

- ZBrush中的动态网格该怎么进行运用

DynaMesh是ZBrush最新的基础模型创建工具,该命令用于基本模型的起稿到中模的制作.使用DynaMesh完全不启用考虑模型的拓扑,可以从一个图形拉扯出整个模型的分支,本文将以一个实例简单介绍Z ...

- (待续)C#语言中的动态数组(ArrayList)模拟常用页面置换算法(FIFO、LRU、Optimal)

目录 00 简介 01 算法概述 02 公用方法与变量解释 03 先进先出置换算法(FIFO) 04 最近最久未使用(LRU)算法 05 最佳置换算法(OPT) 00 简介 页面置换算法主要是记录内存 ...

- FPGA中的delay与latency

delay和latency都有延迟的意义,在FPGA中二者又有具体的区别. latency出现在时序逻辑电路中,表示数据从输入到输出有效经过的时间,通常以时钟周期为单位. delay出现在组合逻辑电路 ...

随机推荐

- JavaWeb -- Struts 数据传输:OGNL和类型转换

1. 数据传输:OGNL和类型转换 OGNL和struts2 OGNL:Object-Graph Navigation Language. OGNL是集成进struts框架中比较强大的技术有助于数据传 ...

- Gamma函数相关matlab代码

1.Gamma函数: Gamma函数matlab代码: x=:0.5:5syms t y=)*exp(-t),,inf) y=double(y) plot(x,y,) 图像如下: 2.lgΓ(x)函数 ...

- Pandas注意事项&窍门

警告和疑难意味着一个看不见的问题.在使用Pandas过程中,需要特别注意的地方. 与Pandas一起使用If/Truth语句 当尝试将某些东西转换成布尔值时,Pandas遵循了一个错误的惯例. 这种情 ...

- JSON01_资料

1. 资料网址: http://blog.csdn.net/vincent_czz/article/details/7333977 http://blog.csdn.net/huangwuyi/art ...

- MSSQL2005数据库显示单一用户模式,无法进行任何操作

MSSQL2005数据库显示单一用户模式,无法进行任何操作 经查询,使用exec sp_who进行查看链接线程,发现仍然有链接不断进行请求,将链接踢出,然后通过命令修复即可恢复 处理步骤: exec ...

- Apache Tomcat 服务因 0 (0x0) 服务性错误而停止

操作系统:Windows Server 2003 SP2/win7 64JDK 版本为 6.0 update 6 安装在 D:\Java 目录下Tomcat 版本为 6.0.16 安装 D:\Tomc ...

- Django进阶Model篇006 - 多表关联查询

接着前面的例子,举例多表查询实例如下: 1.查询作战的所有完整信息. >>> AuthorDetail.objects.values('sex','email','address', ...

- JavaScript中的两个“0” -0和+0

JavaScript中的两个“0”(翻译) 本文翻译自JavaScript’s two zeros JavaScript has two zeros: −0 and +0. This post e ...

- Microsoft Edge Certified with EBS 12.1 and 12.2

I am very pleased to announce that Microsoft Edge is certified as a new browser for Oracle E-Busines ...

- 【scala】集合框架