Xilinx源语-------FDRE

1、源语---FDRE

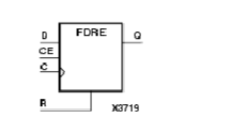

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。在时钟的上升沿数据被加载进入D触发器的输入。

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg1 (

.C (clk), // 同步时钟

.D (data_sync0), //异步数据输入

.Q (data_sync1), //同步数据输出

.CE ('b1), //时钟使能信号

.R ('b0) //复位信号输入,高电平有效

);

由于数据可能与时钟存在着不同步的情况,尤其是在对同步精度要求高的场合,一般还是用多次FDRE源语使得数据、控制信号等同步,例如在一个三态网数据同步模块中使用了四个D触发器进行数据同步:

`timescale 1ps / 1ps (* dont_touch = "yes" *)

module tri_mode_ethernet_mac_0_sync_block #(

parameter INITIALISE = 'b0,

parameter DEPTH =

)

(

input clk, // clock to be sync'ed to

input data_in, // Data to be 'synced'

output data_out // synced data

); // Internal Signals

wire data_sync0;

wire data_sync1;

wire data_sync2;

wire data_sync3;

wire data_sync4; (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg0 (

.C (clk),

.D (data_in),

.Q (data_sync0),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg1 (

.C (clk),

.D (data_sync0),

.Q (data_sync1),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg2 (

.C (clk),

.D (data_sync1),

.Q (data_sync2),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg3 (

.C (clk),

.D (data_sync2),

.Q (data_sync3),

.CE ('b1),

.R ('b0)

); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *)

FDRE #(

.INIT (INITIALISE[])

) data_sync_reg4 (

.C (clk),

.D (data_sync3),

.Q (data_sync4),

.CE ('b1),

.R ('b0)

); assign data_out = data_sync4; endmodule

Xilinx源语-------FDRE的更多相关文章

- 关于各种BUF源语的研究

关于各种BUF源语的研究 资料来源: 单端信号需要用到的BUF 关于这些源语的约束: 增大驱动电流 关于管脚的上拉与下拉约束: ODDR的两种操作模式 关于ODDR输出时钟的应用 为什么ODDR需要这 ...

- FPGA同步复位异步复位

今天看了篇博客, 是拿altera的芯片和软件作例子的,讲同步异步复位的: http://blog.sina.com.cn/s/blog_bff0927b0101aaii.html 还有一个博客, h ...

- Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟篇

xilinx的7系列FPGA根据不同的器件类型,集成了GTP.GTX.GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及最 ...

- 瘋耔java语言笔记

一◐ java概述 1.1 ...

- 多线程的学习与python实现

学习了进程与线程,现对自己的学习进行记录. 目录: 一.进程与线程的概念,以及联系与区别 二.多线程 三.python中多线程的应用 四.python实例 五.参考文献 一.进程与线程的概念.以及联系 ...

- Half Sync And Half Async 半同步半异步模式

如题,这是一个典型的CS结构的模式,至少曾经在CS结构中用过,只是没用好.当年用UDP死活都处理不过来网络命令,用此模式轻松解决. 此模式是典型的三层架构,同步层在一个线程内处理业务逻辑:异步层接受并 ...

- Android系统在超级终端下必会的命令大全(adb shell命令大全)

. 显示系统中全部Android平台: android list targets . 显示系统中全部AVD(模拟器): android list avd . 创建AVD(模拟器): android c ...

- Make和Makefile

无论是在Linux还是在Unix环境中,make都是一个非常重要的编译命令.不管是自己进行项目开发还是安装应用软件,我们都经常要用到make或make install.利用make工具,我们可以将大型 ...

- 初识Attention机制(NLP领域)

Attention 机制. 参考:https://blog.csdn.net/xiewenbo/article/details/79382785 要是关注深度学习在自然语言处理方面的研究进展,我相信你 ...

随机推荐

- 【bzoj4552】【Tjoi2016&Heoi2016】【NOIP2016模拟7.12】排序

题目 在2016年,佳媛姐姐喜欢上了数字序列.因而他经常研究关于序列的一些奇奇怪怪的问题,现在他在研究一个难题,需要你来帮助他.这个难题是这样子的:给出一个1到n的全排列,现在对这个全排列序列进行m次 ...

- 【leetcode】1128. Number of Equivalent Domino Pairs

题目如下: Given a list of dominoes, dominoes[i] = [a, b] is equivalent to dominoes[j] = [c, d] if and on ...

- 错误: 找不到或无法加载主类 org.sang.BlogserverApplication

错误: 找不到或无法加载主类 org.sang.BlogserverApplication

- select下拉框数据回显

前台页面 <select class="select" name="operatorId" id="operatorId" style ...

- Bugku web web基础$_GET

web基础$_GET 打开网站后发现 $what=$_GET['what']; echo $what; if($what=='flag') echo 'flag{****}'; 根据这段话的意思是将w ...

- MSSQL 如何导出db所有用户权限创建语句

use dbgoDECLARE @Database varchar(255),@loginName varchar(255),@roleName varchar(255),@sql nvarchar( ...

- 搜狗词库转txt

#环境需求 Python2 1 #!/bin/python # -*- coding: utf- -*- import struct import sys import binascii import ...

- malloc(50) 内存泄露 内存溢出 memory leak会最终会导致out of memory

https://en.wikipedia.org/wiki/Memory_leak In computer science, a memory leak is a type of resource l ...

- 关于linux中移动目录和到指定目录和移动目录中的数据到指定目录

#这里表示将目录node-v12.13.1-linux-x64移动到/usr/local/中重命名为node,所以node目录可以不存在[root@alone ~]# mv node-v12.13.1 ...

- 浅释Functor、Applicative与Monad

引言 转入Scala一段时间以来,理解Functor.Applicative和Monad等概念,一直是我感到头疼的部分.虽然读过<Functors, Applicatives, And Mona ...