基于FPGA的音频信号的FIR滤波(Matlab+Modelsim验证)

1 设计内容

本设计是基于FPGA的音频信号FIR低通滤波,根据要求,采用Matlab对WAV音频文件进行读取和添加噪声信号、FFT分析、FIR滤波处理,并分析滤波的效果。通过Matlab的分析验证滤波效果后,将叠加噪声信号的音频信号输出到txt文件里。然后使用Matlab语言编写滤波器模块和测试模块,通过Modelsim软件读取txt文件的数据,将数据送入滤波模块,最后将滤波的结果输出到txt文件里,最后用Matlab将处理的结果从txt文件读出、显示、FFT分析用Verilog设计的FIR滤波器的处理效果。

2 设计原理

2.1 语音信号概述

语言是人类创造的,是人类区别于其他地球生命的本质特征之一。人类用语言交流的过程可以看成是一个复杂的通信过程,为了获取便于分析和处理的语音信源,必须将在空气中传播的声波转变为包含语音信息并且记载着声波物理性质的模拟(或数字)电信号,即语音信号,因此语音信号就成为语音的表现形式或载体。

语音学和数字信号处理的交叉结合便形成了语音信号处理。语音信号处理是建立在语音学和数字信号处理基础之上的,对语音信号模型进行分析、存储、传输、识别和合成等方面的一门综合性学科。

本设计中,从WAV音频文件用Matlab读取音频信号进行分析、处理。

2.2 数字滤波器原理

若滤波器的输入、输出都是离散时间信号,那么该滤波器的单位冲激响应h(n)也必然是离散的,这种滤波器称为数字滤波器(DF)。数字滤波器实质上是一种运算过程——用来描述离散系统输入与输出关系的差分方程的计算或卷积计算。数字滤波器的实质是用一有限精度算法实现的离散时间线性时不变系统,以完成对信号进行滤波处理的过程。它是数字信号处理的一个重要分支,具有稳定性好、精度高、灵活性强、体积小、质量轻等诸多优点。

根据单位冲激响应h(n)的时间特性分类

(1) 无限冲激响应(IIR)数字滤波器

(2) 有限冲激响应(FIR)数字滤波器

本设计中选择FIR低通滤波器对音频信号进行滤波处理。

FIR滤波器响应(简称FIR)系统的单位脉冲响应h(n)为有限长序列,系统函数H(z)在有限z平面上不存在极点,其运算结构中不存在反馈支路,即没有环路。如果h(n)的长度为N,则它的系统函数和差分方程一般具有如下形式:

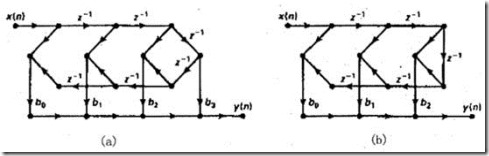

FIR滤波器的结果主要有:直接型、级联型、线性相位型。

设计中采用线性相位型,FIR滤波器最主要的特性就是它可以具备线性相位的特性。所谓线性相位特性,是指滤波器对不同频率的正弦波所产生的相移和正弦波的频率成直线关系。因此,在滤波器通带内的信号通过滤波器后,除了由相移特性的斜率决定的延时外,可以不失真地保留通带内的全部信号。这一点很重要,在很多的应用场合都有所需求。

当系统的单位抽样响应h(n)满足下列对称条件时,即

偶对称条件:h(n)=h(N-1-n)0<n<N-1

奇对称条件:h(n)=-h(N-1-n)0<n<N-1

系统的相頻特性是线性的。其对称中心为(N-1)/2。采用线性相位型可以比直接型少用(N-1)/2个乘法器。下图为N为偶数和奇数的情形,a图为N=7, b图为N=6。

图 1 N为偶数和奇数的FIR滤波器结构

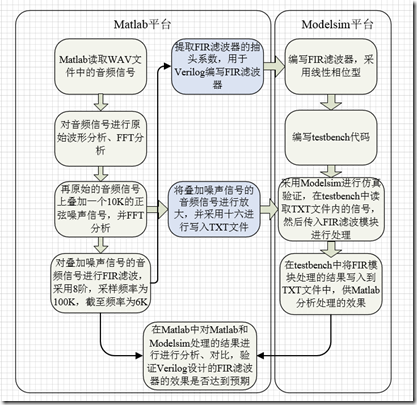

3. 设计思路

本设计主要分为两个部分,一个是Matlab的设计验证和音频信号提取,另一个为Modelsim平台上基于Verilog的FIR滤波器的设计和testbench的编写。

Matlab的设计验证和音频信号提取:在MATLAB中,[y,fs,bits]=wavread('Blip',[N1 N2]);用于读取语音,采样值放在向量y中,fs表示采样频率(Hz),bits表示采样位数。[N1 N2]表示读取的值从N1点到N2点的值。采用此函数对WAV音频信号进行读取,然后对该信号进行FFT分析,再在原始的音频信号上叠加一个6K的正弦波信号,并进行FFT分析。

此过程中需要对叠加了噪声信号的音频信号写入TXT文件作为Modelsim平台的信号源,同时将FIR的抽头参数进行提取,用于Verilog编写FIR滤波器。

在Modelsim平台上,采用Verilog编写线性相位型的FIR滤波器,然后编写testbench代码,testbench的主要功能是提供时钟、复位、信号源,同时将FIR模块的处理结果读出并写入到TXT文件中。

最后将Modelsim处理的结果用Matlab进行分析,并与Matlab处理的结果进行对比。

具体流程如下图:

图 2 本设计的流程

4. 设计过程

4.1 Matlab平台

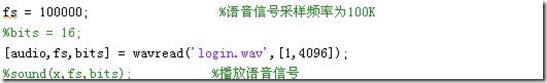

4.1.1 Matlab读取音频文件

在MATLAB中,[y,fs,bits]=wavread('Blip',[N1 N2]);用于读取语音,采样值放在向量y中,fs表示采样频率(Hz),bits表示采样位数。[N1 N2]表示读取的值从N1点到N2点的值。

采样频率为100K,读取点数为4096个信号。

4.1.2 叠加噪声信号

叠加一个频率为6K,点数为4096,幅值为0.003的正弦波,并对叠加前后的信号进行FFT分析。

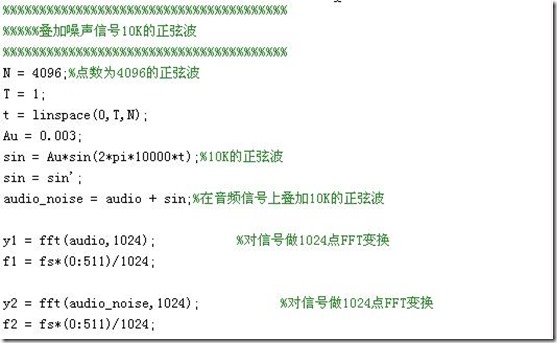

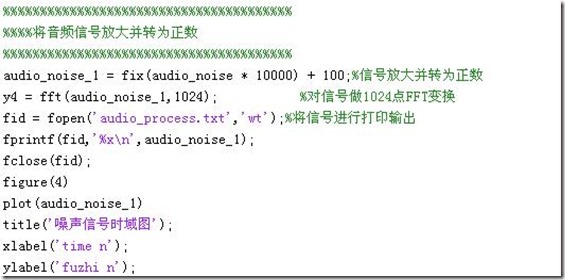

由于读取出来的音频信号幅值很小,由于FPGA处理整数比较方便,所以需要将叠加的噪声的音频信号进行放大,然后将负数转为正整数,最后写入到TXT文件中。

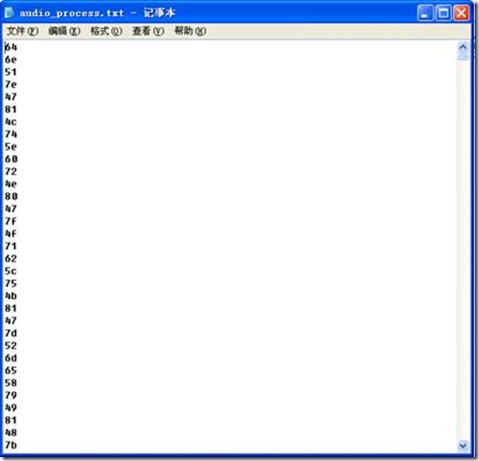

写入的TXT文件如下:

图 3 音频信号的TXT文件

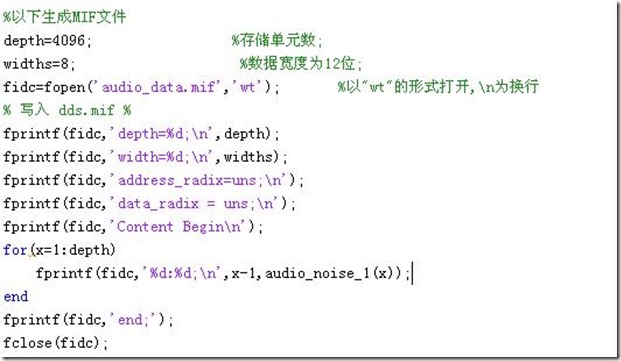

同时,为了将此信号源作为FPGA内部的信号源,还需要将信号数据写入到MIF文件中,然后调用一个ROM模块,存放此数据。在Matlab中将语音信号数据写入MIF文件的代码如下:

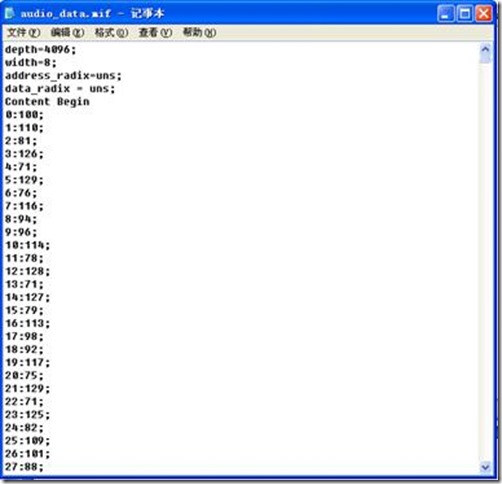

产生的MIF文件数据如下:

图 4 MIF文件

4.1.3 FIR滤波

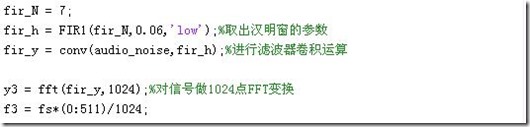

本设计中采用的FIR滤波器为8阶,采样频率为100K,截至频率为6K。

在Matlab中采用fir1函数提取抽头系统,然后将抽头系数和带噪声的音频信号进行卷积,然后对FIR处理的结果进行FFT分析。

提取抽头系数,系数如下:

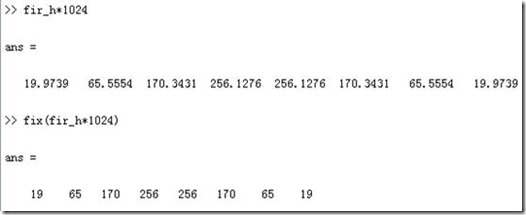

由于提取的系数为浮点数,所以需要对系数进行移位变换,作为整数用于FPGA设计的FIR滤波器中,然后最后再将处理的结果进行反向移位变换,得取正确的结果。

转换后的系数如下:

4.1.4 分析滤波效果

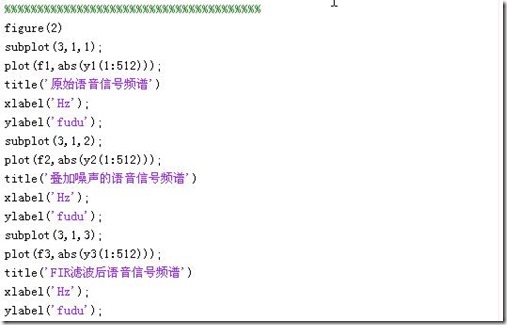

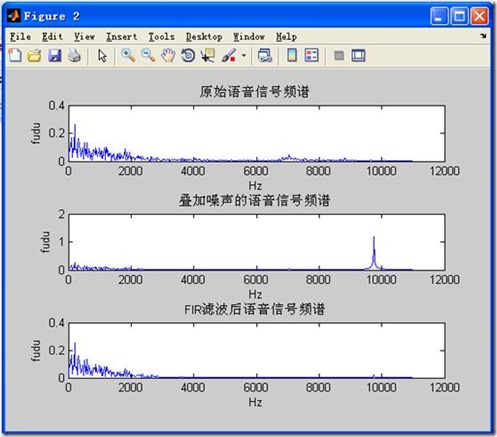

将叠加噪声前后、FIR处理后的信号进行FFT分析,并显示出来进行对比:

4.1

4.2 Modelsim与QuartusII平台

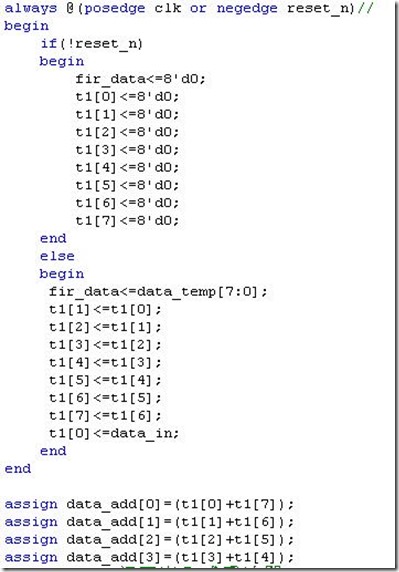

4.2.1 FIR模块的编写

本设计中FIR模块主要分为信号源模块和FIR滤波器模块,信号源模块采用ROM存储带有噪声信号的语音信号,存储的位宽为8bit,深度为4096。由于采用Altera的FPGA中内嵌有一定数量的M4K块,所以可以直接调用这些模块用于存储信号。

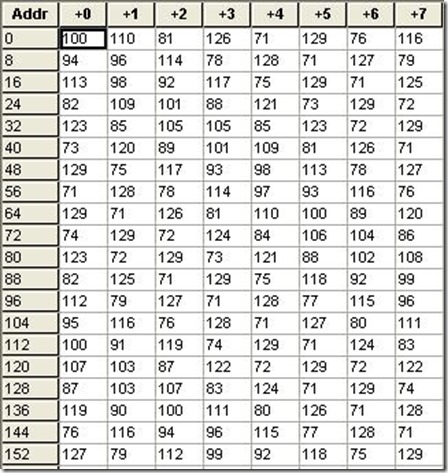

ROM模块中MIF文件存储的信号数据如下:

图 5 ROM模块中的数据

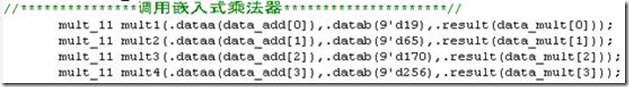

采用线性相位型结构的FIR滤波器进行设计,由此可以将乘法器的个数减少一半,本设计中采用4个乘法器,由于FPGA中内嵌了一定数量的硬件乘法器,由此可以直接调用这些乘法器将抽头参数和信号数据进行乘法运算,以减少逻辑单元的调用和减少一定的延迟。

抽头参数分别为19、65、170、256,是通过将Matlab输出的参数左移10位得到的。

滤波器的结构如下:

由于抽头系数左移了10位,所以在得到最终处理结果后,需要将结果右移10位,如下所示:

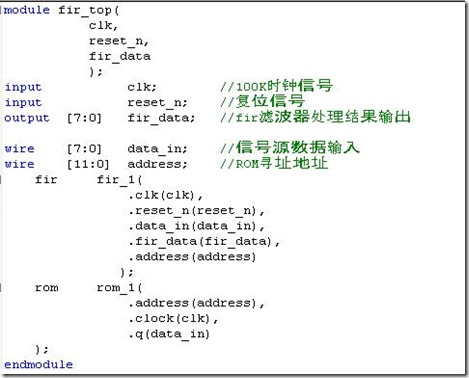

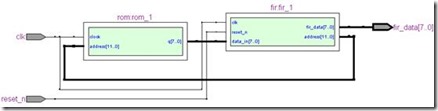

FIR模块顶层设计如下:

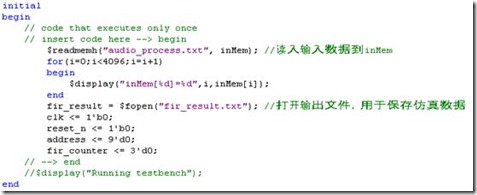

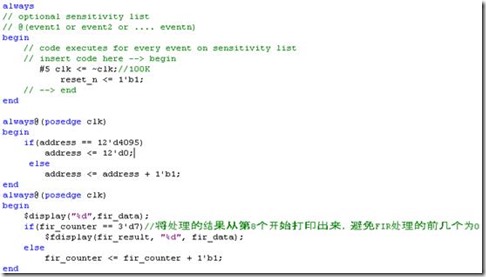

4.2.2 Testbench编写

Testbench的主要的功能是读取TXT文件中的信号数据,作为FIR滤波模块的信号源,同时将为FIR滤波模块提供时钟和复位信号,最后将FIR滤波模块处理后数据写入到TXT文件中。

5 分析验证

5.1 QUARTUS II设计

在设计完成各个模块和顶层封装之后,通过编译综合。

图 6 综合结果

整体设计的RTL视图如下:

图 7 RTL视图

其中,clk信号为100K,同时也是FIR模块的采样信号。

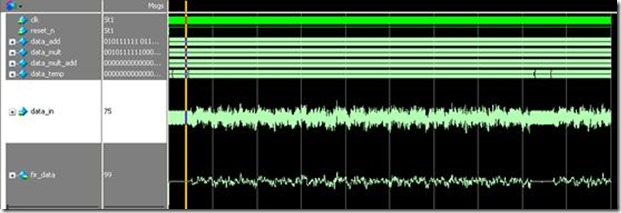

5.2 Modelsim仿真结果分析

Modelsim仿真结果如下,其中data_in为从txt文件读入的叠加了噪声的语音信号,fir_data为经过FIR滤波处理后输出的信号,由于截至频率为6K,从中可以看出,大部分的噪声信号已被滤除,为了更好的分析处理的结果,将FIR处理的结果写入到TXT文件中,然后用Matlab进行FFT分析。

图 8 Modelsim仿真波形

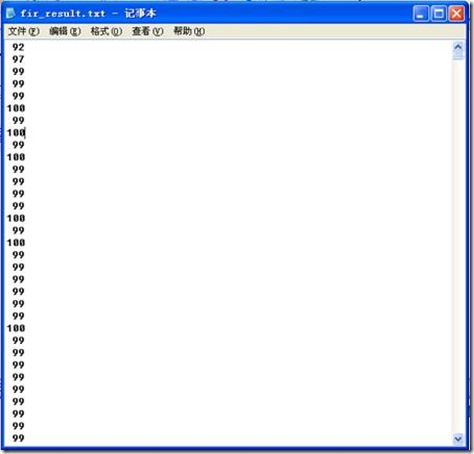

FIR处理输出的结果如下:

图 9 Modelsim仿真结果数据输出

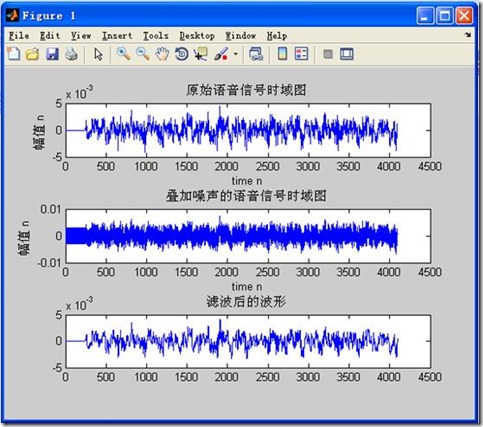

5.3 Matlab设计分析验证

采用Matlab将原始语音信号、叠加噪声的语音信号、FIR滤波后的信号分别显示如下,从下图可以看出,采用8阶的FIR滤波器可以较好的将噪声信号滤除掉。

图 10 时域图对比

为了更好的地分析信号的频谱,原始语音信号、叠加噪声的语音信号、FIR滤波后的信号的頻谱如下,对比可以更加确定地得出,通过FIR滤波,6K以上的信号基本被滤除掉了,由于10K的噪声信号的频率功能相对较大,FIR滤波器的阶数比较少,10K的噪声信号还是未能完全滤除,不过这个可以通过增加阶数将其完全滤除。

图 11 频谱对比

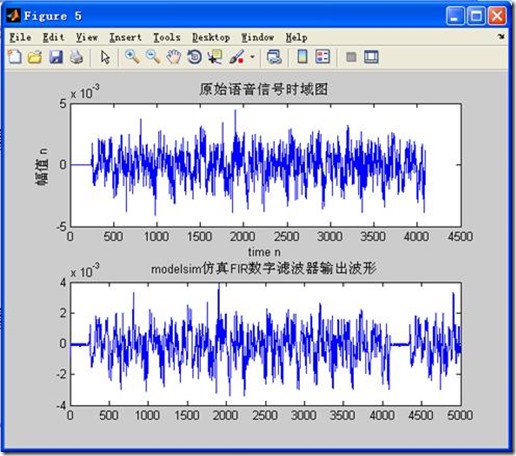

通过Matlab将Modelsim仿真结果的数据读出,并将处理后的语音信号进行显示,并与原始语音信号对比。

图 12 原始语音、Modelsim仿真的语音信号对比

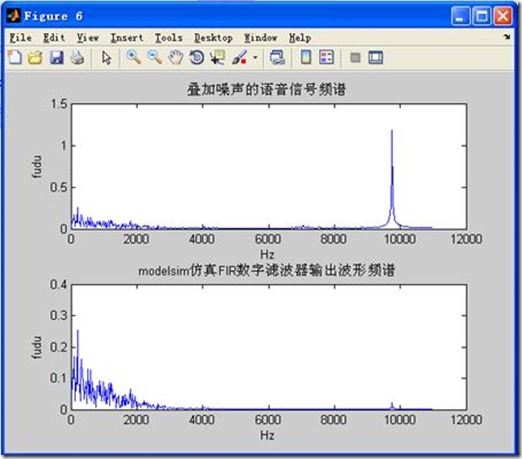

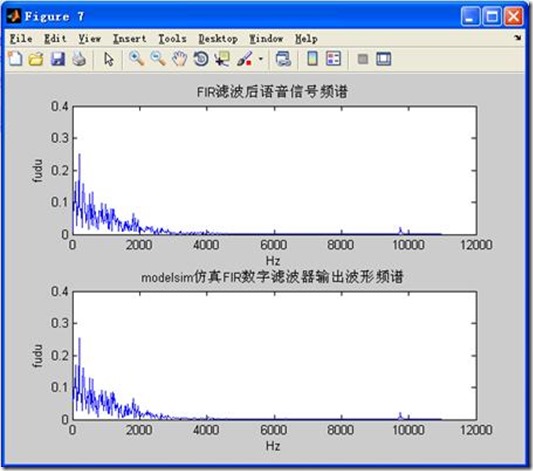

将原始语音信号、采用Matlab进行 FIR滤波后的信号、Modelsim仿真处理后的语音信号进行FFT分析、对比,结果如下:

图 13 叠加噪声的信号与Modelsim仿真后信号频谱对比

图 14 Matlab滤波效果与Modelsim仿真效果对比

通过以上的分析、验证,采用Verilog设计的FIR滤波器能够实现预定的功能,能过将6K以上的噪声信号基本滤除掉,由于10K的噪声信号幅值较大,所以要完全滤波可以通过增加FIR滤波器的阶数。

每日推送不同科技解读,原创深耕解读当下科技,敬请关注“科乎”。

基于FPGA的音频信号的FIR滤波(Matlab+Modelsim验证)的更多相关文章

- 基于FPGA的均值滤波算法的实现

前面实现了基于FPGA的彩色图像转灰度处理,减小了图像的体积,但是其中还是存在许多噪声,会影响图像的边缘检测,所以这一篇就要消除这些噪声,基于灰度图像进行图像的滤波处理,为图像的边缘检测做好夯实基础. ...

- 基于FPGA的均值滤波算法实现

我们为了实现动态图像的滤波算法,用串口发送图像数据到FPGA开发板,经FPGA进行图像处理算法后,动态显示到VGA显示屏上,前面我们把硬件平台已经搭建完成了,后面我们将利用这个硬件基础平台上来实现基于 ...

- 基于FPGA的中值滤波算法实现

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效果图上发现有一些黑白色的斑点,我以为是椒盐噪声,然后在做基于FPGA的中值滤波算法的实验时,我发现黑 ...

- 基于FPGA的IIR滤波器

基于FPGA的IIR滤波器 by方阳 版权声明:本文为博主原创文章,转载请指明转载地址 ...

- 基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- 基于FPGA的腐蚀膨胀算法实现

本篇文章我要写的是基于的腐蚀膨胀算法实现,腐蚀膨胀是形态学图像处理的基础,,腐蚀在二值图像的基础上做"收缩"或"细化"操作,膨胀在二值图像的基础上做" ...

- 基于FPGA dspbuilder的DNLMS滤波器实现

自适应滤波器一直是信号处理领域的研究热点之一,经过多年的发展,已经被广泛应用于数字通信.回声消除.图像处理等领域.自适应滤波算法的研究始于20世纪50年代末,Widrow和Hoff等人最早 ...

- 【转】基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- FPGA经典:Verilog传奇与基于FPGA的数字图像处理原理及应用

一 简述 最近恶补基础知识,借了<<Verilog传奇>>,<基于FPGA的嵌入式图像处理系统设计>和<<基千FPGA的数字图像处理原理及应用>& ...

随机推荐

- SQL Server调优系列进阶篇(查询语句运行几个指标值监测)

前言 上一篇我们分析了查询优化器的工作方式,其中包括:查询优化器的详细运行步骤.筛选条件分析.索引项优化等信息. 本篇我们分析在我们运行的过程中几个关键指标值的检测. 通过这些指标值来分析语句的运行问 ...

- JVM探索之——内存管理(二)

上篇文章我们介绍了JVM所管理的内存结构也就是运行时数据区(Run-Time Data Areas),现在我们将介绍JVM的内存分配与回收静态内存分配与动态内存分配 JVM的内存分配主要分为两种:静态 ...

- Android 横竖屏切换小结

(自己体会:每次横竖屏自动切时都会run Activity的onCreate,即相当后重新进入Activity初始化一样:) 转自:http://www.cnblogs.com/franksunny/ ...

- windows phpstudy 本地添加自定义域名

1.本地配置自定义域名访问 2.打开PHPstudy 域名配置 3.打开host.文件地址 C:\Windows\System32\drivers\etc hosts 192.168.1.101 wi ...

- Brackets(bestcoder)

Brakerts 每次询问一个区间都根据最开始的线段树在询问的区间重建一棵线段树 view code#include <iostream> #include <cstdio> ...

- speex进行音频去噪

应用speex进行音频去噪,speex功能很强大,因为opus的出现,用speex进行编码/解码的人几乎没有了,但是用speex来进行降噪,去除回声,增益还是很多. 这里用speex进行音频去噪,主要 ...

- BeJavaGod - 如何正确使用数据字典进行分类统一操作(一)

先说说什么是数据字典,这个玩意一般不太会解释,举个栗子吧~ 每个系统都会有用户表,性别:男(1)女(0) 另外我们做物流的会涉及到车型:卡车(1),轿车(2),挂车(3) 货物类型:危险品(1),普通 ...

- java 访问sql server数据库

控制面板--管理工具—ODBC数据源(64位)--系统DNS—添加(名称为“test”,服务器填“.”描述随意) 这里访问的数据库为AdventuerWorks 数据源配置好后可以测试一下,下面是ja ...

- 第18章 图元文件_18.2 增强型图元文件(emf)(2)

18.2.7 增强型图元文件的查看和打印程序 (1)传递EMF到剪贴板,剪贴板类型应为:CF_ENHMETAFILE (2)CopyEnhMetaFile用于复制图元文件 (3)剪贴板中的图元文件会自 ...

- Google Guava官方教程(中文版)

Google Guava官方教程(中文版) 原文链接 译文链接 译者: 沈义扬,罗立树,何一昕,武祖 校对:方腾飞 引言 Guava工程包含了若干被Google的 Java项目广泛依赖 的核心库, ...