FPGA奇数分频

在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2、4、8、16、32、64等这些以2的整数倍的。

这里说的是奇数倍分频,如时钟是100MHz,需要一个20MHz的输出频率,那么就需要5次分频,那么问题来了,安装2分频的方法:100/2=50,50/2=25,只能等到一个25MHz的频率,显然这种方法是不可行的,那么就需要奇数分频了。

1、做个模为5的计数器,

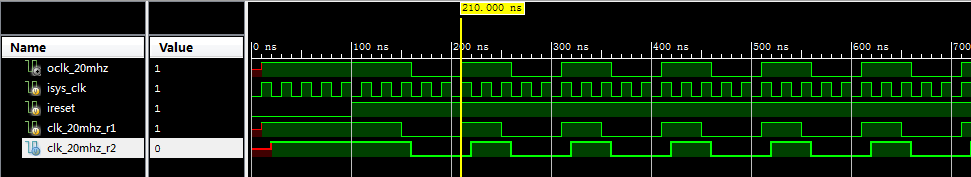

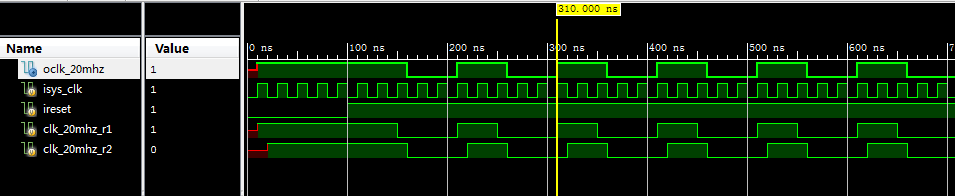

2、做两个个信号a,b。在模1的计数下,前2个周期信号a为高电平,后3个周期信号a为低电平。

3、用时钟的下降沿将信号a延时一个节拍,得到信号b。

4、信号a或b运算输出时钟,即得到占空比为1:1的5分频20MHz时钟频率。

程序中a为clk_20mhz_r1,b为clk_20mhz_r2。

module system_clk

(

input isys_clk,

input ireset,

output oclk_20mhz

);

reg [2:0] cnt_20mhz;

reg clk_20mhz_r1;

reg clk_20mhz_r2;

always @(posedge isys_clk or negedge ireset)

begin

if(!ireset)

cnt_20mhz <= 3'd0;

else if( cnt_20mhz >= 3'd4)

cnt_20mhz <= 3'd0;

else

cnt_20mhz <= cnt_20mhz + 1'b1;

end

always @(posedge isys_clk )

begin

if( cnt_20mhz < 3'd2)

clk_20mhz_r1 <= 1'b1;

else

clk_20mhz_r1 <= 1'b0;

end

always @(negedge isys_clk)

begin

clk_20mhz_r2 <= clk_20mhz_r1;

end

assign oclk_20mhz = clk_20mhz_r1 | clk_20mhz_r2;

endmodule

FPGA奇数分频的更多相关文章

- FPGA三分频,五分频,奇数分频

我们在做FPGA设计时,有时会用到时钟频率奇数分频的频率,例如笔者FPGA的晶振为50M,当我们需要10M的时钟时,一种方式可以使用DCM或PLL获取,系统会内部分频到10M,但其实VERILOG内部 ...

- FPGA时钟分频(转)

http://www.cnblogs.com/fpga/archive/2009/10/24/1589318.html 占空比为50%的分频 偶数分频比较简单 比如N分频,那么计数到N/2-1,然后时 ...

- verilog 奇数分频设计

module tw(clk,k_or,k1,k2); input clk; output k_or,k1,k2; reg [2:0] c1,c2; reg m1,m2; initial begin c ...

- Verilog 奇数分频

代码: module odd_div( ); ; //分频系数,3即3分频 ; reg clk, rstn, clk_div_pos, clk_div_neg; wire clk_div_out; : ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- verilog实现奇数倍分频

在学习FPGA的过程中,最简单最基本的实验应该就是分频器了, 同时分频器也是FPGA设计中使用频率非常高的基本设计之一, 尽管在芯片厂家提供的IDE中集成了锁相环IP, 如altera 的PLL,Xi ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

- 【Verilog】verilog实现奇数次分频

实现占空比为50%的N倍奇数分频:首先进行上升沿触发进行模N计数,计数到某一个值时进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%的奇数n分频时钟.再者 同时进行下降沿触发的 ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

随机推荐

- c#读取文本文档实践4-读入到list泛型集合计算后写入新文档

商品 数量 单价英语 66 100语文 66 80数学 66 100化学 66 40物理 66 60 上面截图是要处理的文本文档内容,目的是计算出总价并加在最后一列. 这一篇与上一篇比较类似,目的相同 ...

- SQL 解决in的参数烦恼(经典,简洁,高效)

原SQL是不能执行的:select * from 表A where 字段A in (select 逗号分隔的字段B from 表B where 条件) 解决方案:select b.* from (se ...

- Android Studio的一些快捷键

以下这些也是百度的其他人整理的.后面有新的会加进来. AS的快捷键容易和QQ,微信等冲突,可以手动关掉或者修改其他软件的热键 Ctrl+G / Ctrl+Alt+Shift+G:查询变量或者函数或者类 ...

- C++异常处理的问题

一般在C语言中,是通过返回值或者设置errno的方式来标识错误的 但在C++里面,构造函数是没有返回值的,于是发明了异常的方式:为了正确的向使用者表明 异常抛出的原因,你必须弄清楚异常抛出的原因(比如 ...

- Runloop之个人理解

Runloop之个人理解更像是一种线程等待机制,传统线程的消息传入机制,线程收到什么样的消息,就执行什么样的动作,如果是信号量队列型的,其实就基本实现了线程在无消息时挂住休眠;而不是在每隔一段时间就要 ...

- JQUERY操作css与css()方法、获取设置尺寸;

一.jQuery addClass() 方法 向不同的元素添加 class 属性.在添加类时,您也可以选取多个元素 <style> .aa { color:red; }; </sty ...

- JavaScript中的document.cookie的使用

转:http://blog.csdn.net/liuyong0818/article/details/4807473 我们已经知道,在 document 对象中有一个 cookie 属性.但是 Coo ...

- Mvc4系列文章

http://www.cnblogs.com/duanshuiliu/tag/MVC/

- javascript_获取浏览器属性

navigator.appName:浏览器名称: navigator.appVersion:浏览器版本: navigator.language:浏览器设置的语言: navigator.platform ...

- 第一节:简单的请求(Requests)和响应(Responses)

目录 创建项目 开发服务器 创建名称为Polls的应用 编写你的第一个视图 创建项目 在命令行中,使用cd命令进入到你想要存储你的项目的目录,然后运行下面的命令: $ django-admin sta ...