ISE联合modelsim功能仿真和综合后仿真1

本文出自 “李海川” 博客,请务必保留此出处http://lihaichuan.blog.51cto.com/498079/984870

补充:http://wenku.baidu.com/link?url=idbSvNzz2fLSl1WXiEmtIL1amhQTHmtqqQ6g1cp-oU1X3W4wF2Wdu5LSe745rwjCrM-btR44-we9zLCyMf2ofjjAt2d8wcBT7LFyIHF8Tym

ISE联合modelsim功能仿真和综合后仿真1的更多相关文章

- ISE联合modelsim功能仿真和综合后仿真

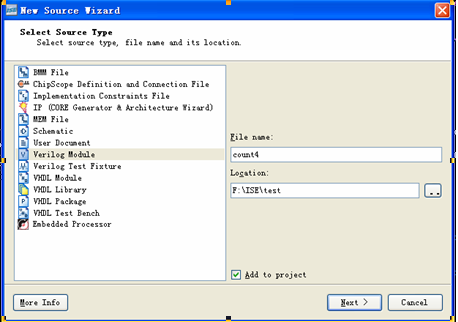

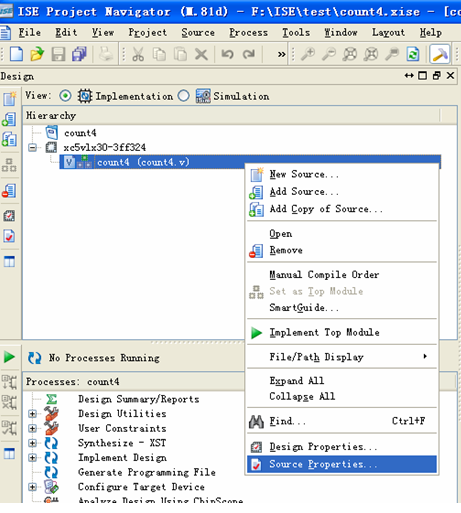

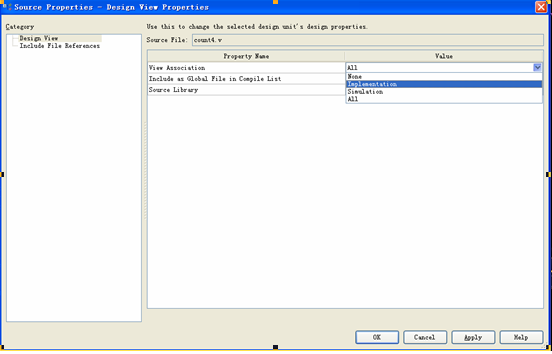

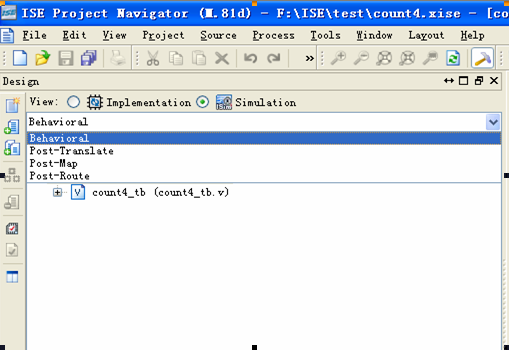

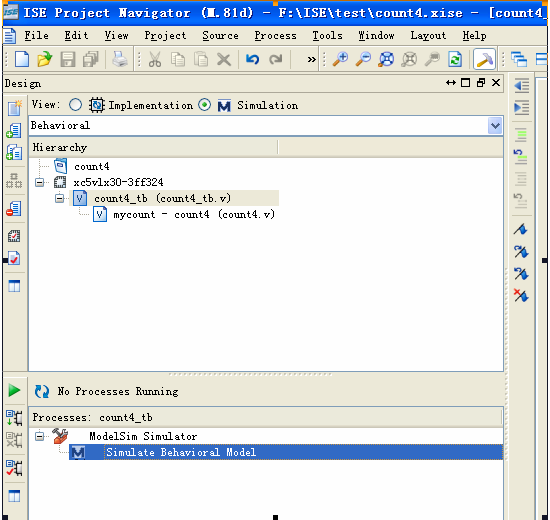

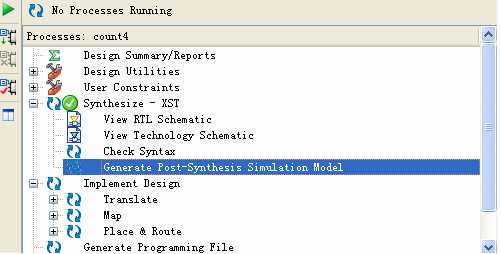

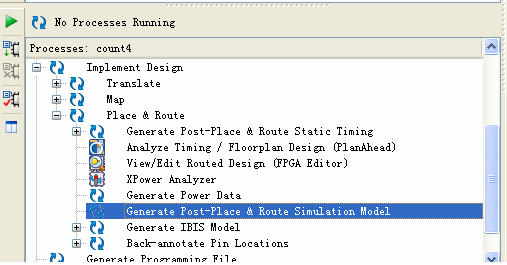

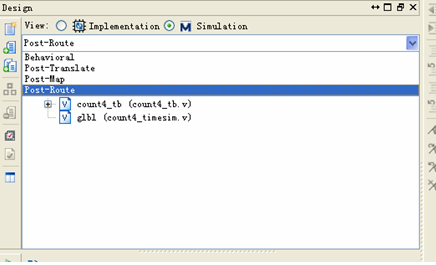

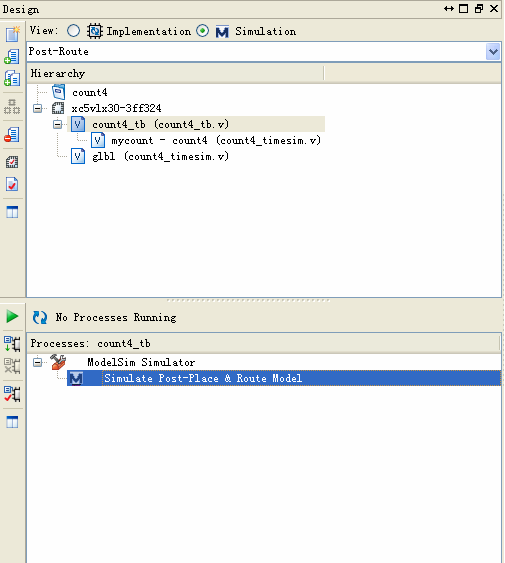

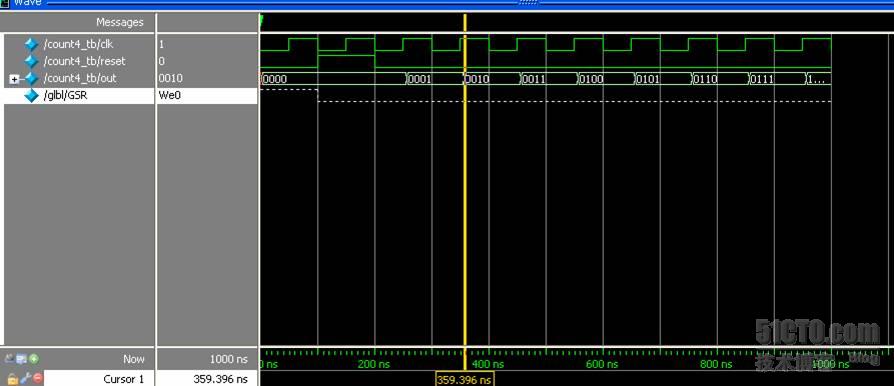

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- 用Modelsim仿真QuartusII综合后网表时库的添加方法(转)

这两天做综合后仿真,发现FPGA器件库又不会加了,无奈上网找方法.说起来不好意思,很早就接触Modelsim这个仿真软件了,可是没有好好琢磨.把这两天找的方法贴出来,再加上自己的理解,以后忘了可以上博 ...

- FPGA功能仿真,门级仿真,后仿真的区别

前言 分清楚各种仿真间的关系,工具采用quartus prime16.0,仿真工具采用modelsim10 ae版:项目:led_display; 流程 1.RTL行为级仿真:也叫功能仿真,这个阶段的 ...

- ISE和Modelsim联合仿真(详细步骤讲解)

ISE和Modelsim联合仿真(转) 地址:http://www.cnblogs.com/feitian629/archive/2013/07/13/3188192.html 相信很多人会遇到过这个 ...

- ISE和Modelsim联合仿真(转)

相信很多人会遇到过这个问题,不知如何让ISE调用Modelsim进行仿真.我也迷糊了不少时间,查查找找,终于弄明白了,所以有了本文,和大家分享一下.我尽量讲得详细点儿,多多上图. 我的环境:Windo ...

- ISE综合后得到的RTL图如何与硬件对应起来,怎么知道每个element的功能

2013-06-23 21:34:03 要知道“我写的这段代码会综合成什么样的电路呢”,就要搞清楚RTL图中每个模块的功能,从而将代码与硬件对应,判断综合后的电路是否与预期的一致.如何做到? 之前查了 ...

- ise和modelsim联合仿真的一些准备

首先要在modelsim中编译xilinx的三个库,分别是unisims库,simprims库,和corelib库,其中unisims库全称为(library of united component ...

- 怎样用modelsim做后仿真

摘要: 怎样用modelsim做后仿(编译工具采用quatus) step1:在qurtus改变编译选项: assignments->EDA tool setting:选择verilog ...

- [原创]Modelsim后仿真

因调试需要,进行后仿真,ISE生成的sim文件和sdf文件 `timescale ns/ ps module lut_dly ( clkout, fpga_clk, config_in ); outp ...

随机推荐

- 如何使用屏幕取色工具ColorPixl

ColorPix可以屏幕取色,假如现在想要取色桌面徽标键的颜色,按任意键可以锁定这个区域(press any key to lock)这样我们就可以在放大的区域更清楚的取色,加号按钮可以设置该软件是否 ...

- 简单概率dp-hdu-4487-Maximum Random Walk

题目链接: http://acm.hdu.edu.cn/showproblem.php?pid=4487 题目大意: 开始位置在0,每一步可以向右向左或者不动,问走了n步后,路径中能到达最右的期望. ...

- iOS判断日期A是否在日期B到日期C之间

方法一: 可以用nsdate 的 timeIntervalSince1970 方法把时间转换成时间戳进行比较,这里timeIntervalSince1970返回的是NSTimeInterval(dou ...

- PHP高级教程-JSON

PHP JSON 本章节我们将为大家介绍如何使用 PHP 语言来编码和解码 JSON 对象. 环境配置 在 php5.2.0 及以上版本已经内置 JSON 扩展. JSON 函数 函数 描述 json ...

- 【IPC进程间通讯之二】管道Pipe

IPC进程间通信+管道Pipe IPC(Inter-Process Communication.进程间通信). 管道用于进程间共享数据,事实上质是共享内存 ...

- JAVA 爬虫Gecco

主要代码: Gecco(matchUrl="https://github.com/{user}/{project}", pipelines="consolePipelin ...

- Java基础2-容器篇

java基础2-容器篇 1.页首请关注 思维导航大纲 1.常用容器的类型层次结构 2.理解容器的常用思维大纲 a.空间 时间 concurrentModifyException 加载因子 3.常用类源 ...

- 使用quartz进行容器启动时登陆接口服务器和接口服务器进行心跳连接

1.下载quartz的相应jar包 2.增加spring配置文件(applicationContext-quartz.xml) 内容如下: <?xml version="1.0&quo ...

- java打包成window service服务[转]

1 解释 java project 我说的是main方法作为程序入口的java工程,有别于 web project. 这样的工程 一般都是web project的附属扫描程序或一些独立的执行程序,如 ...

- C# 采用钩子捕获键盘和鼠标事件-验证是否处于无人操作状态

原文地址:https://www.cnblogs.com/gc2013/p/4036414.html 全局抽象类定义 using System; using System.Collections.Ge ...