基于FPGA的SATA3.0主机控制器IP

SATA3.0 Host Controller IP

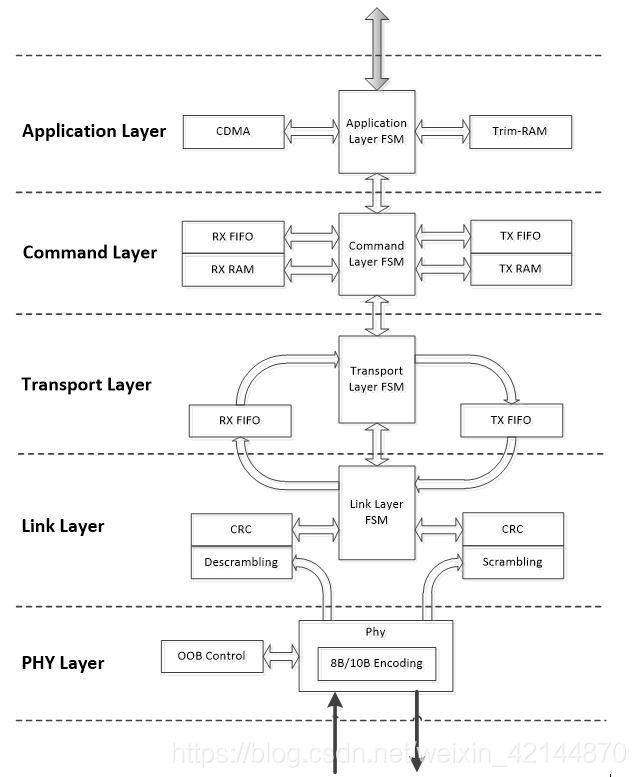

SATA3.0 Host IP不仅实现了SATA协议的PHY(物理层)、Link(链路层)和TRN(传输层),并且实现了CMD(命令层)和APP(应用层),支持1.5、3和6Gbps传输速率,和SATA规范完全兼容。

SATA3.0 Host IP给用户使用SATA存储设备提供一种高效且易于使用的接口。无需用户干预,SATA3.0 Host IP自动完成连接、诊断、识别以及初始化SATA存储设备,输出SATA设备的Identify Data Structure。SATA3.0 Host IP内置DMA控制器,用户不但可以通过IO接口访问SATA存储设备,还可以使用DMA接口高效读写SATA存储设备。

SATA3.0 Host IP不局限连接SATA存储设备的个数,即连接SATA存储设备的数量是可编程的。

内核特性:

- 与SATA 1.5Gbps、3.0Gbps以及6.0Gbps业界规范完全兼容

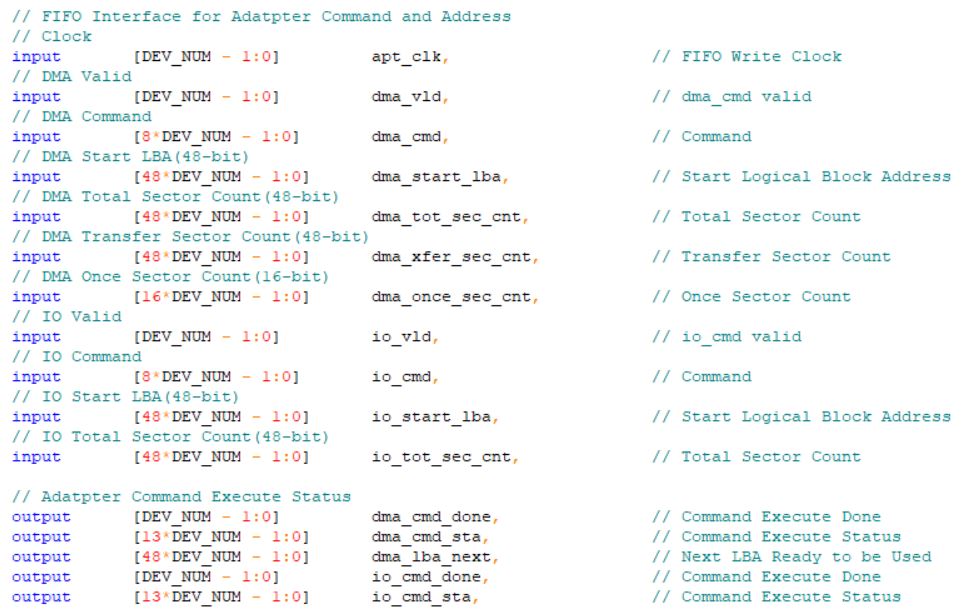

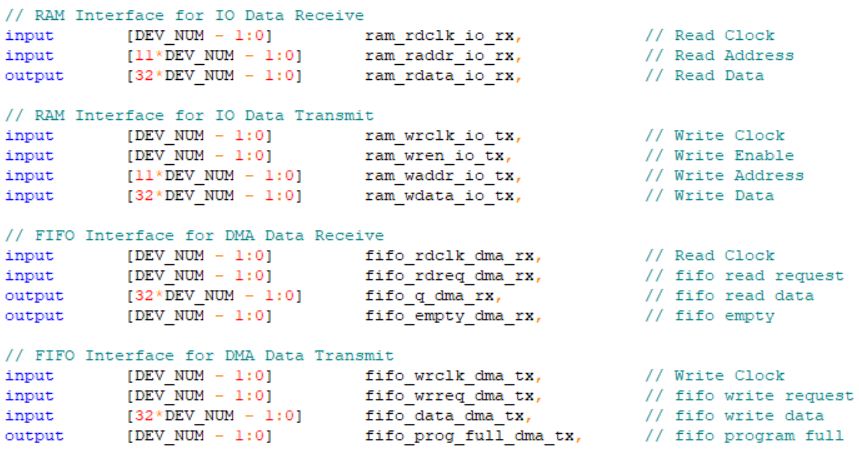

- AXI-Lite或应用寄存器(ARI)接口,同时支持IO(包括PIO和Trim)和DMA操作

- IO数据接口采用RAM设计,DMA数据接口采用AXI-Stream或FIFO设计

- 支持SerDes接口,并且SerDes接口个数可编程(即可连接的SATA存储设备的数量是可编程的,数量取决于FPGA的GT个数)

- 支持SATA存储设备带电热插拔

- 支持Xilinx器件:Spartan-6,Virtex-5,Virtex-6,Artix-7,Kintex-7,Virtex-7,Kintex Ultrascale,Kintex Ultrascale+,Virtex Ultrascale,Virtex Ultrascale+

- 易于集成的同步、可综合Verilog设计

- 通过完全验证的SATA3.0 IP

对外接口:

- AXI-Lite或应用寄存器(ARI)接口

- AXI-Stream或FIFO流式数据总线

- RAM块式数据总线

性能指标:

- SATA 3.0 Core:连续写入速度大于530MB/s,连续读取速度大于550MB/s

- SATA 2.0 Core:连续写入速度大于240MB/s,连续读取速度大于250MB/s s

1通道(连接1个SATA存储设备)SATA3.0 IP资源使用(XC7K325为例):

- LUTs:3850,FFs:4630,BRAM:16,GT:1

4通道(连接4个SATA存储设备)SATA3.0 IP资源使用(XC7K325为例):

- LUTs:15363,FFs:18468,BRAM:64,GT:4

8通道(连接8个SATA存储设备)SATA3.0 IP资源使用(XC7K325为例):

- LUTs:30763,FFs:37011,BRAM:128,GT:8

可交付资料:

- 详细的用户手册

- Design File:Post-synthesis EDIF netlist or RTL Source

- Timing and layout constraints,Test or Design Example Project

- 技术支持:邮件,电话,现场,培训服务

联系方式:

Email:neteasy163z@163.com

SATA3.0 Host IP Block Diagram

基于FPGA的SATA3.0主机控制器IP的更多相关文章

- 基于FPGA的AES加解密IP

Programmable AES Encryption/ Decryption IP 可编程AES加解密IP 可编程AES加解密IP提供了加解密算法功能,兼容美国国家标准与技术研究院(NIST)发布的 ...

- 基于FPGA+USB2.0的图像采集系统测试小结-mt9m001

基于FPGA+USB2.0的图像采集系统测试小结-mt9m001 该系统采用层层惊涛出品的FPGA_VIP_USB_V102板卡测试 板卡分为:核心板.底板.摄像头板 核心板采用:ep4ce10e22 ...

- 基于FPGA的红外遥控解码与PC串口通信

基于FPGA的红外遥控解码与PC串口通信 zouxy09@qq.com http://blog.csdn.net/zouxy09 这是我的<电子设计EDA>的课程设计作业(呵呵,这个月都拿 ...

- 基于FPGA的均值滤波算法的实现

前面实现了基于FPGA的彩色图像转灰度处理,减小了图像的体积,但是其中还是存在许多噪声,会影响图像的边缘检测,所以这一篇就要消除这些噪声,基于灰度图像进行图像的滤波处理,为图像的边缘检测做好夯实基础. ...

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- 基于FPGA的腐蚀膨胀算法实现

本篇文章我要写的是基于的腐蚀膨胀算法实现,腐蚀膨胀是形态学图像处理的基础,,腐蚀在二值图像的基础上做"收缩"或"细化"操作,膨胀在二值图像的基础上做" ...

- 基于FPGA dspbuilder的DNLMS滤波器实现

自适应滤波器一直是信号处理领域的研究热点之一,经过多年的发展,已经被广泛应用于数字通信.回声消除.图像处理等领域.自适应滤波算法的研究始于20世纪50年代末,Widrow和Hoff等人最早 ...

- 优化基于FPGA的深度卷积神经网络的加速器设计

英文论文链接:http://cadlab.cs.ucla.edu/~cong/slides/fpga2015_chen.pdf 翻译:卜居 转载请注明出处:http://blog.csdn.net/k ...

随机推荐

- Chapter 09 - NSUndoManager (C#实现 + 全网原创)

此例子针对NSDocument实现了tableview 每一行添加/删除的undo/redo,以及每一个单元格内容编辑的undo/redo.基于NSDocument类的实现.PersonModel + ...

- 【java】学习路径29-异常捕捉实例

import java.util.ArrayList;public class ExceptionCatchDemo { public static void main(String[] args) ...

- 前端利器躬行记(8)——VSCode插件研发

VSCode提供了丰富的 API,可以借助编辑器扩展许多定制功能. 本次研发了一款名为 Search Method 的插件,在此记录整个研发过程. 一.准备工作 1)安装环境 首先是全局安装 yo 和 ...

- Dynamic CRM插件中记录日志-Nlog记录到文本

Dynamic CRM插件中记录日志的方式有多种 通常情况下分为ITracingService记录.单独日志表插入记录.文本记录三种. 之前整理过ITracingService记录的方式,但这种记录有 ...

- 使用VS Code 搭建 platformio 平台

一.需要的资源网站 arduino GitHub:https://github.com/arduino espressif GitHub:https://github.com/espressif pl ...

- SpringMvc(一)-初识

1.环境搭建 1.1 jar包 <spring.version>4.3.18.RELEASE</spring.version> <!-- spring-mvc begin ...

- 如何写成高性能的代码(一):巧用Canvas绘制电子表格

一.什么是Canvas Canvas是HTML5的标签,是HTML5的一种新特性,又称画板.顾名思义,我们可以将其理解为一块画布,支持在上面绘制矩形.圆形等图形或logo等. 需要注意的是,与其他标签 ...

- kindeditor获取html内容之终极大法

请允许我哔哔两句,真是难受啊,有问题去百度,结果百了一堆乱七八糟的内容,有头没尾,有尾没头的,搞得我晕头转向,现在把kindeditor获取HTML的终极打法无偿分享出来,这可是我配置查找了一下午的成 ...

- Django 测试脚本

一.测试脚本 Django 在创建项目时自动在应用下创建了tests.py,这个py文件可以作为测试文件:也可以在应用下手动创建一个py测试文件. 无论哪种方式,都需要提前书写以下代码. from d ...

- kibana访问多个 Elasticsearch 节点间的负载均衡

如果 Elasticsearch 集群有多个节点,分发 Kibana 节点之间请求的最简单的方法就是在 Kibana 机器上运行一个 Elasticsearch 协调(Coordinating onl ...