AD_TLC549采集模拟信号

AD_TLC549采集模拟信号

实验原理

芯片介绍

TLC549是 TI公司生产的一种低价位、高性能的8位A/D转换器,它以8位开关电容逐次逼近的方法实现 A/D转换,其转换速度小于 17us,最大转换速率为 40000HZ,4MHZ典型内部系统时钟,电源为 3V至 6V。它能方便地采用三线串行接口方式与各种微处理器连接,构成各种廉价的测控应用系统。

TLC549 引脚图及各引脚功能

TLC549引脚图

REF+:正基准电压输入 2.5V≤REF+≤Vcc+0.1。

REF-:负基准电压输入端,-0.1V≤REF-≤2.5V。且要求:(REF+)-(REF-)≥1V。

VCC:系统电源3V≤Vcc≤6V。

GND:接地端。

/CS:芯片选择输入端,要求输入高电平 VIN≥2V,输入低电平 VIN≤0.8V。

DATA OUT:转换结果数据串行输出端,与 TTL 电平兼容,输出时高位在前,低位在后。

ANALOGIN:模拟信号输入端,0≤ANALOGIN≤Vcc,当 ANALOGIN≥REF+电压时,转换结果为全"1"(0FFH),ANALOGIN≤REF-电压时,转换结果为全"0"(00H)。

I/O CLOCK:外接输入/输出时钟输入端,同于同步芯片的输入输出操作,无需与芯片内部系统时钟同步。

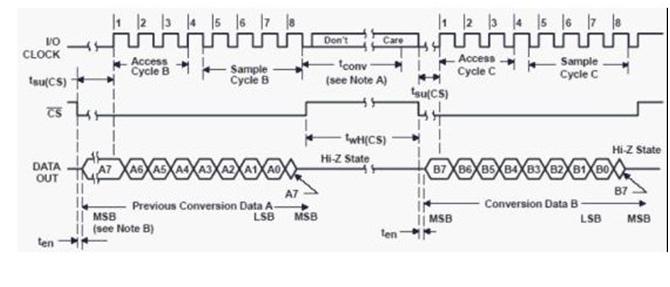

TLC549工作时序

当/CS变为低电平后, TLC549芯片被选中,同时前次转换结果的最高有效位MSB (A7)自 DATA OUT 端输出,接着要求自 I/O CLOCK端输入8个外部时钟信号,前7个 I/O CLOCK信号的作用,是配合 TLC549 输出前次转换结果的 A6-A0 位,并为本次转换做准备:在第4个 I/O CLOCK 信号由高至低的跳变之后,片内采样/保持电路对输入模拟量采样开始,第8个 I/O CLOCK 信号的下降沿使片内采样/保持电路进入保持状态并启动 A/D开始转换。转换时间为 36 个系统时钟周期,最大为 17us。直到 A/D转换完成前的这段时间内,TLC549 的控制逻辑要求:或者/CS保持高电平,或者 I/O CLOCK 时钟端保持36个系统时钟周期的低电平。由此可见,在自 TLC549的 I/O CLOCK 端输入8个外部时钟信号期间需要完成以下工作:读入前次A/D转换结果;对本次转换的输入模拟信号采样并保持;启动本次 A/D转换开始。

TLC549工作时序

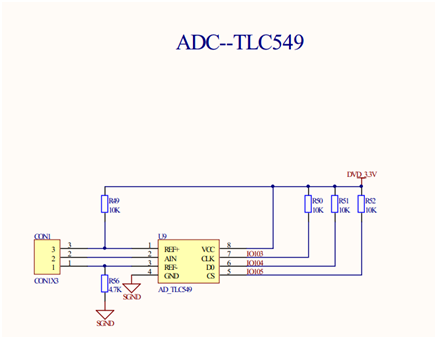

本实验中,我们使用TLC549芯片检测模拟电压,为方便检测,我们在实验中,使用了数码管作为我们的显示模块,将检测到的电压显示到数码管上,与实际的电压进行比较。开发板上,芯片VCC=3.3V,VREF+=3.3V,VREF-=0。

硬件原理图

实验代码

|

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: ADC_TLC549.v ** 创建日期: ** 功能描述:使用AD芯片TLC549采集模拟信号,经过模数转换并显示在数码管上 ** 操作过程:将模拟信号接到TLC549的数据管脚上,观察数码管变化 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module ADC_TLC549 ( clk,//系统50MHZ时钟 adc_sclk,//AD TLC549的时钟 data,//AD TLC549的数据口 cs,//AD TLC549的片选择 wei,//数码管的为选择 段码 ); input clk; input data; output cs; output adc_sclk; ] duan; ] wei; reg cs,adc_sclk,clk1k,clk1ms; ] count; ] count1ms; ] cnt; ] number; ] state; ] wei; reg ledcs; ] duan; ] dataout; ] tenvalue; parameter sample=2'b00, display=2'b01; /**********产生100k的采集时钟信号*********/ always@(posedge clk) begin ) count<=count+1'b1; else begin ; adc_sclk<=~adc_sclk; end end /*******产生周期为1ms即1kHz的信号*********/ always@(posedge clk) begin if(count1ms>25'd25000) begin clk1ms<=~clk1ms; ; end else ; end /*********AD采样程序**************/ always@(negedge adc_sclk) begin case(state) sample: begin ; ],data}; if(cnt>4'd7) begin ; state<=display; end else begin ; state<=sample; end end display: begin ;//关AD片选 ;// //得到采集的数据 state<=sample; end default: state<=display; endcase end /***********2进制转十进制函数*************/ 位的数字 ] datain; begin case(datain) 4'b00000000: tendata=4'd0;//0 4'b00000001: tendata=4'd1;//1 4'b00000010: tendata=4'd2;//2 4'b00000011: tendata=4'd3;//3 4'b00000100: tendata=4'd4;//4 4'b00000101: tendata=4'd5;//5 4'b00000110: tendata=4'd6;//6 4'b00000111: tendata=4'd7;//7 4'b00001000: tendata=4'd8;//8 4'b00001001: tendata=4'd9;//9 4'b00001010: tendata=4'd10;// 4'b00001011: tendata=4'd11;// 4'b00001100: tendata=4'd12; 4'b00001101: tendata=4'd13; 4'b00001110: tendata=4'd14; 4'b00001111: tendata=4'd15; default:tendata=4'bzzzz_zzzz; endcase end endfunction /*********十进制转LED段选函数*********/ 位的数字 ] datain; begin case(datain) 4'd0: leddata=8'b11000000;//0 4'd1: leddata=8'b11111001;//1 4'd2: leddata=8'b10100100;//2 4'd3: leddata=8'b10110000;//3 4'd4: leddata=8'b10011001;//4 4'd5: leddata=8'b10010010;//5 4'd6: leddata=8'b10000010;//6 4'd7: leddata=8'b11111000;//7 4'd8: leddata=8'b10000000;//8 4'd9: leddata=8'b10010000;//9 4'd10: leddata=8'b10111111;//- 4'd11: leddata=8'b01111111;//. default:leddata=8'bzzzz_zzzz; endcase end endfunction /********数码管扫描函数*************/ always@(posedge clk1ms) begin ) ; else begin ; case(number) 4'd0: begin );//个位 wei<=4'b1110; end 4'd1: begin );//十位 wei<=4'b1101; end 4'd2: begin );//百位 wei<=4'b1011; end 4'd3: begin );//千位 wei<=4'b0111; end 4'd4: begin duan<=leddata(4'd11);//. 显示小数点 wei<=4'b0111; end endcase end end endmodule |

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

AD_TLC549采集模拟信号的更多相关文章

- 基于FPGA的电压表与串口通信(上)

实验原理 该实验主要为利用TLC549采集模拟信号,然后将模拟信号的数字量通过串口发送到PC上上位机进行显示,使用到的TLC549驱动模块在进阶实验已经使用到了,串口模块在基础实验也已经使用到了,本实 ...

- 玩转X-CTR100 l STM32F4 l ADC 模拟数字转换

我造轮子,你造车,创客一起造起来!塔克创新资讯[塔克社区 www.xtark.cn ][塔克博客 www.cnblogs.com/xtark/ ] 本文介绍X-CTR100控制器 AD转换接 ...

- 东芝线阵CCD芯片TCD1305DG驱动时序设计

最近在做微型光谱仪,用到了东芝的CCD芯片TCD1305DG,该芯片是单行3648像素,输出信号是时间上离散的模拟信号,典型输出速率为0.5M,即每2000ns输出一个像素值(模拟信号),芯片内部集成 ...

- 手把手教系列之IIR滤波器设计

[导读]:在嵌入式系统中经常需要采集模拟信号,采集模拟信号的信号链中难免引入干扰,那么如何滤除干扰呢?今天就来个一步一步描述如何设计部署一个IIR滤波器到你的系统. 何为IIR滤波器? 无限冲激响应( ...

- (stm32f103学习总结)—ADC模数转换实验

一.STM32F1 ADC介绍 TM32F103 系列一般都有 3 个 ADC,这些 ADC 可以独立使用,也可 以使用双重(提高采样率).STM32F1 的 ADC 是 12 位逐次 逼近型的模拟数 ...

- 6.MIL采集和实时显示

前面讲到的都是离线的图像获取方法,实际中我们做机器视觉都是在线采集图像和处理,处理结果决定了计算机要给出的控制信号如电机运动等,这样就实现了实时视觉反馈运动.MIL中的采集需要Matrox采集板卡的支 ...

- FPGA在AD采集中的应用

AD转换,也叫模数转换,是将模拟信号转换为数字信号.目前包括电脑CPU,ARM,FPGA,处理的信号都只能是数字信号,所以数据信号在进入处理芯片前必须要进行AD转换. 在高速的AD转换中,FPGA以其 ...

- 关于esp32的ADC采集

对于ADC采集 程序源码如下: /* ADC1 Example This example code is in the Public Domain (or CC0 licensed, at your ...

- 关于海康视频采集卡的简介---基于pci的插潮采集卡

vga 640x480 qvga vga的1/4,宽高分别是vga的一半 (1)采集类型 海康威视 DS-2CE16A2P-IT3P 700TVL 1/3" DIS ICR 红外防水筒型摄像 ...

随机推荐

- Sublime Text 2 windows8安装插件失败解决

事件是这样的: 1.安装Package Control组件后, 2.调出Install Package选项安装插件,状态栏显示成功, 3.但打开Packages目录也看不到,Sublime插件管理也没 ...

- jquery点击切换背景色

刚在自己的前端技术群里有个小伙伴儿问到这个问题,点击的时候进行红色背景和白色背景的切换,然后我就临时想到了一个解决方法,在这里记录一下吧,希望还有别的刚学习前端的小伙伴儿能用到,大神就请绕道咯!另外提 ...

- 使用jq插入节点

.append()和.appendTo()两种方法功能相同,主要的不同是语法——内容和目标的位置不同 append()前面是要选择的对象,后面是要在对象内插入的元素内容 appendTo()前面是要插 ...

- iOS UITabBarController的使用

UITabBarController 和 UINavigationController 几乎是iOS APP的标配. UITabBarController分栏(标签栏)控制器, 和UINavigati ...

- crm on premise IFD 部署下提供oauth 2.0 集成自定义应用

很多情况下我们的CRM系统会和弟三方应用集成,一般情况我们会开发一个中间站点来提供web api 给弟三方应用. 参考:http://alexanderdevelopment.net/post/201 ...

- JavaScript异步编程(1)- ECMAScript 6的Promise对象

JavaScript的Callback机制深入人心.而ECMAScript的世界同样充斥的各种异步操作(异步IO.setTimeout等).异步和Callback的搭载很容易就衍生"回调金字 ...

- 【代码笔记】iOS-获得设备型号

一,代码. - (void)viewDidLoad { [super viewDidLoad]; // Do any additional setup after loading the view. ...

- python之面向对象与构造函数

一.面向对象介绍 不同的编程范式本质上代表对各种类型的任务采取的不同的解决问题的思路, 大多数语言只支持一种编程范式, 当然也有些语言可以同时支持多种编程范式. 两种最重要的编程范式分别是面向过程编程 ...

- sql tuning advisor使用

DB tuning advisor是创建优化任务,对某些sql数据库进行分析,并尽量给出优化建议的一个强大的数据库工具. 自己平时几乎没用过这玩意,所以来测一测用法,其实对于一些sql一筹莫展的时候跑 ...

- mapreduce导出MSSQL的数据到HDFS

今天想通过一些数据,来测试一下我的<基于信息熵的无字典分词算法>这篇文章的正确性.就写了一下MapReduce程序从MSSQL SERVER2008数据库里取数据分析.程序发布到hadoo ...