IP核——PLL

一、Quartus II创建PLL

1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager

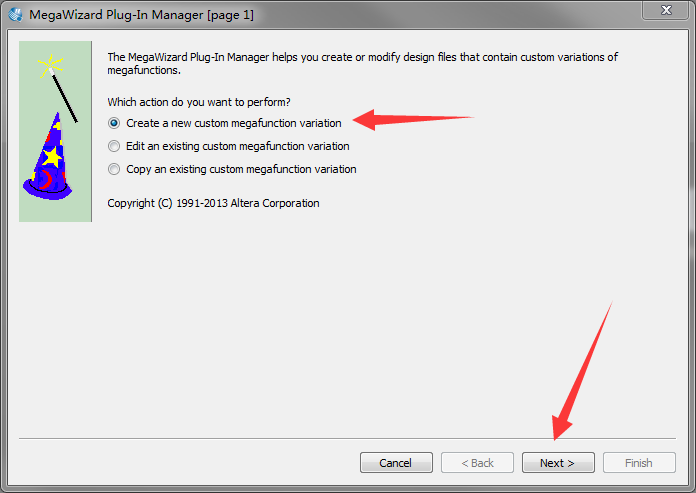

2.弹出创建页面,选择Creat a new custom megafunction variation,点Next

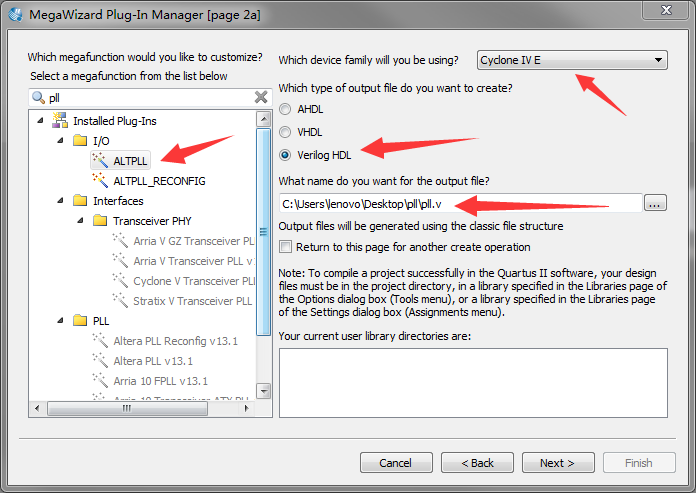

3.选择IP核,可以直接搜索pll,选择ALTPLL,右上方选择器件型号,语言选成Verilog,再填写一下路径名字,点Next,后面就是参数设置了。

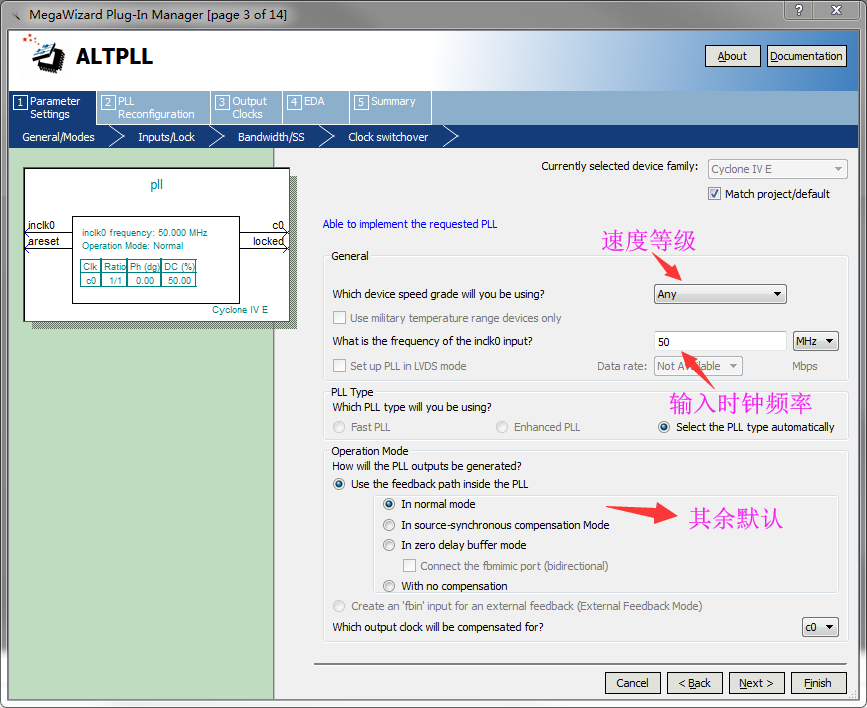

4.设置输入时钟频率,Next

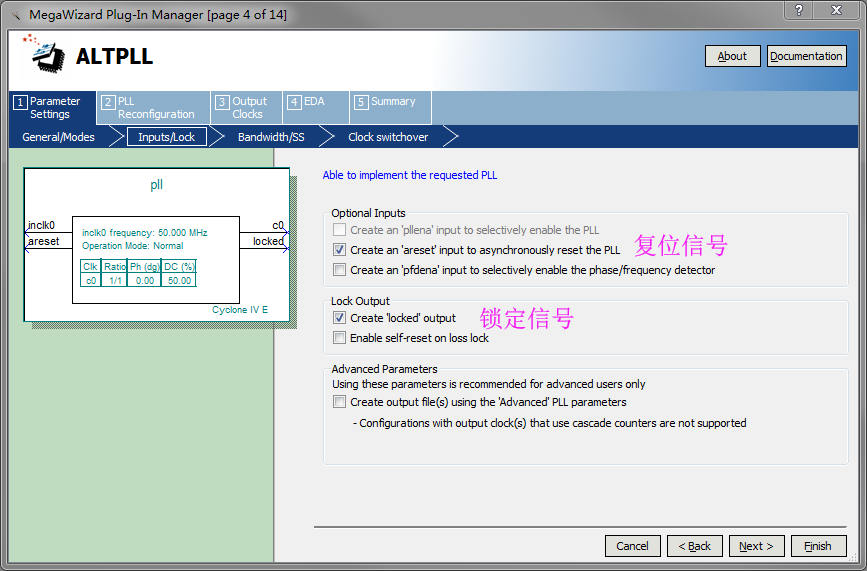

5.复位信号和锁定信号,锁定信号是指为1时,时钟就是稳定输出的状态,一般使用不勾选也行。Next

6.默认,Next

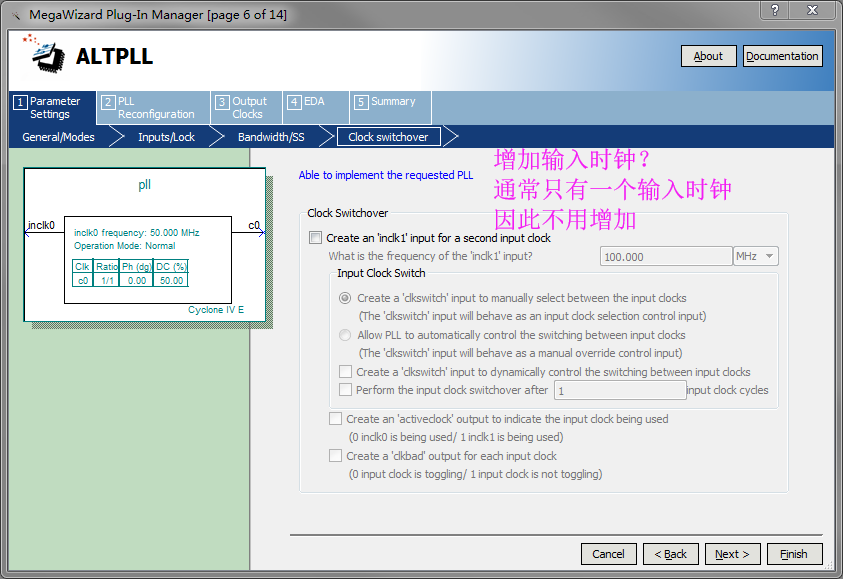

7.增加输入时钟,一般只有一个输入时钟,只用inclk0即可,因此无需增加,Next

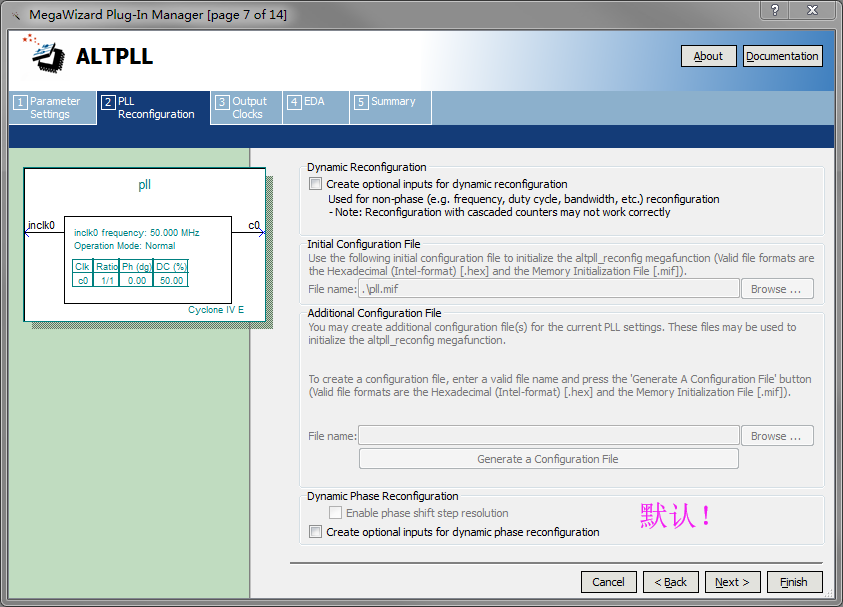

8.默认,Next

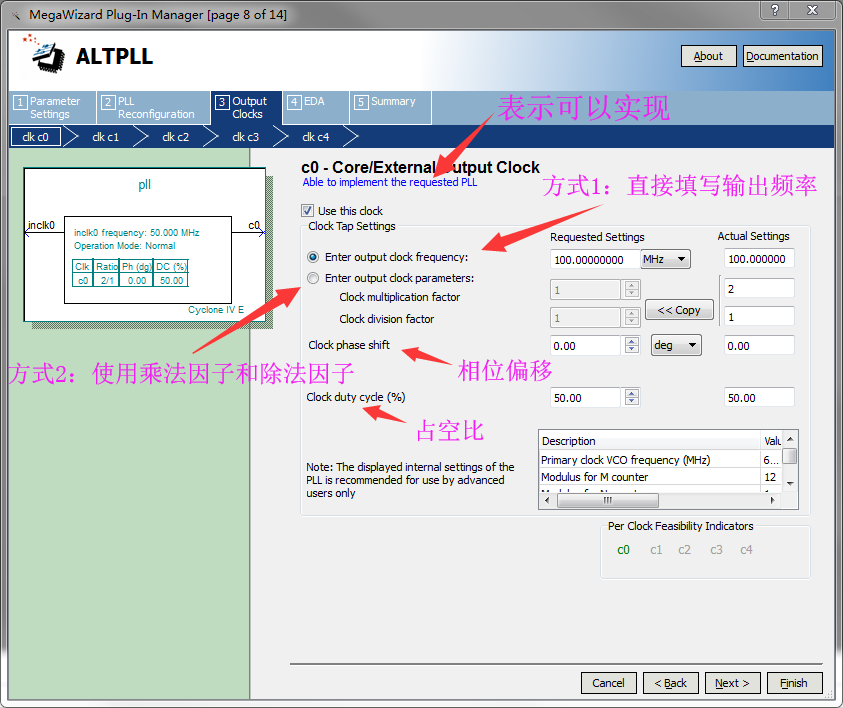

9.设置输出时钟,Next

10.后面是c1,c2,c3,c4,说明总的支持5个输出时钟,我们需要几个填几个就行,Next

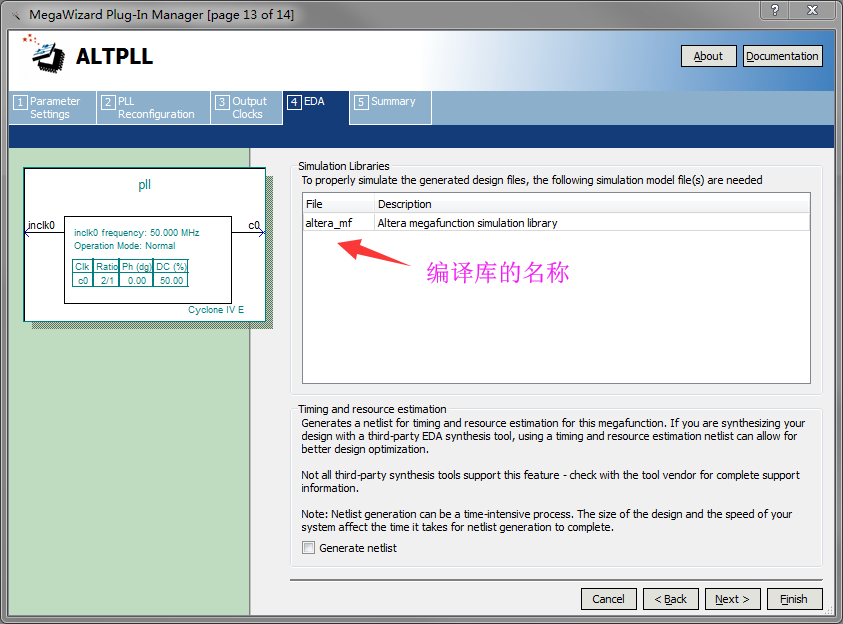

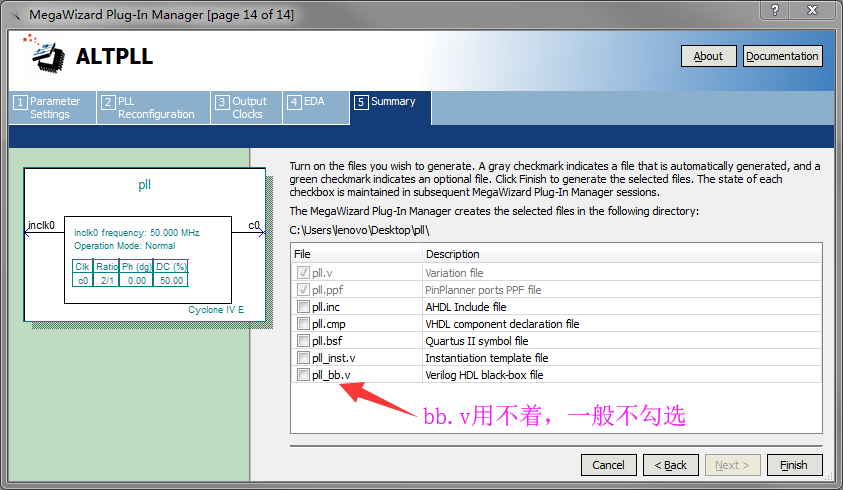

11.告诉你此IP核的编译库是什么,Next

12.输出的文件列表,除了正常IP核,还可以选择例化文件,注意bb.v文件用不到,一般是不勾选的。之后点finish就生成IP核了。

ps

1.Modelsim联合仿真ip核:quartus正常调用Modelsim就行

2.Modelsim独立仿真ip核:上面提示了仿真库名称,该仿真库可以在你的quartus安装目录下搜索到,把它复制出来,和其他文件一起添加到Modelsim中即可。

二、ISE

1.创建

1.创建ISE工程,IP核需要在ISE工程里面进行调用。点击Tools---Core Generator...

2.在新弹出来的界面中创建一个属于IP核的工程:file---new project,并填写文件存储位置和文件名称,一般为ipcore_dir文件夹,点击保存

3.弹出的Part处填写器件的系列、型号、封装以及速度等级,Generation处设置语言为Verilog,点击OK

4.点击文件夹,找到FPGA Features and Design---Clocking---Clocking Wizard,(也可以直接搜索)双击打开,进行参数设置

5.设置模块名和输入的时钟频率,Next

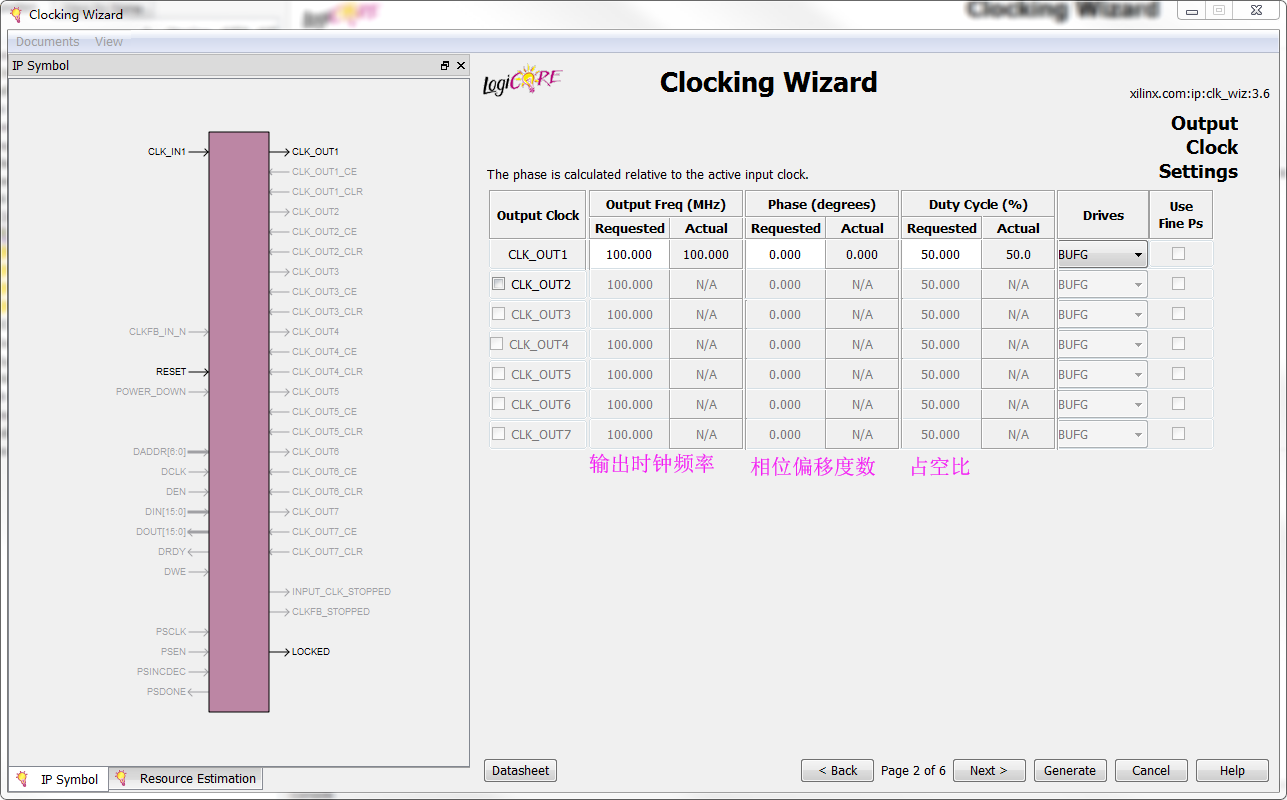

6.设置输出的时钟频率,还可以进行相位偏移度数和占空比,Next

7.设置控制信号,一般的设计不勾选就行,Next

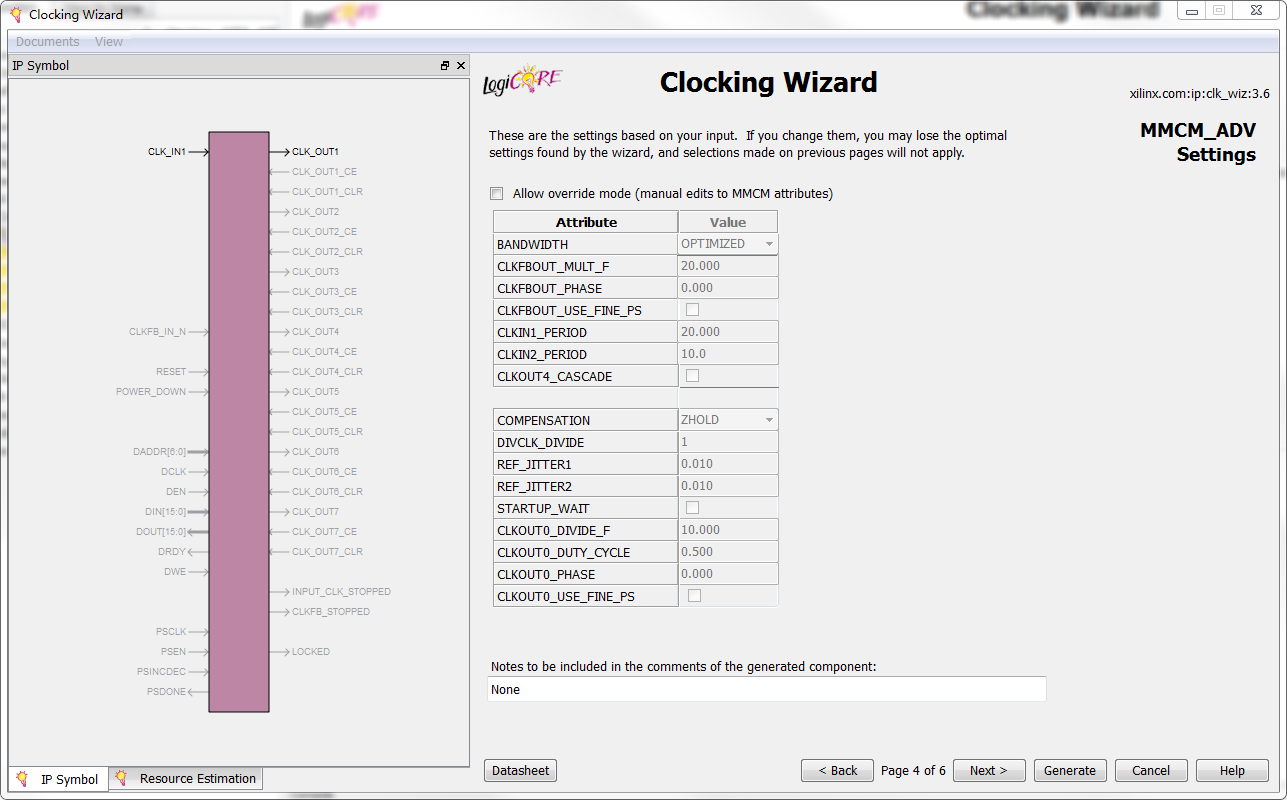

8.预览页面,Next

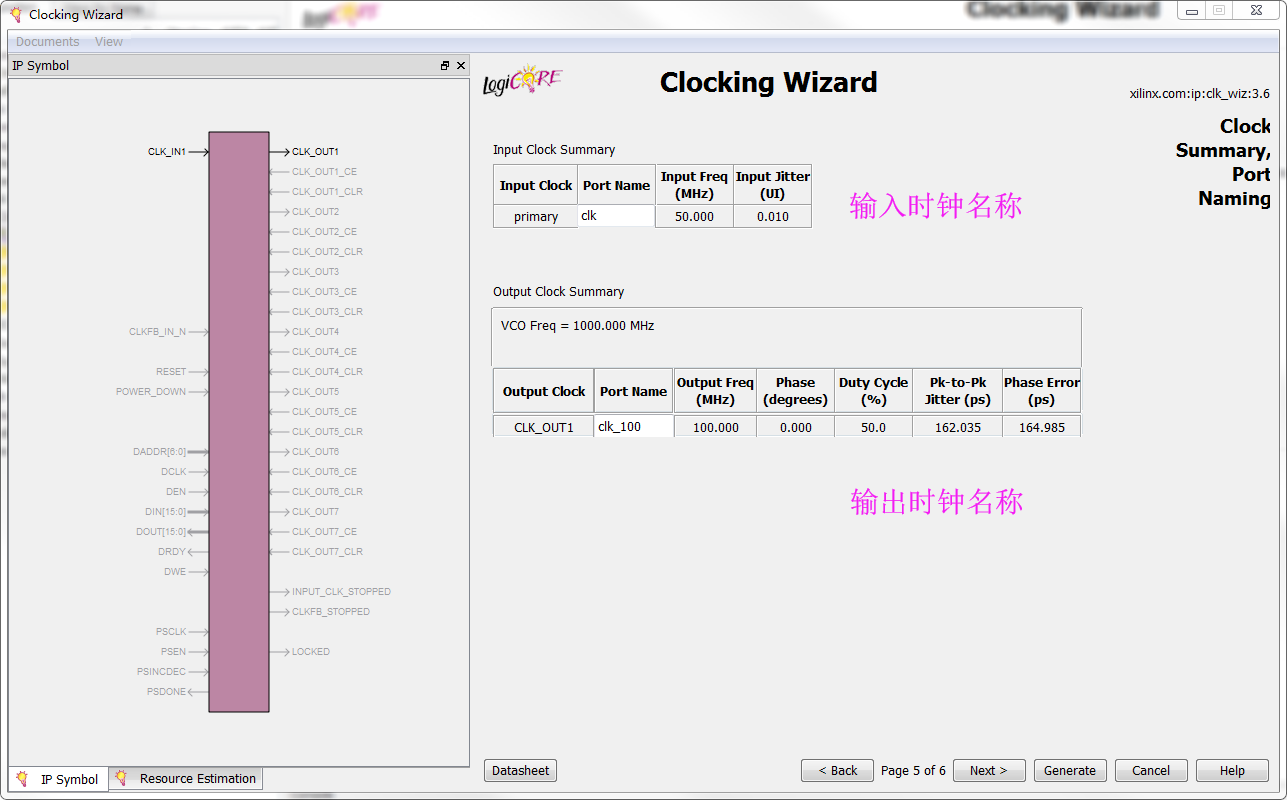

10.设置输入时钟和输出时钟的信号名称,Next

11.预览页面,点击Generate,静静等待IP核生成,生成后关闭弹出的readme.pll页面,关闭Core Generator页面。

2.使用

1.需要把创建好的IP核添加到工程中,创建IP核会生成一些文件,主要看以下三种文件:

①pll.v:IP核模块,看看里面的接口就行,不需要关注具体的代码含义

②pll.xco:进行内部优化后的IP核模块,我们把这个添加到工程中

③pll.veo:此IP核的例化模板文件

2.选中工程,添加pll.xco

3.选中工程,右键New Source,选中Verilog Test Fixture,填写名称和保存路径,一路Next。

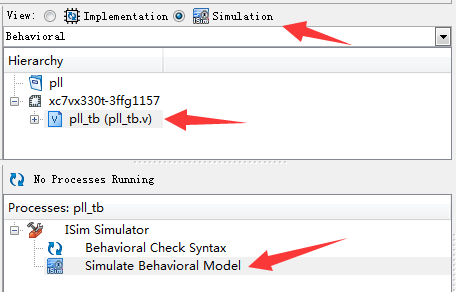

4.主页面切换至Simulation,可以看到生成了testbench文件,但是没有时钟驱动,我们设计一下。

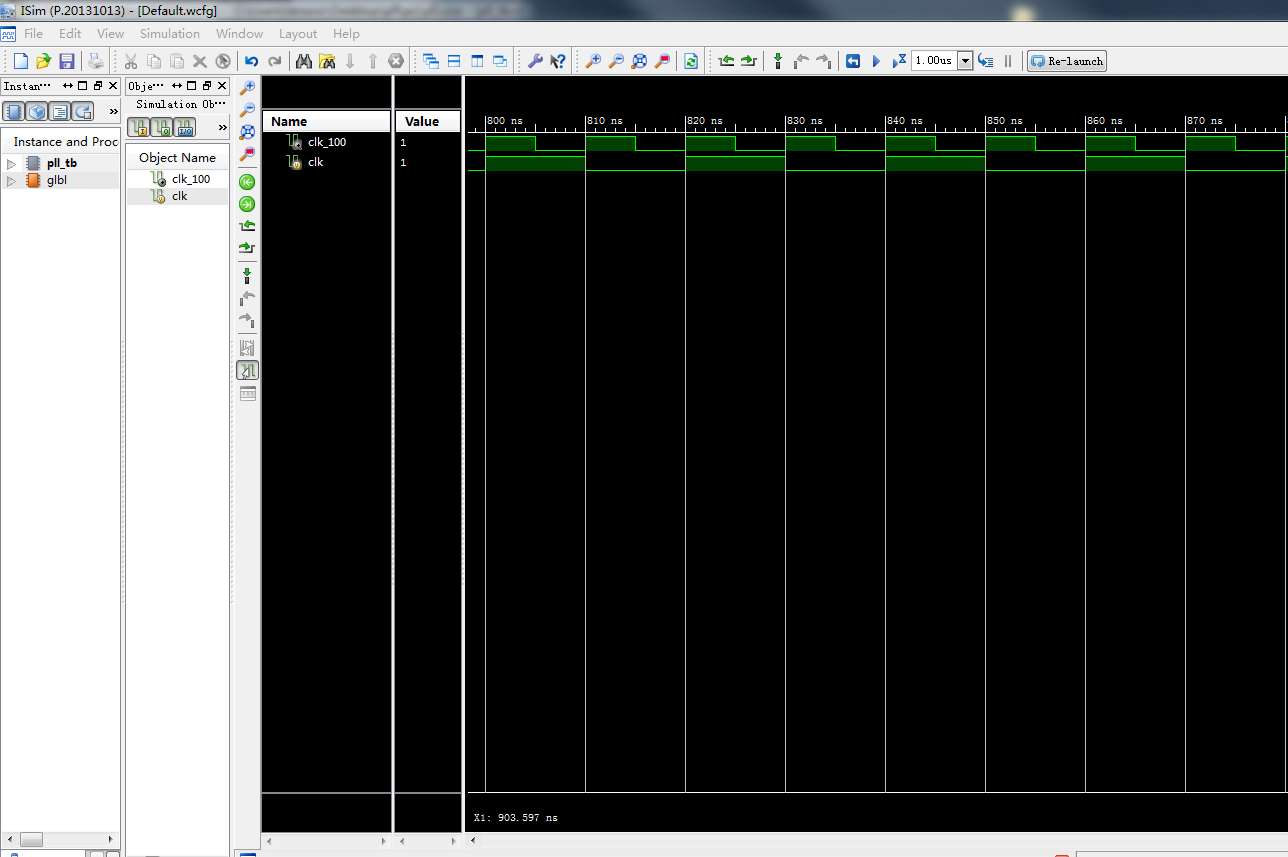

5.点击一下tb文件,下面进程栏中就出现了仿真工具,我们点击Simulate Behavioral Model,即可打开Isim,自动出波形。

PS:ISE也可以直接关联Modelsim,但有ip核的话还需要一个编译库的漫长过程,详细情况可自行百度。

IP核——PLL的更多相关文章

- 如何用ModelsimSE仿真IP核-以PLL为例

我们之前介绍了如何使用Modelsim SE进行仿真和利用do文件的仿真方法,但是其中待仿真的模块是我们自己编写的Verilog模块,但是在实际工作中,我们的设计中会经常用到FPGA厂商给我们提供的现 ...

- FPGA VGA+PLL+IP核笔记

1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ.2.分辨率使用了800*600@72HZ.3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色.VGA图形基 ...

- 7 Series GTP IP核使用总结 IP核配置篇

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级.本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用.本文是 ...

- 7系列高速收发器总结 GTP IP核使用篇

上一篇7系列收发器博文讲解了GTP IP核的基本配置,本文继续分析如何将它使用起来.生成IP核后打开example design,先看看工程中包含的文件结构. 顶层文件下包含了gtp ip核系统顶层文 ...

- Mdoelsim10.4怎么脚本单独仿真ISE14.7 IP核

软件版本: Modelsim10.4SE ISE14.7 仿真IP:时钟管理IP(clock wizard) 流程: 1.对于Modelsim10.4SE,并不自带Xilinx家的仿真库,因此首先 ...

- xilinx IP核配置,一步一步验证Xilinx Serdes GTX最高8.0Gbps

版权声明:本文为博主原创文章,未经博主允许不得转载. https://blog.csdn.net/u010161493/article/details/77658599 目录(?)[+] 之前 ...

- Altera三速以太网IP核使用(下篇)--- 百兆网接口设计与使用

MAC IP核的主要作用是:实现数据链路层协议,分为TX方向与RX方向,TX方向实现的是在原包文的前面加上7个55和1个D5,RX方向则相反.在使用这个 MAC IP核之前,首先确认下自己使用的网卡是 ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- Altera DDR2 IP核学习总结2-----------DDR2 IP核的生成

打开IP核工具,然后选择Verilog HDL选项,填写路径,写入文件名DDR2_IP.V,点击next PLL reference clock frequency填入板子晶振的频率50MHZ,这里设 ...

随机推荐

- callbag js callback 标准-支持轻量级观测以及迭代

callbag 是一个js 的回调标准,方便开发支持观测以及迭代的代码 类似已经有好多的实现了 callbag-basics 比rxjs 以及xstream 还快 wonka 说明 基于标准的开发,对 ...

- Phalcon框架的编译安装 内存不足的解决办法

对症解决 有两种解决方法,一种是提升ECS系统内存.但是却要真金白银跟阿里云去购买的.另一种,则是手动创建swap交换文件.下面来介绍第二种方法. 第一步:首先确定系统是否已经开启swap交换分区: ...

- 洛谷 P4316绿豆蛙的归宿

题目描述 记f[i]表示经过i号点的概率. 那么点v从点u到达的概率=经过点u的概率/点u的出度.由于v可以由多个点走到,所以f[v]+=f[u]/out[u]. 计算f的过程可以在拓扑中完成,同时可 ...

- 一个100%Go语言的Web-Term-SSH 堡垒机项目

SSH-Fortress 1. What does it do? Make your cluster servers be more safe by expose your SSH connectio ...

- 用jquery做一个带导航的名单列表

代码: <!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8 ...

- mysql 升序降序

默认不指定,order by 按照升序排列. asc:升序 desc:降序

- edusoho上传视频弹出abort之解决方案

错误描述:edusoho上传如avi.mp4等容量大的图片(如100m以上或500m等)弹出abort提示框 原因:是因为web服务器apache默认上传文件有限制导致的 解决办法如下: (1)首先修 ...

- axios跨域请求报错:Request header field content-type is not allowed by Access-Control-Allow-Headers in preflight response.

在做项目时,用到axios,数据用post提交时,老是报错,错误提示为: Access to XMLHttpRequest at 'http://127.0.0.1:3000/api/add' fro ...

- epoll 或者 kqueue 的原理是什么?

来自知乎:http://www.zhihu.com/question/20122137 epoll 或者 kqueue 的原理是什么? 为什么epoll和kqueue可以用基于事件的方式,单线程的实现 ...

- arcgis python 获得硬件id

import time import wmi, zlib def get_cpu_info(): tmpdict = {} tmpdict["CpuCores"] = 0 c = ...