转:(WIN)S04-CH01 PCIE XDMA开发环境搭建以及环路测试

摘要: 这一章开始主要介绍 XILINX FPGA PICE IP XDMA IP的使用。XDMA IP使用部分教程分LINUX 篇和WINDOWS篇两个部分。通过实战,面向应用,提供给大家 XILINX FPGA PCIE 应用解决方案。

软件版本:VIVADO2017.4

操作系统:WIN7/WIN10 64bit

硬件平台:XILINX FPGA MK7160FA

米联客(MSXBO)论坛:www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问!!

1.1 课程介绍

这一章开始主要介绍 XILINX FPGA PICE IP XDMA IP的使用。XDMA IP使用部分教程分LINUX 篇和WINDOWS篇两个部分。通过实战,面向应用,提供给大家 XILINX FPGA PCIE 应用解决方案。

本教程以MK7160FA作为样机测试。在正式开始教程内容前,有必要把MK7160FA开发板的特点说明下。这是一款高性价比的FPGA开发板。带PCIE接口,四路SFP光通信接口,双路千兆以太网口,1路HDMI输入,1路HDMI输出,1路串口,1路USB3.0接口。支持MSXBO(米联客)FEP标准扩展接口。采用的CPU型号为XC7K160t-FGG676。PL端搭载64bit 2GB DDR3内存,FPGA读写PL端DDR支持的最大数据时钟为1600M,可以进行更多复杂的开发任务。

教程的内容完全适合其他开发板。如果读者使用过程中遇到问题,可以在我们讨论课程网页留言(米联客(MSXBO)论坛www.osrc.cn答疑解惑专栏开通,欢迎大家给我提问)。我们会在论坛上公布相关课程内容和源码。

1.2 XDMA 概述

Xilinx 提供的DMASubsystem for PCIExpressIP是一个高性能,可配置的适用于PCIE2.0,PCIE3.0 的SG 模式 DMA,提供用户可选择的 AXI4 接口或者 AXI4-Stream接口。一般情况下配置成 AXI4 接口可以加入到系统总线互联,适用于大数据量异步传输,通常情况都会使用到 DDR,AXI4-Stream 接口适用于低延迟数据流传输。

XDMA 是SGDMA,并非Block DMA,SG 模式下,主机会把要传输的数据组成链表的形式,然后将链表首地址通过BAR 传送给XDMA,XDMA 会根据链表结构首地址依次完成链表所指定的传输任务。

1.3 XDMA 提供如下接口:

- AXI4、AXI4-Stream,必须选择其中一个,用来数据传输

- AXI4-Lite Master,可选,用来实现PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可用来读写用户逻辑寄

存器

- AXI4-Lite Slave,可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA

内部寄存器,不会映射到BAR

- AXI4 Bypass 接口,可选,用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输

1.4 XDMA IP 配置

Mode:配置模式,选择 Advanced 高级配置

Lane Width:MK7160FA 支持X4

Max Link Speed:选择5.0GT/s 即PCIE2.0

Reference Clock :100MHZ,参考时钟 100M

DMA Interface Option:接口选择 AXI4 接口

AXI Data Width:128bit,即 AXI4 数据总线宽度为128bit

AXI Clock :125M,即AXI4 接口时钟为 125MHZ

PCIE ID 配置

PCIE BAR 配置,这里面的配置比较重要

首先使能 PCIE to AXI Lite Master Interface ,这样可以在主机一侧通过PCIE 来访问用户逻辑侧寄存器或者其他 AXI4-Lite 总线设备

映射空间选择 1M,当然用户也可以根据实际需要来自定义大小。

PCIE to AXI Translation:这个设置比较重要,通常情况下,主机侧PCIE BAR 地址与用户逻辑侧地址是不一样的, 这个设置就是进行BAR 地址到AXI 地址的转换,比如主机一侧 BAR 地址为0,IP 里面转换设置为 0x80000000, 则主机访问 BAR 地址 0 转换到AXI LIte 总线地址就是0x80000000

DMA Bypass 暂时不用

PCIE 中断设置

User Interrupts:用户中断,XDMA 提供16 条中断线给用户逻辑,这里面可以配置使用几条中断线。

Legacy Interrupt:XDMA 支持 Legacy 中断

选择 MSI 中断

注意:MSI 中断和 MSI-X 中断只能选择一个,否则会报错,如果选择了 MSI 中断,则可以选择 Legacy 中断, 如果选择了 MSI-X 中断,那么 MSI 必须取消选择,同时Legacy 也必须选择None。此 IP 对于7 系列设置有这么 个问题,如果使用Ultrascale 系列,则可以全部选择

配置DMA 相关内容

Number of DMA Read Channel(H2C)和Number of DMA Write Channel(C2H)通道数,对于PCIE2.0 来说最大 只能选择 2,也就是 XDMA 可以提供最多两个独立的写通道和两个独立的读通道,独立的通道对于实际应用中 有很大的作用,在带宽允许的前提前,一个PCIE 可以实现多种不同的传输功能,并且互不影响。这里我们选择1

Number of Request IDs for Read (Write)channel :这个是每个通道设置允许最大的 outstanding 数量,按照默 认即可

配置完成以后,点击 Run Block Auto,可以看到之前的配置信息,如果有发现和目标配置不一样的,需要手动 修改,点击 OK,完成配置

配置完成以后,VIVADO 会自动进行必要的连接

到此为止,XDMA IP 配置就完成了只要再进行时钟和 GTP 约束即可。

1.5 MIG 7 SERIES 的配置

Step1:任单击 IP Catalog,选取 Memory Interface Generator(MIG 7 series)IP 添加到 Block design。双击 MIG 7 SERIES ,对这个 IP 进行配置。

双击生成的IP核

选择Create Design 单击NEXT

继续单击NEXT

选择DDR3 单击NEXT

设置MIG 内核时钟频率、内存型号、内存的数据位宽

设置MIG AXI4 最大支持的位宽,对4于片DDR 最大位宽为512bit

设置输入频率为200M

系统和参考时钟时钟选择no buffer,MIG低电平复位

Step9:终端阻抗选择40hms,设置DCI

选择Fixed Pin Out

根据原理图手动填写PIN 脚定义,或者选择Read XDC/UCF直接读入pin脚定义,本课程下提供了MK7160FA.ucf 的DDR 配置文件,直接读入既可。

填写完成后,先单击Validate再单击NEXT

继续单击NEXT

继续单击NEXT

继续单击NEXT

继续单击NEXT

最后单击Generate,至此MIG的配置完成

1.6 基础测试系统搭建

我们的测试目标是进行PCIE AXI4总线与外设进行读写操作,PCIE AXI4-Lite 总线进行用户逻辑寄存器或者其他 AXI4-Lite 总线设备访问操作。AXI4总线上挂载到MIG控制器DDR上去,实现对DDR的读写控制。

为此搭建系统为下图所示:

进行地址分配:

这里我们把挂在M_AXI上的DDR地址分配从0开始(对于widnows系统必须为0), M_AXI是需要进行DMA操作的。而M_AXI_LITE挂载的BRAM是需要进行BAR空间操作,所以地址设置为0x80000000和XMDA IP里面设置的地址对应。

1.7 WIN7/WIN10系统下开发环境搭建

请用户在我们提供的网盘里面下载 VS2015,WINSDK,WDK 开发包,这是经过我们验证的,如果 SDK 和

WDK 版本不匹配会造成编译失败。

首先是 VS2015 的安装,如果已经安装了 VS2010,或者其他版本,建议先进行卸载,卸载过程不要使用 360

等软件工具卸载,而是使用 VS 自带的卸载工具(注意:操作过程中可能会出现问题,导致该系统无论如何都无法

编译程序,本教程不对此情况负责,我们测试宿主机是一台刚刚安装了 WIN7/WIN10 系统的机器,为了避免因搭建环境而造成宿主机原系统算坏的情况,建议用户可以花几十块钱购买一块 320G 以下的硬盘,在新硬盘安装系统搭建环境测试)

大家请注意软件的安装顺序一定要是先安装vs2015再安装WINSDK,最后安装WDK。如果一不小心顺序错了,卸载干净后重新安装,否则肯定不会成功的。

这里一定要选择自定义,默认情况下是不安装 VC++语言的,不知道VS 是怎么搞的。

然后在编程语言里面勾选 vc++,vs2015 更新 3 也勾选上,否则也可能造成编译错误,这些错误主要是由于版本匹配问题引起的。下面就是一路安装,不多说了。安装好以后,记得去百度搜个序列号,你们懂得。

下面安装WINSDK。

最后安装WDK

接下来还有一项重要的设置,根据官方文档的说法,XDMA 的驱动没有提供一个验证过的证书,所以必须使用

测试模块才能安装驱动。

打开上面的连接,可以看到使用如下命令可以开关测试模式。

另外也可以采用禁用驱动签名的办法来安装没有签名的驱动,禁用驱动签名的办法,下面我们也会演示。首先还是采用测试模式下进行。

bcdedit /set testsigning on 打开测试模式

bcdedit /set testsigning off 关闭测试模式

在 WIN7/WIN10 系统下打开终端,一定要使用管理员权限

显示操作成功,电脑重启,可以在桌面的右下角看到,系统进入测试模式。

1.8 WIN7/WIN10下驱动程序编译以及安装

1.8.1 驱动编译(如果不想编译可以跳过)

Xilinx 提供的XDMA 驱动源码,直接编译可能会由于WPP 的原因导致编译失败,WPP 是驱动调试功能,用户可以自行修改,本教程中不使用 WPP 功能,同时对驱动源码进行了一些修改,可以直接使用,请参考我们提供的工程。工程文件如下:

driver 里面是驱动源码,其他项目都是应用程序。拿到工程以后,先进行清理,然后进行编译。

编译成功。然后可以在如下目录里面看到生成的驱动文件

可以在如下目录看到生成的应用程序文件

1.8.2 驱动安装

和纯FPGA的开发板不一样,ZYNQ一定要先用SDK烧录程序,烧写完成之后重启电脑,打开设备管理器,可以看到被识别倒是未驱动的PCIE 设备。

接下来进行驱动的安装,首先安装证书文件,XDMA.cer,双击安装即可。然后在设备管理器里面选择PCIE 设备,右击

更新驱动程序软件,选择浏览计算机查找驱动程序

选择生成驱动的 sys 目录下面的 XDMA 目录

到此,PCIE 驱动就安装完毕了。

1.9 WIN7/WIN10下 XDMA 应用程序测试

我们打开一个终端(如果双击运行会很快退出来),进入到上一节编译生成的应用程序目录找到xdma_rw.exe,这个应用程序是操作 pcie 的所有设备的,我们在终端只输入xdma_rw.exe,可以看到提示信息,告诉用户这个程序如何使用

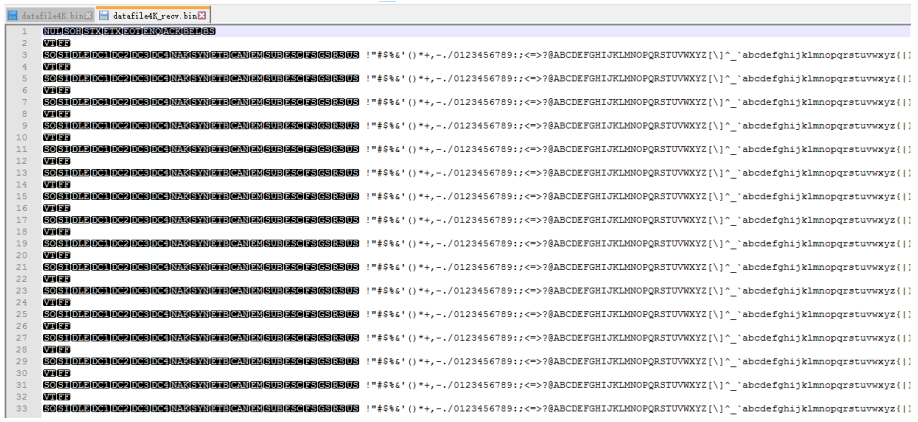

可以看到在当前目录有一个datafile4k.bin文件,那就测试一下将这个文件传输到 FPGA(BRAM),然后读出来。首先在终端输入指令:xdma_rw.exe h2c_0 write 0x0000000 -b -f datafile4K.bin -l 4096 意思就是使用h2c_0 设备以二进制的形式读取文件datafile4k.bin写入到BRAM内存地址0x0000000长度为4096字节。

接下来再读回来,使用命令 xdma_rw.exe c2h_0 read 0x0000000 -b -f datafile4K_recv.bin -l 4096

接下来我们可以使用 winhex 等软件来检查一下两个文件数据是否一直,经过检查,是一致的则说明传输功能正常。

转:(WIN)S04-CH01 PCIE XDMA开发环境搭建以及环路测试的更多相关文章

- 基于WDF的PCI/PCIe接口卡Windows驱动程序(1)-WDF概述及开发环境搭建

原文出处:http://www.cnblogs.com/jacklu/p/4619110.html 本科毕业设计是这方面的工作,所以想开几篇博客来介绍使用WDF开发PCI/PCIe接口卡的驱动程序方法 ...

- Cocos2dx-3.0版本 从开发环境搭建(Win32)到项目移植Android平台过程详解

作为重量级的跨平台开发的游戏引擎,Cocos2d-x在现今的手游开发领域占有重要地位.那么问题来了,作为Cocos2dx的学习者,它的可移植特性我们就需要掌握,要不然总觉得少一门技能.然而这个时候各种 ...

- Android配置----Android开发环境搭建

[声明] 欢迎转载,但请保留文章原始出处→_→ 生命壹号:http://www.cnblogs.com/smyhvae/ 文章来源:http://www.cnblogs.com/smyhvae/p/3 ...

- Appium-001-测试开发环境搭建(Android - Win7)

随着移动端 App 测试自动化的兴起,为更好的控制产品质量,越来越多的中大型公司开始了移动端的自动化测试.Appium 自动化测试技术也是我很早之前就想学习的一门技术,却一直没有比较空余的时间来学习( ...

- android 开发环境搭建 (转)

最近由于工作中要负责开发一款Android的App,之前都是做JavaWeb的开发,Android开发虽然有所了解,但是一直没有搭建开发环 境去学习,Android的更新速度比较快了,Android1 ...

- Android菜鸟的成长笔记(1)——Android开发环境搭建从入门到精通

原文:Android菜鸟的成长笔记(1)--Android开发环境搭建从入门到精通 今天在博客中看到好多Android的初学者对Android的开发环境的搭建不熟悉而导致不能进行学习,所以我决定自己写 ...

- 【java系列】java开发环境搭建

描述 本篇文章主要讲解基于windows 10系统搭建java开发环境,主要内容包括如下: (1)安装资料准备 (2)安装过程讲解 (3)测试是否安装成功 (4)Hello Word测试 1 安装 ...

- NDK在windows下的开发环境搭建及开发过程

在Android应用的开发工程中,不管是游戏还是普通应用,都时常会用到.so即动态链接库,关于.so是什么玩意儿,有什么好处,这个大家可以在网上查一下,本人不做过多解释..so本是linux下的文件类 ...

- angular开发环境搭建及新建项目

最近一个星期准备学习一下angular前端框架,因为之前在学习abp框架的时候,都要求前端要掌握angular,所以不得不回来恶补一下了,学习的过程有时间的话会记录在这里,方便以后复习. 闲言少叙,下 ...

随机推荐

- Collections集合工具类和可变参数

Collections常用的API: public static <T> boolean addAll(Collection<? super T> c, T... elemen ...

- AtCoder Regular Contest 069 D - Menagerie 枚举起点 模拟递推

arc069.contest.atcoder.jp/tasks/arc069_b 题意:一堆不明身份的动物排成一圈,身份可能是羊或狼,羊一定说实话,狼一定说假话.大家各自报自己的两边是同类还是不同类, ...

- Django学习day11随堂笔记

今日考题 """ 今日考题 1.简述自定义分页器的使用 2.forms组件是干什么用的,它的主要功能有哪些功能,你能否具体说说每个功能下都有哪些经常用到的方法及注意事项( ...

- ACID的实现原理

引言 ACID是事务的特点也是必须的要求,只有保证ACID事务的执行才不会出错,分别是原子性.一致性.隔离性和持久性.我们知道典型的MySQL事务是这样执行的: start transaction 开 ...

- 使用阿里云CDN后,php使用$_SERVER['HTTP_VIA']判断是否是移动端会出错

使用阿里云CDN后,php使用$_SERVER['HTTP_VIA']判断是否是移动端会出错 if (isset ($_SERVER['HTTP_VIA'])) return stristr($_SE ...

- linux新安装了php,但是使用mysqli连接数据库一直超时

centos7+mysql5.5+php5.6+nginx mysql php nginx都安装完成,然后启动了,网站也运行, 但是php文件中使用mysqli_connect时一直超时,有时也报错, ...

- git合并内容的1个方式

诉求 把自己的改动的文件合并到目标分支: 不想改那些不属于自己开发时出现的冲突: 操作 开发分支dev,要合并至master分支 1 所有改动都已提交,保持分支的干净状态(working tree c ...

- 织梦Call to a member function GetInnerText() on string

"include"-"customfields.func.php"文件,在第539行中把以下代码: $fvalue = trim($ntag->GetIn ...

- 使用Jmeter过程中遇到的问题

学习接口自动化测试框架或工具,UI自动化测试框架或工具,有时会觉得知识似乎比较零散,死记硬背不是一个好方法.一个学习的思路是思考使用这些框架或工具的时候,可能会遇到什么问题,遇到这些问题可以通过什么方 ...

- Python就业方向

0.WEB开发 Python拥有很多免费数据函数库.免费web网页模板系统.以及与web服务器进行交互的库,可以实现web开发,搭建web框架,目前比较有名气的Python web框架为Django. ...