自建AXI4的IP核的地址问题

自建AXI4的IP核的地址问题

1、问题概述

在AXI4中,对应的操作通过对对应的寄存器设置来完成。其中的寄存器又分为数据寄存器和地址寄存器。其中,如果只是想要操作数据的话,只需要使用数据寄存器即可。在自建AXI4的IP时,会选择数据寄存器的个数。在打开封装文件时也可以看到数据寄存器。一般是slv_reg0·····等编号。其中slv代表从机,reg0代表寄存器0.这里有一个如何操作寄存器的问题。

2、问题解决

可以看出,这个数据寄存器既可以接收AXI的数据,也可以发送数据到AXI上。这里的功能十分类似一个三态门。只不过这里的控制信号也是一个可控寄存器的输出。主机通过设置配置寄存器决定输入还是输出,通过地址读取或者写入数据。严格来说,如果要使用这个寄存器的作为输入输出口,是需要和控制信号也就是配置寄存器的状态关联的。比如,作为接收主机数据时的输入寄存器,该寄存器作为正常的输入口,可以直接输出到所需的PL模块。当作为发送数据到主机的输出口,则需要接受来自PL模块的信号。显然,这里是有矛盾的。一个寄存器不可能同时有两个输入和输出。所以,虽然AXI总线是可以设置从机的通信模式:接收或者发送,但是,在设计时,具体到某个数据寄存器时,只能作为输入或者输出,不可更改。作为向主机输入的输出寄存器,甚至可以直接采用wire型变量,实时等待发送。而作为向主机接收数据的输入寄存器,只需要用reg向其他变量赋值即可将数据导出到PL。显然,发送到主机是比较困难的,需要等待主机的读取。主机是可以对每个特定的寄存器设置输入输出模式的。所以在PS端需要提前设置模式以便寄存器正确的工作。当然,如果一定要实现某个寄存器的输入输出灵活转换,则可以牺牲另外一个寄存器用于配置PL的寄存器。如果对AXI总线的信号比较熟悉的话,也可以直接读取对应的从地址进行判断,这就是需要更加复杂的结构。现在暂时不涉及。

3、问题总结

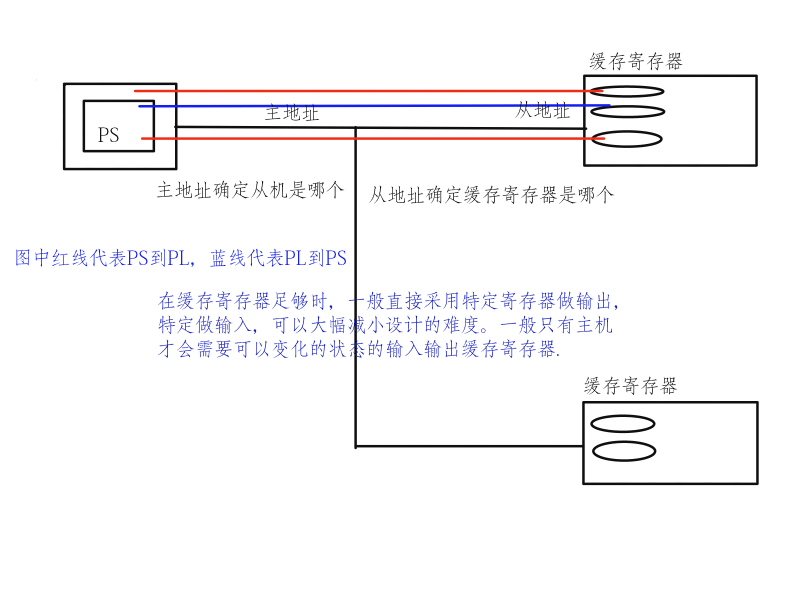

这里主要通过对主地址和从地址的对应的物理信号出发,分析所需要的数据操作。下面给出一个AXI数据传输的关系图。

这只是用于理解PS端设计时的示意图。如果想要完全理解AXI的从机逻辑,必须要五个通道和辅助的模块出发。后面会逐渐涉及数据的读写、地址的读写、响应信号的构建、优先级判断、数据缓存等各种细节的问题。

自建AXI4的IP核的地址问题的更多相关文章

- 基于AXI4总线卷积FPGA加速IP核的尝试

本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面.使用的硬件平台是Zedboard. 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块 ...

- Xilinx IP核的根目录地址,有datasheet 和仿真相关的资料

C:\Xilinx\14.7\ISE_DS\ISE\coregen\ip\xilinx\dsp\com\xilinx\ip Xilinx IP核的根目录地址,有datasheet 和仿真相关的资料

- NIOS II 自定义IP核的静态地址对齐和动态地址对齐

如果使用静态地址对齐(每个寄存器在Avalon总线上占4个字节的地址)设置IP使用静态地址对齐的方式为,在hw.tcl脚本里加上一局话:set_interface_property as addres ...

- AXI-Lite总线及其自定义IP核使用分析总结

ZYNQ的优势在于通过高效的接口总线组成了ARM+FPGA的架构.我认为两者是互为底层的,当进行算法验证时,ARM端现有的硬件控制器和库函数可以很方便地连接外设,而不像FPGA设计那样完全写出接口时序 ...

- 理解AXI Quad Serial Peripheral Interface(SPI) IP核

reference : PG153-AXI Quad SPI v3.2 LogiCORE IP Product Guide.pdf 在使用MicroBlaze过程中,调用了此IP,所以有必须仔细学 ...

- Vivado中xilinx_BRAM IP核使用

Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3 BRAM IP核包括有5种类型: Single-port RA ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- (转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)

原地址modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核) 1.打开D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\compxlibgui.e ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

- Lattice 的 Framebuffer IP核使用调试笔记之IP核生成与参数设置

本文由远航路上ing 原创,转载请标明出处. 这节笔记记录IP核的生成以及参数设置. 先再IP库里下载安装Framebuffer 的ipcore 并安装完毕. 一.IP核的生成: 1.先点击IP核则右 ...

随机推荐

- Java判断一个字符串中是否包含数字

知识点 本例考察以下Java知识点: 正则表达式 关于正则表达式: https://www.runoob.com/java/java-regular-expressions.html Characte ...

- mdbook安装使用实录

简介 mdbook是一个基于Rust的电子书系统,效果类似于gitbook.本人写图文文章一直都采用的印象笔记,但是写系列教程的情况不方便管理.因此引入mdBook,分享一下基本安装使用过程及遇到的问 ...

- 【Android 逆向】【攻防世界】easy-apk

apk 安装到手机,随便输入点内容,提示错误 2. apk 拖入到jadx中看看 public class MainActivity extends AppCompatActivity { /* JA ...

- Java面向对象之内部类的几类使用场景

介绍 Java内部类是一种特殊的类,它定义在另一个类的内部.内部类提供了许多有用的特性,包括访问外部类的私有成员.隐藏实现细节以及实现回调接口等.以下是Java内部类的一些常用场景及其举例说明: 回调 ...

- 【Azure API 管理】是否可以将Swagger 的API定义导入导Azure API Management中

问题描述 是否可以将Swagger 的API定义导入导Azure API Management中? 操作步骤 是的,可以通过APIM门户导入单个的API Swagger定义文件.具体步骤如下: 第一步 ...

- vscodeC++生成配置文件

参考 https://www.cnblogs.com/harrypotterisdead/p/14207866.html 和 https://www.cnblogs.com/heyiping/p/14 ...

- IISExpress 跨域cookie的奇怪问题

测试环境 WIN10,IIS 10,IISExpress 10,Chrome 120,Microsoft Edge 114 网站A 端口7001 只有1个Default.aspx,无前端代码.逻辑很简 ...

- Android APP 渗透测试---总结

1.apk反编译得到源代码 使用编译软件 dex2gar 和 jdgui.jar 对Android APP软件进行反编译.具体步骤如下: (1)首先将APK文件后缀改为zip并解压,得到其中的clas ...

- C++ Qt开发:QHostInfo主机地址查询组件

Qt 是一个跨平台C++图形界面开发库,利用Qt可以快速开发跨平台窗体应用程序,在Qt中我们可以通过拖拽的方式将不同组件放到指定的位置,实现图形化开发极大的方便了开发效率,本章将重点介绍如何运用QHo ...

- nginx 和 mysql 安装

先附上大云资料: 安装nginx. 登录弹性云服务器. 执行以下命令,下载对应当前系统版本的nginx包. wget http://nginx.org/packages/centos/7/noarch ...