Verilog的非阻塞语句放到顺序块中,综合出来怎样的逻辑电路?

情境:

FPGA里面计数器需要复位(计数值置零),与计数器状态有关的行为是状态机控制的,即状态机为CLEAR_TIMER状态时,计数器才完成清零动作。

清零有两个条件:(1)计数器值溢出(达到OVF门限);(2)清零信号有效(1有效)。这两个条件是独立的,没有先后关系的约束。

问题是:如何写Verilog语句,才使得这两个触发的优先级相同?

有两个思路:

一个是:

always@(posedge clk)begin

if(!rst_n)begin

stat_preload <= STAT_IDLE;

end

else begin

//*** Combined Transition

if((tim_cnt >= TIIM_OVF) || (1'b1 == tim_rst))begin // OR

stat_preload <= STAT_CLEAR_TIMER;

end

else begin

stat_preload <= stat_preload; // Status Latch

end

end

end

另一个:

always@(posedge clk)begin

if(!rst_n)begin

stat_preload <= STAT_IDLE;

end

else begin

//*** Separate Transition

if(tim_cnt >= TIM_OVF)begin

stat_preload <= STAT_CLEAR_TIMER;

end

else begin

stat_preload <= stat_preload; // Stay

end

if(1'b1 == tim_rst)begin

stat_preload <= STAT_CLEAR_TIMER;

end

else begin

stat_preload <= stat_preload; // Stay

end

end

end

这两种写法的区别在于:第一种,状态转移语句放在两个条件参与的单个if选择结构里面;第二种,状态转移语句放在分别的两个if选择结构里面。

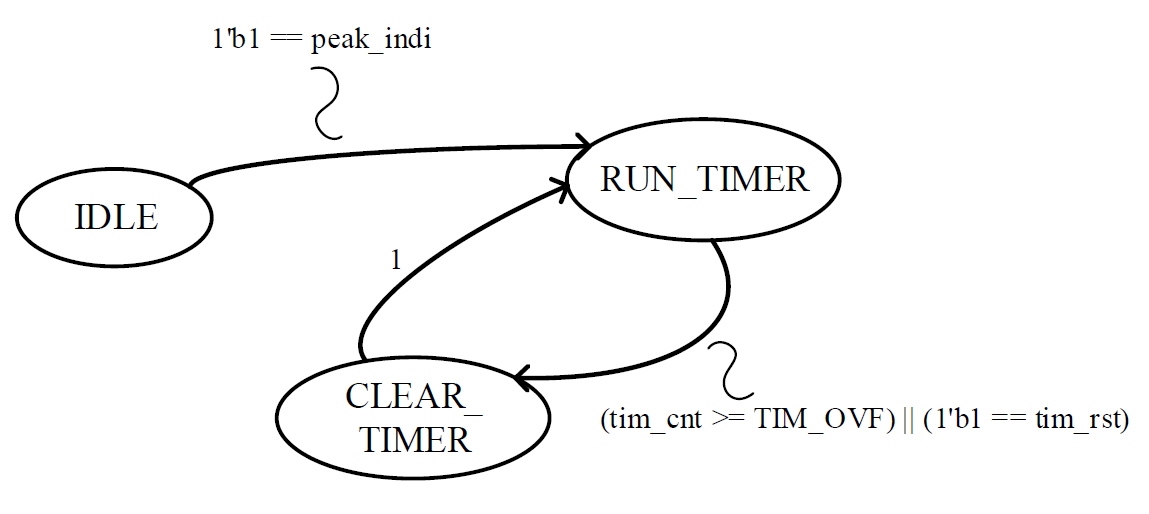

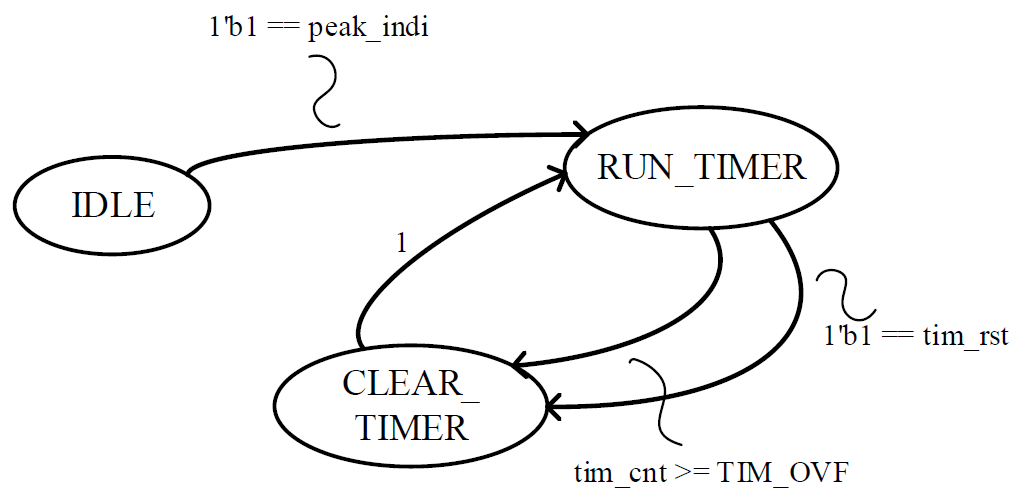

状态转移图中表现为这样的两种情况:

实现和测试:

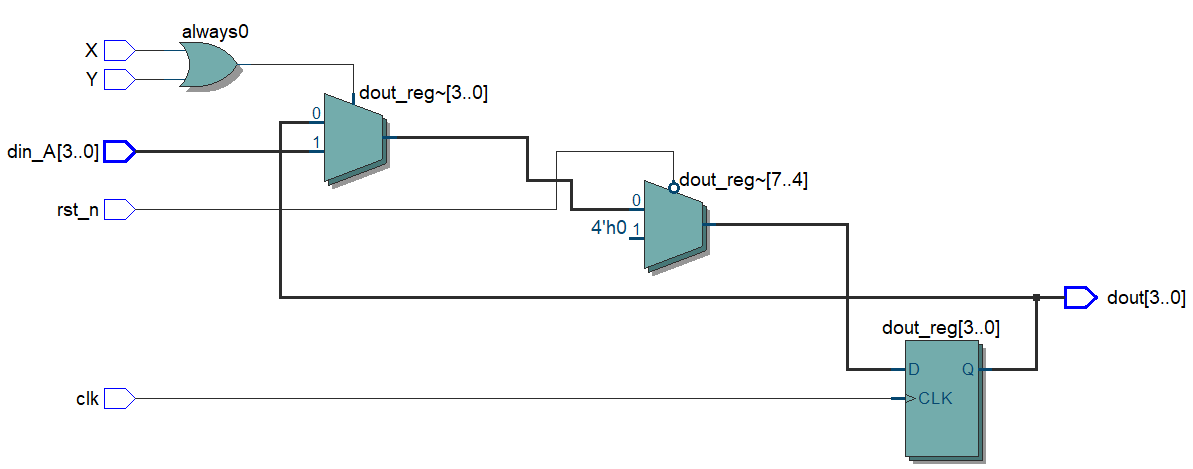

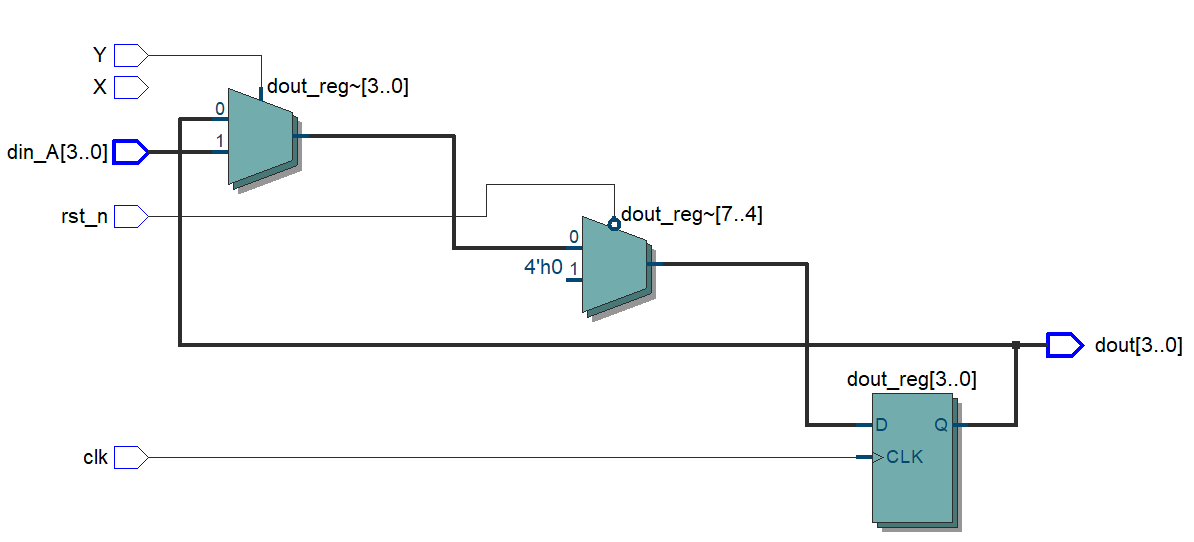

上述两种的代码和综合结果如下:

module top(

rst_n,

clk,

X,

Y,

din_A,

dout

); //****************************************

// Port Def.

//****************************************

input wire rst_n;

input wire clk; input wire X; // Conditions

input wire Y; input wire[:] din_A; output wire[:] dout; //****************************************

// Variables

//****************************************

reg[:] dout_reg; //****************************************

// Behaviour

//**************************************** assign dout = dout_reg; always@(posedge clk)begin

if(!rst_n)begin

dout_reg <= 'b0;

end

else begin

if(('b1 == X) || (1'b1 == Y))begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

end

end endmodule

module top(

rst_n,

clk,

X,

Y,

din_A,

dout

); //****************************************

// Port Def.

//****************************************

input wire rst_n;

input wire clk; input wire X; // Conditions

input wire Y; input wire[:] din_A; output wire[:] dout; //****************************************

// Variables

//****************************************

reg[:] dout_reg; //****************************************

// Behaviour

//**************************************** assign dout = dout_reg; always@(posedge clk)begin

if(!rst_n)begin

dout_reg <= 'b0;

end

else begin

if('b1 == X)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == Y)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

end

end endmodule

综合器是Quartus 15.1内置的。

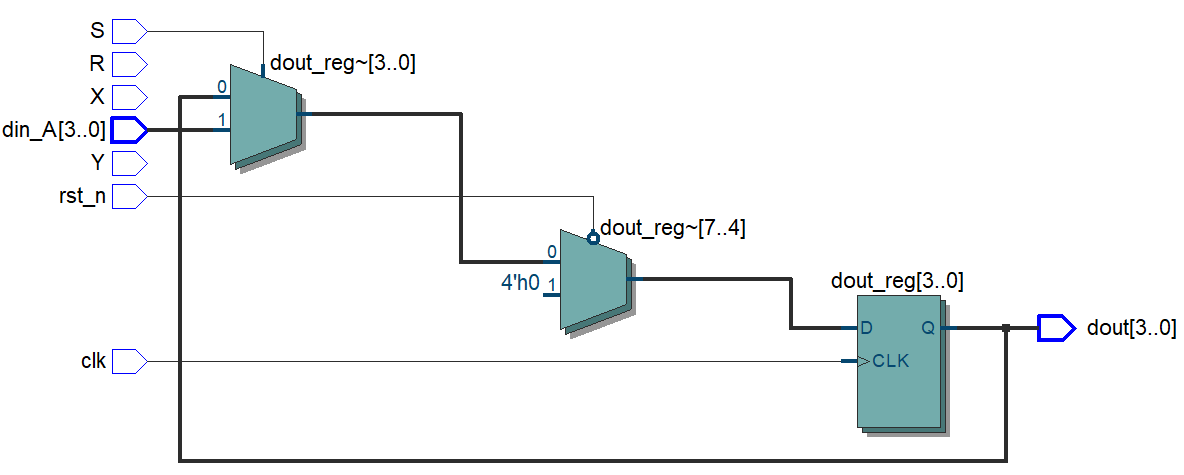

可以看到,第二种写法的综合结果让输入信号X没有驱动逻辑了,这样就与需求不符。

原因是什么?

第二种(分开if)情况下,虽然赋值语句都是非阻塞的<=,但是由于if语句放在顺序的begin::end结构内,所以判断和执行都是顺序处理的,状态转移和状态停留操作是一模一样的,所以X条件被省略了。

为了验证这个结论,在X,Y两个条件的基础上再加R,S两个条件,进行X,Y,R,S的顺序if,然后查看结果:

module top(

rst_n,

clk,

X,

Y,

R,

S,

din_A,

dout

); //****************************************

// Port Def.

//****************************************

input wire rst_n;

input wire clk; input wire X; // Conditions

input wire Y;

input wire R;

input wire S; input wire[:] din_A; output wire[:] dout; //****************************************

// Variables

//****************************************

reg[:] dout_reg; //****************************************

// Behaviour

//**************************************** assign dout = dout_reg; always@(posedge clk)begin

if(!rst_n)begin

dout_reg <= 'b0;

end

else begin

if('b1 == X)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == Y)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == R)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

if('b1 == S)begin

dout_reg <= din_A;

end

else begin

dout_reg <= dout_reg;

end

end

end endmodule

显然,只有S条件有效了。

结论:顺序块begin::end中的语句是顺序执行的。

Verilog的非阻塞语句放到顺序块中,综合出来怎样的逻辑电路?的更多相关文章

- verilog中阻塞复制,非阻塞复制,顺序块,并行块之间的关系

这几个概念是不一样的 顺序块:顺序块中的语句是按顺序执行的,每条语句中的延迟值是与其前一条语句执行的仿真时间有关. 并行块:并行块语句是并行执行的,它里面的每条语句中指定的延迟值都是相对于语句块开始执 ...

- Verilog HDL中阻塞语句和非阻塞语句的区别

在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“<=”).正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要. Verilog语言中讲的阻塞赋值与非 ...

- Verilog-FPGA硬件电路设计之一——if语句优先级(always块中的阻塞赋值生成的组合逻辑电路是按照顺利执行的)

出处:http://bbs.ednchina.com/BLOG_ARTICLE_3013262.HTM 综合软件:Quartus II 一.有优先级的if语句 if..else if.. else i ...

- Verilog中的阻塞与非阻塞

这篇文档值得阅读 按说阻塞与非阻塞是Verilog中最基本的东西,也是老生常谈.但是最近看到很多程序里用到阻塞语句竟然不是很明白,说到底是从来没有自己仔细分析过.当然一般情况程序中也是推荐用非阻塞的. ...

- Verilog之阻塞赋值非阻塞赋值

verilog设计进阶 时间:2014年5月6日星期二 主要收获: 1. 阻塞赋值与非阻塞赋值: 2. 代码测试: 3. 组合逻辑电路和时序逻辑电路. 阻塞赋值与非阻塞赋值: 1. 阻塞赋值" ...

- 07-阻塞赋值与非阻塞赋值原理分析——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:掌握阻塞赋值与非阻塞赋值的区别 实验平台:无 实验原理: 阻塞赋值,操作符为"=","阻塞"是指在进程语句( ...

- 用Java实现非阻塞通信

用ServerSocket和Socket来编写服务器程序和客户程序,是Java网络编程的最基本的方式.这些服务器程序或客户程序在运行过程中常常会阻塞.例如当一个线程执行ServerSocket的acc ...

- 非阻塞同步算法与CAS(Compare and Swap)无锁算法

锁(lock)的代价 锁是用来做并发最简单的方式,当然其代价也是最高的.内核态的锁的时候需要操作系统进行一次上下文切换,加锁.释放锁会导致比较多的上下文切换和调度延时,等待锁的线程会被挂起直至锁释放. ...

- 【Java并发编程】9、非阻塞同步算法与CAS(Compare and Swap)无锁算法

转自:http://www.cnblogs.com/Mainz/p/3546347.html?utm_source=tuicool&utm_medium=referral 锁(lock)的代价 ...

随机推荐

- 实时监听 mysql 操作,Linux 版

效果 场景:某数据库新增了某条记录,服务器可以监听到变化的数据与操作,如 增加一条记录: id = 1009,name=''test,number = 11 服务器监听结果: 实现过程 测试过程:数据 ...

- Educational Codeforces Round 79 (Rated for Div. 2) - D. Santa's Bot(数论)

题意:有$n$个孩子,第$i$个孩子有$k[i]$件想要的礼物,第$j$个礼物为$a[i][j]$,现在随机挑一个孩子,从他想要的礼物里面随机挑一个,然后送给另一个孩子$($这个孩子可以和第一个孩子是 ...

- onclick="this.src=this.src+'?'"是什么意思?

onclick="this.src=this.src+'?'" 这是表示当前图片链接 在当前链接值的基础上添加了一个问号 譬如当前src="check.aspx" ...

- Linux 命令中 find 和 xargs 命令的用法

find 命令(一) find 命令主要作用是沿着文件层次结构向下遍历,匹配符合条件的文件,并执行相应的操作.Linux 下 find 命令提供了相当多的查找条件,功能很强大,对应的学习难度也比较大. ...

- MyBatis 入门Demo

新建数据库my_db,新建表student_tb id为主键,不自动递增. 不必插入数据. 下载MyBatis https://github.com/mybatis/mybatis-3/release ...

- JavaScript - 包装类型

1. 概念 基本类型是没有方法的 包装类型作用是为了方便操作基本数据类型 // 下面代码的问题? // s1是基本类型,基本类型是没有方法的 var s1 = 'zhangsan'; var s2 = ...

- Unity的3种消息传递方法(SendMessage等)

为了方便多个物体间的消息传达与接收,Unity中包含了几种消息推送机制 : 分别为SendMessage.SendMessageUpwards.BroadcastMessage. 我们首先以SendM ...

- 吴裕雄--天生自然PYTHON爬虫:使用Scrapy抓取股票行情

Scrapy框架它能够帮助提升爬虫的效率,从而更好地实现爬虫.Scrapy是一个为了抓取网页数据.提取结构性数据而编写的应用框架,该框架是封装的,包含request异步调度和处理.下载器(多线程的Do ...

- 穿越雷区--蓝桥杯--DFS/BFS

题目描述 X星的坦克战车很奇怪,它必须交替地穿越正能量辐射区和负能量辐射区才能保持正常运转,否则将报废. 某坦克需要从A区到B区去(A,B区本身是安全区,没有正能量或负能量特征),怎样走才能路径最短? ...

- CODE 大全网站整站源码分享(带数据库)

CODE 大全是一个偏向于 JavaEE.JavaWeb,WEB 前端,HTML5,数据库,系统运维,编程技术开发的纯个人学习.交流性质的技术博客,一个很不错的网站,现在我免费分享给大家.对 java ...